本設(shè)計方案旨在利用上述 的有利條件,提出一套基于TMS320C6x11系列DSP的圖像獲取方案,利用模擬視頻信號的統(tǒng)一性,實現(xiàn)隨意更換帶有標準模擬視頻信號輸出接口的圖像設(shè)備而無需在圖像處理系統(tǒng)的硬件和軟件上作修改。同時,本方案還需提供一個相對通用的數(shù)字視頻接口,可以適應TMS320C6xll系列DSP的接口。本設(shè)計的主要技術(shù)要求有:

①支持標準的模擬視頻輸入接口,可以對標準的模擬視頻信號解碼得到數(shù)字圖像數(shù)據(jù);

②在不降低圖像幅面的前提下,圖像采集速度快,滿足一定的實時性要求;

③占用CPU時間少,使得圖像采集過程在后臺自主完成;

④數(shù)字圖像接口通用性好,可以在TMS320C6u1l系列乎臺上通用互換。

1 總體方案設(shè)計

1.1 方案的選擇

目前,解碼模擬視頻信號主要的方法有:采用A/D采樣模擬視頻信號和采用專用的模擬視頻信號解碼器。對于前一種方案需要的外部芯片較少,只需A/D轉(zhuǎn)換芯片即可;但是需要占用大量的CPU時間,在采集圖像的過程中CPU基本沒有額外的時間處理圖像。這個問題通常會導致圖像處理系統(tǒng)處理圖像的時間嚴重不足。后一種方案采用專門的模擬視頻信號解碼器,需要一些額外的接口芯片,但是可以節(jié)約大量的CPU時間,圖像采集過程可以全部在后臺完成,基本上不需要CPU的干預。這個優(yōu)點對于圖像處理系統(tǒng),特別是算法比較復雜的處理系統(tǒng)(例如視頻監(jiān)控系統(tǒng))有著非常大的吸引力,所以本方案決定采用后者。

本方案中一個難點是:由模擬視頻信號解碼得出的數(shù)字視頻信號數(shù)據(jù)量非常大,而且由于是實時視頻信號,所以數(shù)據(jù)輸出速率也非常高;但是相反,DSP外部存儲器接口的讀出速率卻比較慢。為了解決這個問題,本方案采取了兩種緩沖方式.首先是使用高速FIFO,對數(shù)據(jù)進行暫存以緩解速度上的差異,但是這樣的緩沖還不足以平衡兩者之間的速度差異。

于是在本方案中提出了“隔行采樣”的思想。通常,隔行采樣會使得分辨率下降,例如每四行采樣一行數(shù)據(jù),會使得圖像垂直方向上的行數(shù)下降到原來的1/4。這不是設(shè)計所希望的,所以為了保證圖像的分辨率,設(shè)計中在隔行采樣的同時,將一整幅圖像的行數(shù)據(jù)交錯分多次采樣,然后再重新組合成一幅完整的圖像。這樣既起到了緩沖速度差異的作用,又保證了圖像的分辨率。

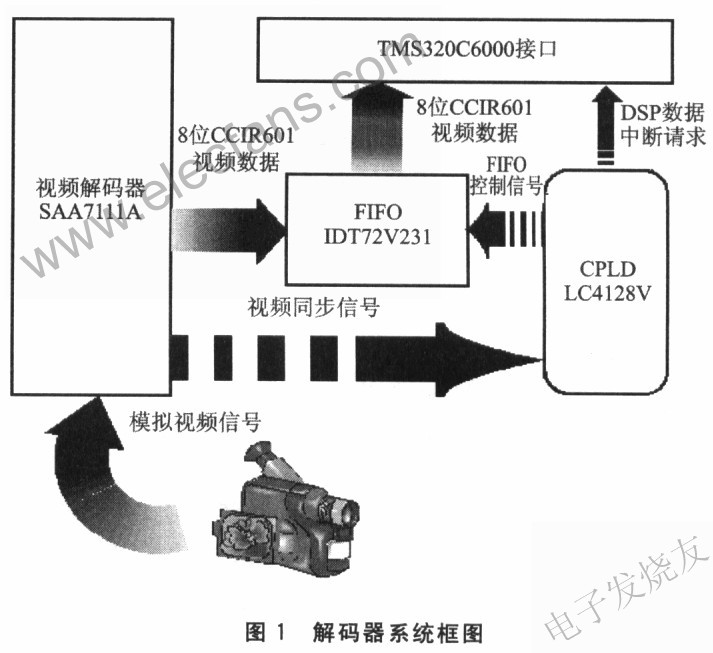

最后本方案確定的思路是,采用FIFO來暫存一行圖像數(shù)據(jù),視頻解碼器直接向FIF0中寫入圖像數(shù)據(jù)。當FIFO中寫入了有效圖像數(shù)據(jù)后,由CPLD向DSP發(fā)出中斷請求;同時,DSP接到中斷請求后,啟動DMA方式將一行圖像數(shù)據(jù)從FIFO中讀入到其外部RAM中存放。CPLD主要完成“隔行采樣”的實現(xiàn)、控制解碼器向FIFO中寫入數(shù)據(jù)以及DSF從FIFO中讀出數(shù)據(jù)。

另外,本方案目前主要是針對PAL制式模擬信號的。PAL制模擬信號傳輸?shù)膱D像幅面大小為720×576像素。下面的設(shè)計主要針對該格式的視頻信號展開。如果需要對NSTC等其他制式視頻信號解碼,只需要在軟件上作一些修改即可。

1.2 系統(tǒng)框圖

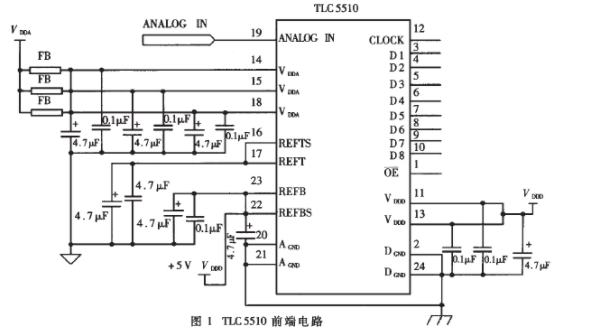

在本方案中,模擬視頻信號解碼器采用的是Philips公司的SAA7111A。對于PAL制式模擬視頻信號,l行圖像數(shù)據(jù)有720個像素;同時由于YUV分量采用了4:2:2抽樣,所以需要1440字節(jié)的存儲空間存儲1行數(shù)據(jù)。由于本方案中需要用到FIFO對1行數(shù)據(jù)暫存,所以FIFO的存儲深度必須大于1440字節(jié),最后選定高速FIFO采用IDT公司的IDT72V23l,其具有2K×9位的存儲深度。同時還使用了Laittice公司的CPLD——LC4128V,作為中間邏輯接口控制“隔行采樣”的完成、解碼器對FIFO的寫操作以及DSP對FIFO的讀操作,系統(tǒng)框圖如圖l所示。

2 硬件方案設(shè)計

2.1 芯片介紹

本方案選用SAA7111A作為前端視頻解碼器。SAA71llA視頻解碼器是雙通道模擬預處理電路、自動鉗位和增益控制電路、時鐘產(chǎn)生電路、數(shù)字多標準解碼器、亮度/對比度/飽和度控制電路、彩色空間矩陣的組合,是一款功能完善的視頻處理器。SAA711lA只需要單一的3.3V電源供電,與C6x11的I/O電壓一 致。SAA7111A接收CVBS(復合視頻)或S-video模擬視頻輸入,可以將PAL、SECAM、NTSC模式的彩色視頻信號解碼為CCIR-60l/656兼容的彩色數(shù)字分量值,器件功能通過I2C接口控制。

SAA7111A的主要性能特點如下:

◆4路模擬輸入一一4路CVBS或2路Y/C或1路Y/C和2路CVBS;

◆主通道靜態(tài)增益可編程,自動增益控制選擇的CVBS或Y/C通道;

◆2個8位視頻CMOS模數(shù)轉(zhuǎn)換器;

◆片上時鐘產(chǎn)生器,只需要24.576 MHz單一時鐘輸入;

◆自動探測50 Hz和60 Hz場頻,自動在PAL和NTSC標準間切換;

◆可以處理PALBGHI、PALN、PAL M、NTSC M、NTSC N、NTSC 4.43、NTSC-Japan和SECAM信號。從以上特點可以看出,SAA7111A功能強大,性能全面,可以滿足各種視頻轉(zhuǎn)換處理的需要,完全符合本系統(tǒng)的要求。SAA7111A已經(jīng)在各種視頻處理系統(tǒng)中得到廣泛的應用,技術(shù)性能已得到充分的證明。采用SAA7111A具有很高的性價比。

2.2 DSP與FOFO接口技術(shù)

TMS320C6xll的外部存儲器接口(EMIF)提供了功能十分強大的外部接口,可以實現(xiàn)與諸多種類的存儲器的無縫接口,如SBSRAM、SDRAM、SRAM、ROM等等。但是其對FIFO的接口并不能做到真正的無縫接口,需要增加一些外部邏輯來調(diào)整它們之間的時序。

本方案中采用的FIFO一一IDT72V23,是標準的同步FIFO,具有兩個獨立的讀寫時鐘——RCLK、WCLK;同時還具有讀寫控制信號WENl、WEN2、REN1和REN2。

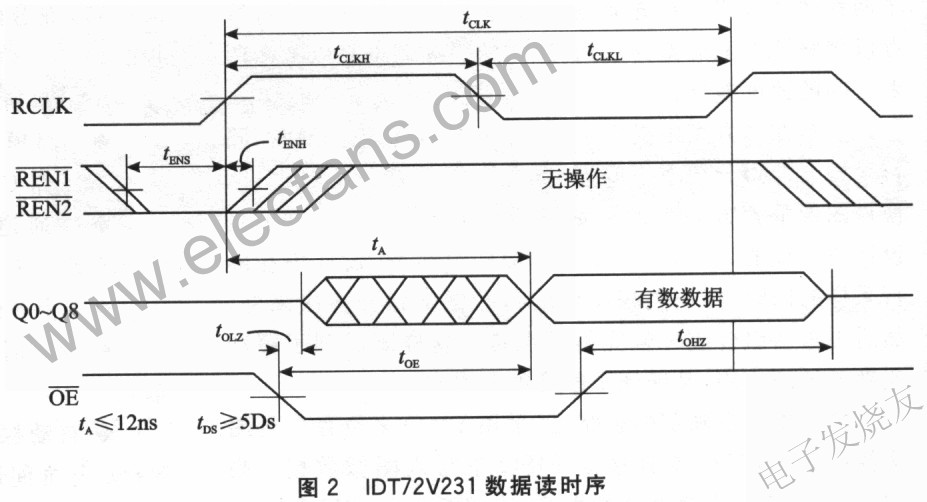

對于本設(shè)計而言,要求DSP從FIFO中將數(shù)據(jù)讀出,故關(guān)鍵考慮DSP對IDT72V23l的讀時序。圖2是IDT72V31數(shù)據(jù)讀出的時序。

圖2中,tENS為REN1(REN2)的最短建立時間(SETUP),tDS為數(shù)據(jù)的最短建立時間(SETUP)。由圖2可以看出IDT72V231與一般SRAM讀時序的一個很大區(qū)別是:當RCLK上升沿到來以后,需要有一個比較長的延時tA才會有有效數(shù)據(jù)出現(xiàn)在總線上。此前一段時間內(nèi)總線上的數(shù)據(jù)是不穩(wěn)定的,并且該延時最長可達到12ns。

但是對于TMS320C6x11而言,數(shù)據(jù)的讀入是在ARE信號的上升沿完成的,故這里設(shè)計的主要問題是FIFO的RCLK時鐘怎樣提供。本設(shè)計中采用的解決辦法如下:

RCLK=!(ARE)

REN1&REN2=CEx+AOE+Address

也就是說,RCLK是由DSP的ARE信號取反得到的,而REN1和REN2信號是由DSP的AOE信號經(jīng)過地址譯碼后提供。這樣設(shè)計的TMS320C6xll與FIFO接口為了配合FIFO讀出時序的要求,還必須要求DSP的讀時序(主要是Setup/Strobe/Hold三個時序段)滿足以下要求:

Setup≥(tENS+tSKEW)/tcyc

Strobe≥(tA+tDS)/tcyc

Strobe≥(tCLKH(min)/tcyc

Hold+Setup≥(tCLKL(min)/tcyc

Setup+Strobe+Setup≥(trc(min)/tcyc

從時序圖上的數(shù)據(jù)可以看出,tENS≥5ns,tA≤12 ns,tDS≥5 ns;同時,由于IDT72V23l的要求,RCLK高電平時間(tCLKH(min)大于等于8ns、RCLK低電平時間(tCLKL(min)大于等于8 ns以及讀寫周期(trc(min)必須大于等于20ns。加上一定的冗余,最后計算可以得到:

Setup≥20ns

Strobe≥30 ns

Hold≥l0ns

在本設(shè)計的TMS320C6211的系統(tǒng)板上,EMIF的外部時鐘頻率是100 MHz,所以tcyc=10ns。這樣可以得出DSP中CExCTL寄存器中Setup值設(shè)置為2,Strobe值設(shè)置為3,Hold值設(shè)置為1。

實際系統(tǒng)實現(xiàn)證明。通過這樣的硬件接口設(shè)計后,TMS320C621l可以很穩(wěn)定地從FIF0中讀出數(shù)據(jù)。

2.3 隔行采樣技術(shù)

由于DSP接口與FIFO的接口速度只能達到15MB/s的速度,同時當DSP把圖像數(shù)據(jù)從FIFO中讀出來以后還需要將數(shù)據(jù)存入其外部存儲器中,這樣DSP與FIFO的接口速度是完全不可能跟上解碼器SAA7111A的有效數(shù)據(jù)輸出速度(最低19.8 MB/s)的,所以DSP無法實時地從視頻流中抓出一幅完整的圖像。 因此,在DSP與SAA711lA的接口之間采用高速FIFO進行緩沖的同時,還采取了“隔行采樣”的方法來緩沖速度上的差異。通過計算得出DSP每隔4行有效視頻信號采1行視頻數(shù)據(jù)是合理的。(把DSP將獲取的數(shù)據(jù)存人其外部存儲器中所需要的時間考慮在內(nèi)。)

“隔行采樣”的結(jié)果會導致所獲取的圖像垂直分辨率下降(對于PAL制式視頻信號由原來的576行/幅下降到144行/幅)。為了保證圖像的分辨率,本設(shè)計中將每幅圖像分成連續(xù)的4次采樣.在連續(xù)的4次采樣中,分別抓取圖像中不同的144行數(shù)據(jù),也就是說,現(xiàn)在DSP抓取1幅完整幅面(720×576)大小的圖像需要分4次獲取,然后對數(shù)據(jù)重排組合得到完整的圖像。PAL制信號是按照50Hz的場頻對圖像進行輸出的,即每秒種可以傳輸25幅圖像,現(xiàn)在由于“隔行采樣”的原因,DSP每秒鐘可以從PAL制信號中解碼出6.25幅完整幅面大小的圖像。這個速度完全可以滿足很多實時系統(tǒng)的要求,如視頻監(jiān)控系統(tǒng)。

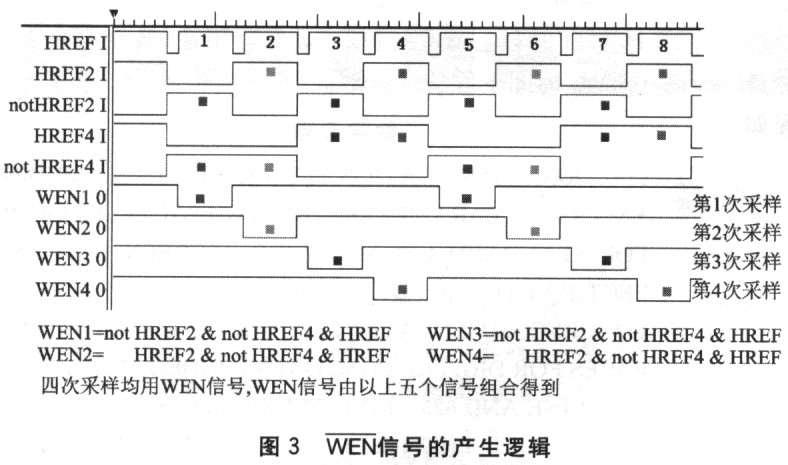

“隔行采樣”功能的具體實現(xiàn)是由CPLD配合SAA7111A輸出的同步信號(行同步、場同步信號)來完成的。由于IDT72V231(FIFO)的寫入控制是通過WEN信號完成的,因此CPLD可以通過控制WEN信號來實現(xiàn)圖像的隔四行一采樣。具體WEN信號的產(chǎn)生邏輯如圖3所示。

由圖3可以清晰地看出,通過這種采樣方式以后,每次輸出的圖像行是隔4行輸出l行,而連續(xù)4次獲取的圖像則是一整幅圖像576行圖像數(shù)據(jù)中互不相同的144行數(shù)據(jù),這四部分圖像按照一定規(guī)律組合便可以得到一幅幅面為720×576像素的完整數(shù)宇圖像。

另外由圖3可以看出,SAA7111A每向FIFO中寫入一行圖像數(shù)據(jù)(需要53.3μs),DSP則有相當于4行圖像數(shù)據(jù)輸出的時間(約256μs)來讀出這一行圖像數(shù)據(jù)。因此“隔行采樣”有效地緩沖了數(shù)據(jù)輸出和數(shù)據(jù)讀入速度上的差距。

3 軟件方案設(shè)計

解碼器DSP方軟件的設(shè)計主要分成兩個部分:①將圖像數(shù)據(jù)從FIFO中讀出來存人到DSP的外部RAM中去;②對讀出的數(shù)據(jù)進行重排,組合成完整的圖像。下面分成兩部分來說明。

3.1 QDMA方式數(shù)據(jù)的讀入

由于DSP將數(shù)據(jù)從外部讀人到RAM中通常是圖像處理系統(tǒng)的一個圖像獲取過程,所以如果使CPU一直處于讀入數(shù)據(jù)的操作中,顯然是不合理的。

為了保證盡可能少地占用CPU時間,即在第n幅圖像讀入到RAM中的同時,DSP仍然可以有足夠的時間來處理第n-1幅圖像(對其做需要的處理,例如去噪、壓縮、識別等等)。本設(shè)計中采取了下面這種讀出方式:視頻解碼器通過一個中斷信號通知DSP目前已有數(shù)據(jù)寫入到FIFO中,然后DSP在中斷中采用DMA方式,將數(shù)據(jù)從FIFO中成塊地搬移到RAM中去。

這種操作的好處是顯而易見的:當DSP正在處理某一幀圖像時,如果有數(shù)據(jù)需要讀入,那么DSP將進入中斷,然后僅僅只需要開啟DMA讀出操作便可退出中斷服務(wù)于程序,繼續(xù)沒有處理完的工作;而DMA控制器則在后臺將一塊區(qū)域連續(xù)的圖像數(shù)據(jù)讀入到RAM中。這樣圖像的獲取可以實規(guī)在后臺完成,圖像的處理和圖像的獲取很好地并行進行,大大提高了CPU的利用率。

具體在本方案中,由于使用的FIFO的深度是2 K×9位,所以采取的是DMA每次搬移一行圖像數(shù)據(jù)(也就是720×2=1440字節(jié))到RAM中去。同時,TMS320C6x11提供了 十分強大的EDMA功能。為了加快DSP在中斷中開啟DMA讀出操作的速度,本設(shè)計采用了其QDMA的功能.這樣申請一次QDMA僅僅需要幾條指令即可。具體申請QDMA的操作代碼如下:

QSRC="SourceAddress",

//設(shè)置FIFO在系統(tǒng)中的地址

QCNT="0x000005A0";

//設(shè)置一次需要讀出的數(shù)據(jù)量

//(1440)

QDST=(int)DesAddress; //設(shè)置數(shù)據(jù)讀出的目的地址

QIDX="0x00000001"; //設(shè)置QDMA傳送的間距

DesAddress="DesAddress"+0x5A0;

//更新數(shù)據(jù)讀出目的地址

QSOPT="0x30300000"; //啟動QDMA通道傳輸

3.2 圖像數(shù)據(jù)的重排

由于本方案中采用了隔四行一采樣的方法來平衡速度上的差異,所以最后載人RAM中的數(shù)據(jù)需要重排。這個重排可以在讀入FIFO中的數(shù)據(jù)時就進行,也可以在所有數(shù)據(jù)全部讀人到RAM中后再進行重排;但是重排的方案和流程是一樣的。

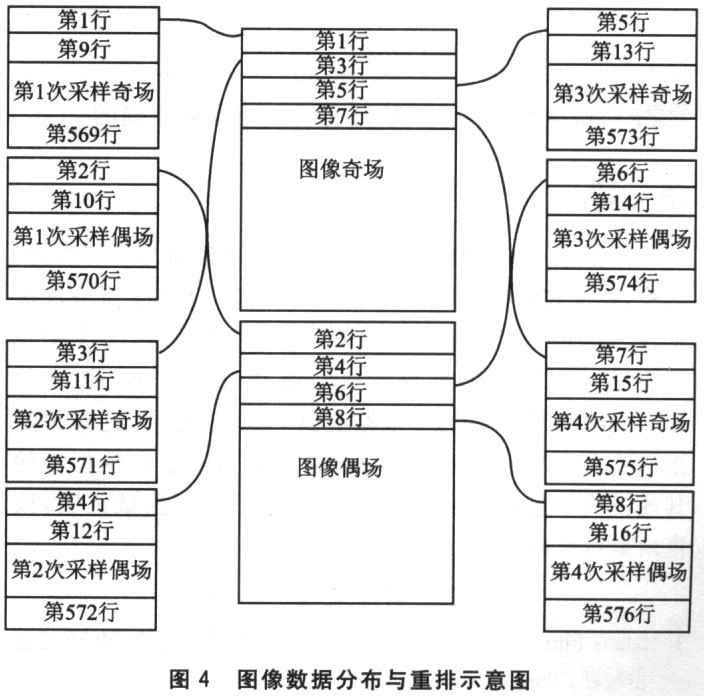

如果是采用全部數(shù)據(jù)都讀完后再重排,由于隔四行采樣的原因,圖像數(shù)據(jù)是分四個連續(xù)的數(shù)據(jù)塊存放的,并且每個數(shù)據(jù)塊中是按照奇偶場分布的。那么,以第一個數(shù)據(jù)塊為例,它的奇場部分存儲的實際上是圖像的第1,9,17,…,561,569行數(shù)據(jù);而其偶場部分存儲的實際上是圖像的第2,10,18,…,562,570行數(shù)據(jù)。另外,三個數(shù)據(jù)塊里面存儲的圖像數(shù)據(jù)在整幅圖像中的行數(shù)分布依此類推。具體分布和重排過程如圖4所示。

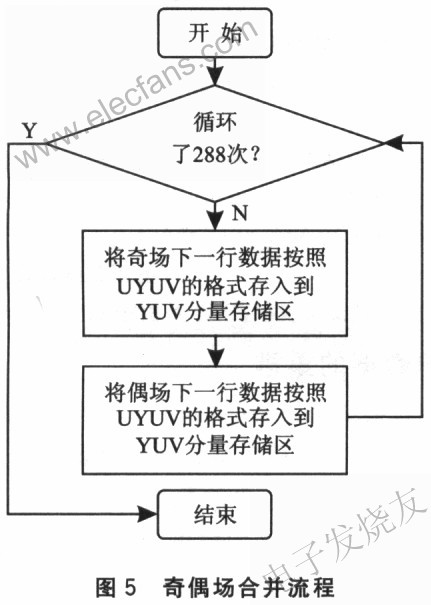

通過圖4所示方式的重排處理以后,全部圖像數(shù)據(jù)分成了兩大塊:奇場區(qū)和偶場區(qū)。這時可以根據(jù)需要來處理這兩個區(qū)域。本設(shè)計中采用的是將奇偶場合并,同時將YUV分量分開到三個獨立的存儲區(qū)域中去,程序流程如圖5所示。

4 總結(jié)及展望

本文提出了一種基于TMS320C6xll接口的圖像獲取方案。它利用目前大多數(shù)成熟的圖像獲取設(shè)備都配備了通用的模擬視頻輸出接口這一特點,提出了一個從模擬編碼的視頻信號中抓出靜止的數(shù)字圖像的方案。由于其數(shù)字部分接口非常通用(8位),使得可以很容易地在通用圖像處理系統(tǒng)中加入實時圖像獲取接口。通過具體實現(xiàn)證明此方案可行、穩(wěn)定、高效;可以實現(xiàn)每秒鐘6.25幅720×576幅面的彩色圖像的獲取,具有通用性好、性能穩(wěn)定、占用CPU時間少等特點。防碰撞模塊對SELECT命令的響應是正確的。

5 結(jié) 語

A型卡RFID技術(shù)已經(jīng)廣泛應用于智能卡、票物、安檢、物流和防偽等領(lǐng)域。本文根據(jù)RFID防碰撞協(xié)議規(guī)定,在數(shù)字硬件上實現(xiàn)了A型卡的防碰撞模塊,用VHDL語言進行了仿真和綜合后,通過了Xilinx公司的XC4010XLFPGA驗證,電路規(guī)模5000門左右,達到預定指標要求。最后,采用O.35μm的工藝與電子防偽標簽的其他模塊一起進行了MPW流片,實際應用測試證明,該模塊運行正確、穩(wěn)定。

電子發(fā)燒友App

電子發(fā)燒友App

評論