1 前言

DM642 (TMS320DM642)型處理器是TI最新推出的面向多媒體處理領域的數字信號處理器(DSP).給多媒體設備的實現提供了另一種有效的手段。 DM642建立在C64x DSP核基礎上.采用德州儀器公司開發的第二代高性能的先進的超長指令字結構VeloeiTl.2TM,在600MHz的時鐘頻率下.DM642每秒可以進行24億次16位的乘累加或48億次的8位的乘累加。這樣強大的運算能力使得DM642可以進行實時多視頻圖像處理。它的增強型直接內存存取 (EDMA)對DSP圖像處理系統是非常重要的,它可以在沒有CPU參與的情況下完成映射存儲空間中數據搬移。靈活使用EDMA可以大大提高數據傳輸效率。以:DM642為例,結合Sobel算法給出EDMA的一種具體控制和實現方法。

2 DM642的EDMA控制器

DM042的EMDA能提供超過2Gb/s的外部帶寬.支持64路獨立觸發的事件傳輸,總共有85個參數對“Linking”或“Chaining”進行配置。Linking是在1個事件被觸發時允許1個序列進行傳輸。Chaining是當1個通道的數據傳輸完畢時觸發另1個通道的數據傳輸。 Linking和Chaining使得僅僅被CPU初始配置之后EDMA能夠連續的自動運行。EDMA的特點決定了其適合圖像處理的功能。由于圖像處理的原始數據量很大.同時圖像處理中也會產生同等量的中間數據.對于片內存儲資源有限的高速DSP來說,一般需要借用外部存儲空間。為了提高系統的實時處理能力.可以將數據在不同存儲空間轉移的任務交給EDMA來完成,而CPU只用于數據的計算。同時,EDMA對數據重排功能可以優化圖像數據在內存中的存儲,這不僅可以提高內部存儲空間的利用效率.而且可以提高數據的傳輸速率。雖然對圖像數據的傳輸也可由軟件實現,但將消耗大量的CPU時鐘周期。使DSP的高速性能難以發揮。而由EDMA來完成同樣的工作幾乎不占用CPU的時鐘周期。

在C64xDSP中.EDMA控制器負責片內L2存儲器與其他設備之間的數據傳輸。EDMA控制器和DMA在結構上有很大的不同.其增強之處包括:

提供了64個通道;

通道間的優先級可以設置;

支持不同結構數據傳輸的鏈接。

EDMA控制器由以下幾部分組成;

事件和中斷處理寄存器;

事件編碼器;

參數RAM;

硬件地址產生。

其中,事件寄存器控制對EDMA事件進行捕獲。1個事件相當于1個同步信號,由它觸發1個EDMA通道開始數據傳輸。如果有多個事件同時發生.則由事件編碼器對它進行分辨。EDMA的參數RAM中存放了有關的傳輸參數,這些參數會被送入地址發生器硬件.進而產生讀寫操作所需要的地址。

EDMA支持8bit、16bit和32bit數據的存儲。在EDMA中定義了下列概念:

(1) 數據單元(element)的傳輸。單個數據單元從源地址向目的地址傳輸.如果需要,每1個數據單元都可以由同步事件觸發傳輸;

(2) 幀(frame)。l組數據單元組成1幀,l幀中的數據單元可以是相鄰連續存放的,也可以是間隔存放的.幀傳輸可以選擇是否受同步事件控制,“幀” 一般在1維傳輸中提及;

(3) 陣列(array)。1組連續的數據單元組成1個陣列.在1個陣列中的數據單元不允許間隔存放。1個陣列的傳輸可以選擇是否受同步事件控制。“陣列 ”一般在2維傳輸中提及;

(4) 塊(block)。多個幀或者多個陣列的數據組成1個數據塊;

(5) 1維(1一D)傳輸。多個數據幀組成1個1維的數據傳輸。Block中幀的個數可以是 l~65536。

(6) 2維(2一D)傳輸。多個數據陣列組成1個2維的數據傳輸。第1維是陣列中的數據單元,第2維是陣列的個數。

3 EDMA的控制機制

3.1 事件與事件控制寄存器

EDMA有64個通道.每1個通道都有1個事件與之關聯.由這些事件觸發相應通道的傳輸。

3.2 傳輸參數與參數 RAM

EDMA控制器與DMA控制器在結構上有所區別。C64x的.EDMA控制器是基于RAM結構。參數.RAM(Parameter RAM。PaRAM)的容量是2KB,總共可以存放85組EDMA傳輸控制參數。多組參數還可以彼此連接起來,從而實現某些負責數據流的傳輸.例如循環緩存和數據排序等。參數RAM中保存的內容包括:

64個EDMA通道對應的入口傳輸參數.每組參數包括6個字;

用于重加載,鏈接的傳輸參數組。每組參數包括24字節;

8字節空余的RAM可以作為“草稿區”(scratch pad area)。

一旦捕獲到某個事件.控制器將從PaRAM頂部的64組入口參數中讀取數據對應的控制參數送往地址發生器硬件。

表l給出1組EDMA傳輸參數的內部結構,總共6個字.192bit。可以通過32bit的外設總線對EDMA的參數.RAM進行訪問。

可選參數(Option Parameter),32bit,用戶可以根據情況選擇設置該參數。

SRC/DST地址.32bit,用于存放EDMA訪問起始的源地址和目的地址,可以通過可選參數中的SUM/DUM位設定對SRC/DST地址的修改方式。

數據單元計數(Element Count),16bit無符號數.存放l幀(1一D傳輸)或1個陣列(2一D傳輸)中的數據單元數。

幀/陣列計數(Frame/Array Count),16bit無符號數.存放的是1-D數據傳輸中的幀計數,或是2一D數據傳輸中的陣列計數。

數據單元,幀,陣列索引(Element/Frame/ArrayIndex).16bit無符號數,作為地址修改的索引值。數據單元索引只應用于1-D 傳輸,為下一數據單元的地址偏移值(2一D傳輸不允許數據單元間隔存放)。幀,陣列索引用于控制下一幀,陣列的地址索引。

數據計數的重加載(Element Count Reload),16bit無符號數。用于在每幀最后一個數據元素傳輸之后.重新加載傳輸計數值。這個參數只能用于1一D傳輸中。

鏈接地址(Link Address),16bit。當設定可選參數中的LINK=1時,可以由鏈接地址確定下1個EDMA事件采用參數的裝載,重裝載地址,從而使多組 EDMA傳輸參數形成EDMA傳輸鏈。

4 EDMA的傳輸操作

EDMA進行數據傳輸時有2種啟動方式,1種是CPU啟動.另1種是由同步事件觸發。每1個通道的啟動是相互獨立的。

4.1 CPU啟動EDMA/非同步的 EDMA

CPU可以通過寫事件置位寄存器(ESR)啟動1個EDMA通道。向ESR中某1位寫1時,將強行觸發對應的事件。此時,與正常的事件響應過程類似, EDMA的PaRAM中的傳輸參數被送入地址發生器.完成對EMIF、L2存儲器或外設的存取訪問。由CPU啟動的EDMA屬于非同步的數據傳輸。EER 中的事件使能與否不會影響這種EDMA傳輸的啟動。

4.2 由事件觸發 EDMA

一旦事件編碼器捕獲到1個觸發事件并鎖存在ER寄存器中,將導致PaRAM中對應的參數被送入地址發生器.進而執行有關的傳輸操作。盡管是由事件啟動傳輸操作,但是事件本身必須首先被CPU使能。EER寄存器負責控制事件的使能。觸發EDMA傳輸的同步事件可以源于外設,外部器件的中斷或某個EDMA通道結束。與DMA的情況不同,與EDMA的每1個通道相關聯的觸發事件是固定的。因此,如果假設EER中的EVT4=1,那么EXT_INT4引腳的外部中斷信號就會啟動EDMA通道4的傳輸。所以,每個事件也就指定了1個特定的EDMA通道。

5 在實時圖像處理系統中的應用

在實時圖形處理系統中,經常是把數據塊轉移,例如從視頻通道采集數據傳送到SDRAM中作為后續處理的緩存,或是把數據傳送到片內RAM中。EDMA使數據的傳送簡單易行。下面以把數據從視頻通道傳送到片內RAM中并作Sobel邊緣提取算法和把數據從視頻通道傳送到SDRAM中并作So—bel邊緣提取算法為例。

(1)把數據從視頻通道通過1維方式傳送到片內RAM中并作Sobel邊緣提取算法

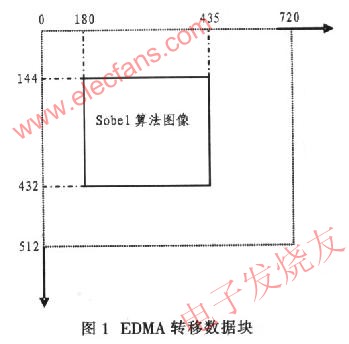

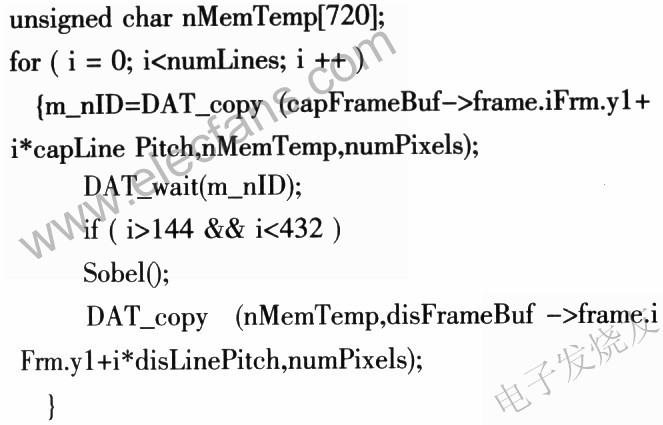

只對攝像頭采集的I塊數據進行Sobel邊緣提取。采用一維EDMA傳送方式,每1次傳送采集1行中的部分數據(DAT_copy()函數)。在PAL制式下.先把1行數據放到nMemTemp數組中,然后對從144行到432行、從180列到435列的圖像進行Sobel邊緣提取.最后把變換后的數據輸出到顯示緩沖區.如圖1所示。

因為Sobel算法需要3行數據,所以可以開辟1個可以存放3行數據的緩沖區,通過指針的交換把從視頻通道過來的數據分別放到緩沖區中。保存的3行圖像使用翻卷的緩沖區管理,3個變量分別指示當前使用的y行、y—l行和y一2行在緩沖區中的起始偏移量。可以這樣:輪流往3塊緩存區拷貝數據.只要改變拷貝的指針就可以。在拷貝當前這1塊的時候.已經拷貝的另外2塊數據依然沒有變化,所以就可以實現3塊數據保存采集圖像中的相鄰3行數據.如表2所示。

(2)把數據從視頻通道通過2維方式傳送到SDRAM中并作Sobel邊緣提取算法可以通過DAT_copy2d 0函數直接把采集的l幅圖像亮度分量存放到SDRAM中,如下:

其中.m_dbFrameBufferTemp是指向SDRAM中緩沖區的指針,numPixels是1行的像素數,num-Lines是行數。當把數據存放到SDRAM的1個數組中后.Sobel算法的實現就非常簡單了。當然也可以參照1維的方法來實現。

6 結束語

大批量的圖像數據傳輸和復雜算法的處理一直是高速數字圖像處理器的速度瓶頸,利用DSP的EDMA功能可以在不中斷信號處理器算法處理工作的同時完成圖像數據的搬移,在有效地解決了大批量圖像數據傳輸速度瓶頸的同時,又能讓DSP的處理器核專門從事算法處理工作,極大地提高了系統的并行性能。

電子發燒友App

電子發燒友App

評論