無線系統(tǒng)及有線系統(tǒng)設(shè)計(jì)師均必須重視電源效率問題,盡管雙方的出發(fā)點(diǎn)不盡相同:對于移動(dòng)設(shè)備而言,更長的電池使用壽命、更長的通話時(shí)間或更長的工作時(shí)間都是明顯的優(yōu)勢,降低電源要求意味著使用體積更小的電池或選擇不同的電池技術(shù),這在一定程度上也緩解了電池發(fā)熱問題;對于有線系統(tǒng)而言,設(shè)計(jì)師可通過減小電源體積、減少冷卻需求以及降低風(fēng)扇噪聲來提高電池效率。人們很少會(huì)提到這樣一個(gè)事實(shí):提高電源效率還可節(jié)省空間,而節(jié)省的空間可以用來增加能夠提高系統(tǒng)性能的組件,尤其是設(shè)計(jì)小組希望添加一個(gè)以上處理器時(shí),這一點(diǎn)非常重要。

設(shè)計(jì)嵌入式DSP處理器或系統(tǒng)功耗要求嚴(yán)格的系統(tǒng)時(shí),采用DSP專用技術(shù)、操作系統(tǒng)及其支持軟件可以降低功耗。超越傳統(tǒng)技術(shù)的DSP或雙處理器設(shè)計(jì)在節(jié)約能量方面表現(xiàn)出色。

功耗基礎(chǔ)知識(shí)

互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)電路的總功耗是動(dòng)態(tài)功耗與靜態(tài)功耗之和:

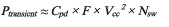

當(dāng)門發(fā)生邏輯狀態(tài)轉(zhuǎn)換并產(chǎn)生內(nèi)部結(jié)點(diǎn)充電所需的開關(guān)電流以及P通道及N通道同時(shí)暫態(tài)開啟引起直通電流時(shí),就會(huì)出現(xiàn)動(dòng)態(tài)功耗。通過以下公式可以估算其近似值:

其中,Cpd為動(dòng)態(tài)電容,F(xiàn)為開關(guān)頻率,Vcc為電源電壓,而Nsw為轉(zhuǎn)換的比特?cái)?shù)。另外,電壓(Vcc)決定著穩(wěn)定工作狀態(tài)下的最大開關(guān)頻率(F)。上述關(guān)系中包含兩個(gè)重要概念:動(dòng)態(tài)功耗與開關(guān)頻率呈線性關(guān)系,與電源電壓呈二次關(guān)系;最大安全開關(guān)頻率取決于電源電壓。為便于本文討論,將特定的頻率及電壓對稱為“設(shè)定點(diǎn)”。

很顯然,降低CPU時(shí)鐘速率將相應(yīng)成比例地降低動(dòng)態(tài)功耗,由于動(dòng)態(tài)功耗與電源電壓成二次關(guān)系,在不影響系統(tǒng)性能的前提下,通過降低電壓就可能大大降低功耗。不過,對于特定任務(wù)集,降低CPU時(shí)鐘速率也會(huì)成比例地延長執(zhí)行該任務(wù)集的時(shí)間,因此必須仔細(xì)分析應(yīng)用以確保滿足其實(shí)時(shí)需求。

靜態(tài)功耗主要是由于晶體管漏電流造成的。一般說來,CMOS電路的靜態(tài)功耗很低,與其動(dòng)態(tài)功耗相比可以忽略不計(jì)。嵌入式應(yīng)用在不工作期間通常會(huì)“閑置”CPU時(shí)鐘以減少動(dòng)態(tài)功耗,從而顯著降低總體功耗。而在未來的設(shè)計(jì)中必須特別關(guān)注靜態(tài)功耗問題,因?yàn)楦咝阅艿男滦途w管的漏電流將顯著提高。

嵌入式系統(tǒng)常用技術(shù)

常用電源管理技術(shù)可以分為兩類:通過早期硬件設(shè)計(jì)決策時(shí)實(shí)現(xiàn),或在系統(tǒng)運(yùn)行時(shí)實(shí)現(xiàn)。設(shè)計(jì)早期的決策對滿足性能及功耗至關(guān)重要,下面列出了設(shè)計(jì)中需要考慮的十大要素,其中包括硬件選擇、設(shè)計(jì)策略及架構(gòu)選擇。大多數(shù)要素都是嵌入式系統(tǒng)的基本要求,其他要素則需要單獨(dú)考慮。盡管下列決策是在設(shè)計(jì)早期制定的,但有些仍需在整個(gè)設(shè)計(jì)周期中進(jìn)行再驗(yàn)證。如下所列:

1. 選擇低功耗組件;

2. 分割電壓與時(shí)鐘域;

3. 支持電壓及頻率調(diào)節(jié)功能;

4. 啟用保持電壓門控功能;

5. 通過軟件利用中斷減少輪詢;

6. 采用分級(jí)存儲(chǔ)器模型;

7. 降低輸出負(fù)載;

8. 系統(tǒng)啟動(dòng)時(shí)關(guān)閉非關(guān)鍵資源供電;

9. 盡量減少活動(dòng)PLL數(shù)量;

10. 使用時(shí)鐘分頻器快速變換頻率。

確定系統(tǒng)架構(gòu)以后,設(shè)計(jì)團(tuán)隊(duì)需要將注意力轉(zhuǎn)向系統(tǒng)運(yùn)行時(shí)環(huán)境。以下列出的14項(xiàng),在設(shè)計(jì)過程中要始終關(guān)注其中大部分內(nèi)容:

1. 不需要時(shí)則關(guān)閉門控時(shí)鐘;

2. 引導(dǎo)過程中主動(dòng)關(guān)閉不必要的功耗;

3. 僅在需要時(shí)用向子系統(tǒng)供電;

4. 激活外設(shè)低功耗模式;

5. 充分利用外設(shè)活動(dòng)狀態(tài)檢測器;

6. 使用自動(dòng)刷新模式;

7. 對應(yīng)用進(jìn)行基準(zhǔn)測試來確定必需的最小頻率及電壓;

8. 根據(jù)總體活動(dòng)情況調(diào)整CPU頻率及電壓;

9. 動(dòng)態(tài)調(diào)節(jié)CPU頻率及電壓以匹配預(yù)計(jì)的工作負(fù)載;

10. 優(yōu)化代碼的執(zhí)行速度;

11. 使用低功耗代碼序列及數(shù)據(jù)模式;

12. 使用代碼覆蓋技術(shù)減少對高速內(nèi)存的需求;

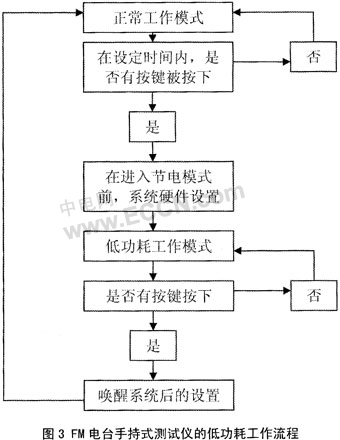

13. 更換電源時(shí)進(jìn)入簡化功能模式;

14. 平衡精確度與功耗的關(guān)系。

有經(jīng)驗(yàn)的設(shè)計(jì)團(tuán)隊(duì)必須至少在概念上熟悉上述嵌入式系統(tǒng)應(yīng)用設(shè)計(jì)要點(diǎn)(其中部分與DSP電路有關(guān))。任何降低功耗的設(shè)計(jì)都有可能對性能產(chǎn)生負(fù)面影響或?qū)е孪到y(tǒng)不穩(wěn)定。

DSP RTOS如何滿足低功耗設(shè)計(jì)要求

一部分最重要的并得到普遍認(rèn)可的技術(shù)方法可以融合到RTOS中,相關(guān)的技術(shù)包括:閑置、關(guān)閉活動(dòng)電源、器件驅(qū)動(dòng)程序通知、內(nèi)存管理、電壓/頻率調(diào)節(jié)。然而,由于設(shè)計(jì)目標(biāo)不盡相同,將這些技術(shù)構(gòu)建到RTOS中并不容易。設(shè)計(jì)師需要在這些方法中做出選擇,設(shè)計(jì)的關(guān)鍵目標(biāo)就是高效性、靈活性以及與操作系統(tǒng)本身的松散關(guān)系。

TI的DSP/BIOS操作系統(tǒng)的電源管理器(PWRM)非常適于用作現(xiàn)有RTOS的電源管理模塊。盡管以下描述的設(shè)計(jì)實(shí)現(xiàn)是針對DSP/BIOS,但其概念可很容易地運(yùn)用到其他操作系統(tǒng),甚至用于無操作系統(tǒng)的應(yīng)用環(huán)境。

電子發(fā)燒友App

電子發(fā)燒友App

評論