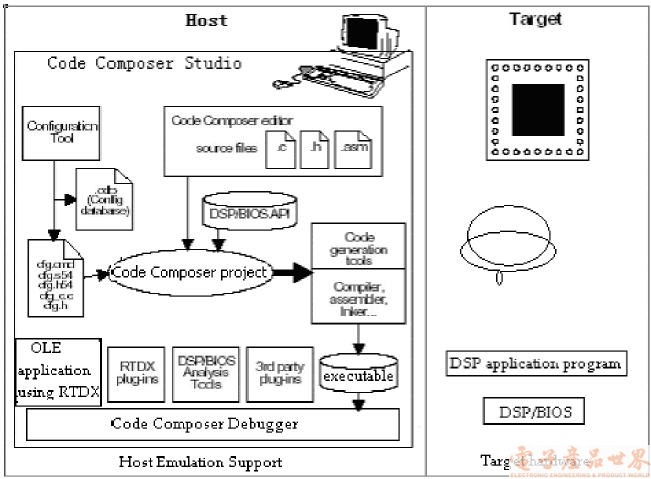

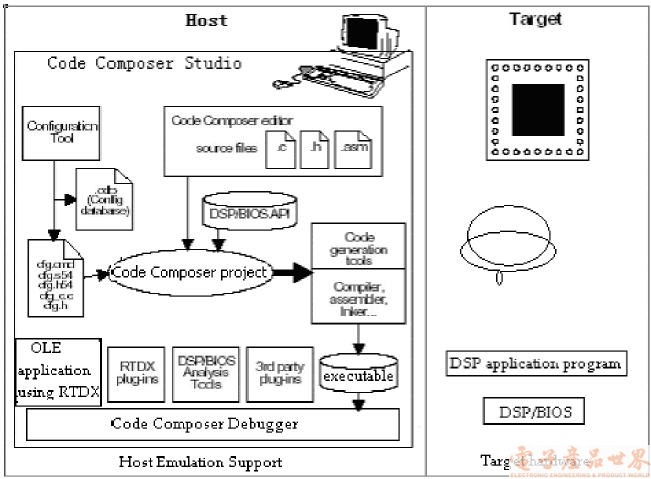

程序,并能提供實時查詢程序運行情況(主要是CPU負(fù)荷,時序,日志以及線程等)。但實際開發(fā)DSP/BIOS應(yīng)用程序時為了真實的了解目標(biāo)板的各種信息,僅有Simulator(軟件仿真器)是不行的,還需要使用Emulator(硬件仿真器)和DSP/BIOS插件(安裝時已裝入)。2.RTDX應(yīng)用程序調(diào)試

2012-06-12 15:11:34

`產(chǎn)品特點基于ZYNQ+并行DSP處理架構(gòu)處理架構(gòu)十分靈活,能夠滿足各類并行加速需求支持OpenCL編程,方便算法移植系統(tǒng)處理靈活:FPGA或DSP可選尺寸小巧,方便集成擴展能力強 應(yīng)用領(lǐng)域并行控制

2017-06-08 10:33:07

DSP并行處理的方法摘 要:TI公司的TMS320C6x和AD公司的ADSP2106x是目前業(yè)界使用廣泛的數(shù)字信號處理器(DSP)。

2009-11-03 15:16:47

DSP的并行互連方法有哪些,其各自的優(yōu)缺點是什么?如何利用TMS320C6x的HPI組成多DSP互聯(lián)并行系統(tǒng)?如何利用ADSP2106x的Link口組成多DSP互連并行系統(tǒng)?

2021-04-08 06:41:13

充當(dāng),利用DSP的HPI接口組成一個多DSP互 連并行系統(tǒng),一般是一個主處理器和一個從處理器,此種方法的一個應(yīng)用實例是在雷達(dá)中的應(yīng)用。滑窗算法是數(shù)字信號處理中一種常用的基本算法,但滑窗算法一般

2019-04-08 09:36:19

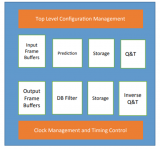

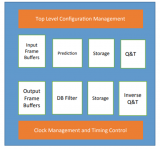

模塊,例如:廣告曝光點擊數(shù)據(jù)回收模塊、idmapping模塊、大數(shù)據(jù)報表模塊、內(nèi)置DMP模塊等等。 圖7-22 技術(shù)架構(gòu)概要示例 2. DSP內(nèi)部技術(shù)處理流程概要 DSP內(nèi)部技術(shù)處理主要依賴

2020-11-30 17:50:16

軟件架構(gòu)設(shè)計教程

2016-09-26 15:27:06

和DSP的重要準(zhǔn)則。 軟件無線電(SDR)結(jié)構(gòu)一直被認(rèn)為是基站開發(fā)的靈丹妙藥,而隨著其適應(yīng)新協(xié)議的能力不斷增強,軟件無線電結(jié)構(gòu)已被一些設(shè)計人員視為在單個基礎(chǔ)架構(gòu)設(shè)計中支持多種無線協(xié)議的重要解決方案

2019-07-26 06:09:25

這些繁重的工作負(fù)載,同時利用了多級流水線、并行處理和多任務(wù)處理的最新微架構(gòu)設(shè)計技術(shù),其成果就是用于傳感器中樞的功能最強大DSP架構(gòu),并且我們非常高興與客戶和合作伙伴一起工作,將基于SensPro的情境感知產(chǎn)品推向市場。”

2020-06-04 15:20:55

.FPGA+DSP的導(dǎo)引頭信號處理結(jié)構(gòu)成為當(dāng)前以及未來一段時間的主流。FPGA和DSP處理器具有截然不同的架構(gòu),在一種器件上非常有效的算法.在另一種器件上可能效率會非常低。如果目標(biāo)要求大量的并行處理或者最大

2019-08-30 06:31:29

測試會很困難。用硬件方式實現(xiàn)并行測試時,需要通過提供充足的測試資源來滿足并行測試的需求,而并行測試過程中激勵資源不足同樣會造成任務(wù)分解和調(diào)度難度增加,甚至導(dǎo)致競爭和死鎖,影響并行測試實現(xiàn)。因此,對多通道并行激勵信號的需求也是影響并行測試的關(guān)鍵因素。

2019-08-16 06:50:47

STM32軟件架構(gòu)設(shè)計的意義是什么?怎樣去設(shè)計STM32軟件的架構(gòu)呢?

2021-10-18 07:43:22

STM32軟件架構(gòu)1、架構(gòu)設(shè)計的意義(1)應(yīng)用代碼邏輯清晰,且避免代碼冗余;(2)代碼通用性,方便軟件高速、有效的移植;(3)各功能獨立,低耦合高內(nèi)聚;2、總體架構(gòu)圖3、結(jié)構(gòu)層說明4、遵循規(guī)則5、優(yōu)劣評估6、STM32實例說明

2021-08-04 07:23:12

各位大神,我想問下STM32f4xxx的圖像處理軟件是什么,求告知!!!

2016-05-08 23:06:32

盡量保持架構(gòu)不變移植到使用SYS/BIOS的TMSC6748上。

因為是單核所以MSGQ模塊用不上了,使用的是EMAC通訊,我這在spraas7g.pdf這篇文檔中也沒有找到關(guān)于?MSGQ_get的處理

2018-06-21 01:01:13

,使用TMS320C6748進(jìn)行多波束測深聲吶信號處理,由于組里做的板子是項目里使用的,很多端口都沒有引出,對我來說很難進(jìn)行系統(tǒng)測試;而且我們最終的項目需要使用兩塊DSP做信號處理才能保證系統(tǒng)實時性,我們計劃使用可靠性

2015-09-10 11:15:16

因工作需要,求整車電氣架構(gòu)設(shè)計軟件——PREEvision(盜版),價格可議,WetChat/***,非誠勿擾

2017-04-18 14:20:20

的設(shè)計中,可以通過接口與處理流水并行達(dá)到。即寫入、處理、讀出等操作可以做到流水式架構(gòu),從而增加處理的能力。流水是FPGA架構(gòu)設(shè)計中一種常用的手段,通過合理劃分流水層次,簡化設(shè)計,優(yōu)化時序。同時流水在

2019-08-02 08:30:00

為何要進(jìn)行嵌入式軟件架構(gòu)設(shè)計?如何進(jìn)行嵌入式軟件架構(gòu)設(shè)計?

2021-11-01 06:31:26

我現(xiàn)在在做一個基于labview環(huán)境下的圖像處理軟件主要就是對給定的avi視頻文件進(jìn)行幀提取比如我選定一個時間點能夠找出對應(yīng)的幀圖像應(yīng)該怎么做用什么版本的labview還需要其他工具包嗎?

2013-04-12 14:49:57

并行測試的實現(xiàn)途徑分為軟件方式和硬件方式。用軟件方式實現(xiàn)并行測試,關(guān)鍵是對測試任務(wù)的分解和調(diào)度,但可能會產(chǎn)生競爭或者死鎖現(xiàn)象。因此,在測試資源有限并且任務(wù)分解和調(diào)度算法不成熟的情況下,用軟件實現(xiàn)并行測試會很困難。那么,為什么說對多通道并行激勵信號的需求也是影響并行測試的關(guān)鍵因素呢?

2019-08-13 08:08:41

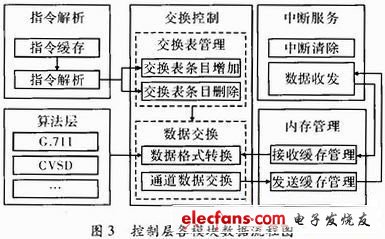

的軟件,變得更加重要。為滿足需求,文中提出一種基于DSP/ BIOS的軟件架構(gòu),可提高軟件的可維護(hù)性和可重用性,方便算法的裁減添加及程序的跨平臺移植,實現(xiàn)多類信號多路并行處理的軟件快速開發(fā)設(shè)計。1 DSP

2012-09-03 17:18:51

FIFO,最后由FPGA和PCI9656聯(lián)合將數(shù)據(jù)傳輸?shù)紺PCI總線,完成串行信號的處理。6 結(jié)語本文介紹了一種基于PFGA的多DSP并行處理系統(tǒng)的設(shè)計,重點對DSP并行結(jié)構(gòu)設(shè)計進(jìn)行了分析,并介紹了

2019-05-21 05:00:19

基于LabVIEW的動態(tài)應(yīng)力處理軟件開發(fā)

2013-08-27 20:03:28

“基于LabVIEW的瞬變電磁數(shù)據(jù)處理軟件設(shè)計”這個題目該怎么著手和設(shè)計呢?

2015-03-25 20:39:24

的算法)放在一個RISCprocessor上,如ARM。將信號處理軟件放在DSP上,利用DSP為信號處理功能提

2021-12-14 08:18:07

隨著紅外探測技術(shù)迅猛的發(fā)展,當(dāng)今紅外實時圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運算時,有時就顯得有些捉襟見肘了

2019-11-08 06:31:26

的軟件中斷SWI完成數(shù)據(jù)處理工作。DSP/BIOS提供兩類優(yōu)先線程:SWI(軟件中斷管理模塊)和TSK(任務(wù)管理模塊)。SWI是DSP/BIOS任務(wù)調(diào)度的核心,SWI任務(wù)是搶斷式的,即高優(yōu)先級的任務(wù)

2019-04-24 07:00:09

1.常見的誤解1.1小型系統(tǒng)不需要架構(gòu)設(shè)計 架構(gòu)應(yīng)當(dāng)滿足當(dāng)前需求并適當(dāng)?shù)目紤]重用和變更1.2 敏捷開發(fā)不需要框架 極限編程, 敏捷開發(fā)的出現(xiàn)使一些人誤以為軟件開發(fā)無需再做架構(gòu)了。 這是一個很大的誤解。 敏捷開發(fā)是在傳統(tǒng)瀑布式開發(fā)流程出現(xiàn)明顯弊端后提出的解決方案, 所以它必然有一個更高的起...

2021-10-27 09:22:55

【1】架構(gòu)設(shè)計的目的1.應(yīng)用的代碼邏輯清晰,且避免重復(fù)造輪子。2.方便軟件的移植。3.最大限度地復(fù)用。4.高內(nèi)聚低耦合。 【2】嵌入式架構(gòu)思路1.功能模塊化設(shè)計獲得需求------->歸類

2021-11-08 06:41:50

作為程序員,我覺得如果要走的更遠(yuǎn)必須要成為工程師,畢竟年齡和資歷都擺在那里了。所以就讓我這個老程序員淺談一下嵌入式軟件架構(gòu)設(shè)計。我參考的也是一篇博文。原圖如下不需要架構(gòu)有相當(dāng)多的嵌入式系統(tǒng)規(guī)模都較小,一般是為了某些特定的目的而設(shè)計的。受工程師認(rèn)識,客戶規(guī)模和項目進(jìn)度的影響,經(jīng)常不做任何架構(gòu)設(shè)計,直接以實現(xiàn)功能為目標(biāo)進(jìn)行編碼

2020-08-10 07:46:29

簡介今天可以使用的高集成度先進(jìn)射頻設(shè)計可讓工程師設(shè)計出性能水平超過以往的RF系統(tǒng),阻隔、靈敏度、頻率控制和基帶處理領(lǐng)域的最新進(jìn)展正在影響RF系統(tǒng)架構(gòu)設(shè)計,本文旨在探討某些參數(shù)特性,以及它們對系統(tǒng)性能的影響。

2019-06-21 07:08:26

隨著紅外探測技術(shù)迅猛的發(fā)展,當(dāng)今紅外實時圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運算時,有時就顯得有些捉襟見肘了

2019-08-23 08:29:27

您可以顯著提高無線系統(tǒng)中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2019-09-19 07:50:50

。許多DSP應(yīng)用開發(fā)人員正因為算法劃分困難而回避多內(nèi)核方法。也有一些任務(wù)(如加密)不支持并行運算。這并不是說多核方法未嘗試與DSP親近過。PicoChip公司很早前推出的picoArray架構(gòu)就整合了

2009-04-09 23:14:41

本文是機甲大師機器人控制的系列博客之一。在功能分析的基礎(chǔ)上,本文設(shè)計軟件的架構(gòu)。文章目錄1 開發(fā)階段2 軟件架構(gòu)設(shè)計2.1 頂層子系統(tǒng)2.1.1 子系統(tǒng)模型2.1.2 輸入接口2.2 電機控制子系統(tǒng)

2021-08-18 07:01:44

機甲大師機器人的軟件架構(gòu)設(shè)計如何實現(xiàn)?

2021-11-22 07:55:21

求助,labview的圖像處理軟件設(shè)計

2012-04-25 22:11:09

瑞芯微提供的媒體處理軟件平臺(Media Process Platform,簡稱 MPP)是適用于瑞芯微芯片系列的通用媒體處理軟件平臺。該平臺對應(yīng)用軟件屏蔽了芯片相關(guān)的復(fù)雜底層處理,其目的是為了屏蔽

2022-06-21 15:33:28

FPGA是一種可編程的硅芯片,DSP是數(shù)字信號處理,當(dāng)系統(tǒng)設(shè)計人員在項目的架構(gòu)設(shè)計階段就面臨到底采用FPGA還是DSP的重要問題。

2019-10-21 06:37:09

您可以顯著提高無線系統(tǒng)中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。常見于無線應(yīng)用中這類處理包括有限沖激響應(yīng)(FIR

2019-07-15 06:18:56

非主流精品圖像處理軟件主要特色: 1. 史上最“傻瓜”,人人都會用:“美圖秀秀”界面直觀,操作簡單,比同類軟件更好用!每個人都能輕松上手,從此做圖不求人! 2. 強大的人

2009-03-02 15:11:17

DSP集成開發(fā)環(huán)境--CCS及DSP/BIOS的原理與應(yīng)用:CCS是TI開發(fā)的一個完整的DSP集成開發(fā)環(huán)境,也是目前使用得最為廣泛的DSP開發(fā)軟件之一。 本書詳細(xì)地介紹了CCS中各種開發(fā)工具的使用,特

2008-10-30 10:54:20 263

263 基于VxWorks的多DSP并行處理系統(tǒng)的實現(xiàn)

2009-03-29 12:31:18 17

17 隨著數(shù)字化技術(shù)和系統(tǒng)軟、硬件技術(shù)的不斷提高,“軟件化雷達(dá)”成為雷達(dá)信號處理領(lǐng)域的最新研究方向。通用并行信號處理平臺是“軟件化雷達(dá)”的重要組成部分。本文討論了

2009-05-25 14:11:51 28

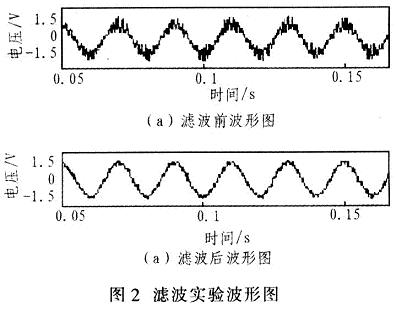

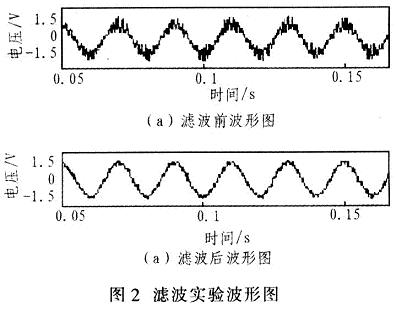

28 基于DSP/BIOS的交流信號檢測研究:介紹了TMS320F28l2的A/D轉(zhuǎn)換器的工作原理,并將其作為信號采樣模塊對交流電壓或電流信號進(jìn)行采樣;采用嵌入式實時操作系統(tǒng)DSP/BIOS作為操作平臺,對

2009-05-26 23:39:08 55

55 本文介紹了在DSP/BIOS 多任務(wù)機制下,如何實現(xiàn)數(shù)據(jù)采集與處理過程的并行化,并通過實例給出了具體的實現(xiàn)方法和程序代碼。關(guān)鍵字:DSP/BIOS 多任務(wù)機制 數(shù)據(jù)采集。傳統(tǒng)的數(shù)

2009-09-02 11:46:10 24

24 本文針對PR-650 光譜色度計配套的軟件不能滿足用戶的需求,設(shè)計了一套基于VisualC++6.0 的光譜色度計數(shù)據(jù)處理軟件。該軟件可實現(xiàn)對PR-650 的遙測,可對所測得的數(shù)據(jù)進(jìn)行實時計算

2009-12-18 16:04:10 36

36 文中提出了一種在DSP/BIOS下,實現(xiàn)Lorenz方程產(chǎn)生混沌信號并對語音實時信號加解密的模塊。信號產(chǎn)生和加解密模塊是在DSP/BIOS下實現(xiàn)多任務(wù)編程的,且可獨立于PC機運行。給出示波器

2009-12-23 16:03:44 10

10 本文介紹了基于DSP/BIOS 實時內(nèi)核的TI DSP 應(yīng)用程序參考框架RF5。另外,面對目前越來越多的多處理器系統(tǒng)設(shè)計以及典型的GPP-DSP 架構(gòu),本文提出了一種改進(jìn)的DSP應(yīng)用程序框架ERF5 以

2009-12-28 13:25:54 43

43 基于DSP和DSP/BIOS的實時雷達(dá)信號采集與處理系統(tǒng):介紹了一種在實時操作系統(tǒng)DSP和DSP/BIOS 平臺下的雷達(dá)信號實時采集" 處理與傳輸系統(tǒng)的設(shè)計和實現(xiàn)! 利用Tms320c6416DSP強大的數(shù)據(jù)處理

2010-01-16 16:59:46 25

25 如何創(chuàng)建一個DSP/BIOS程序?qū)嶒災(zāi)康?#1048698; 掌握DSP/BIOS的的開發(fā)步驟 認(rèn)識DSP/BIOS程序中各文件的含義 掌握如何使用DSP/BIOS配置工具實驗內(nèi)容

2010-04-07 10:56:16 71

71 一種具有功耗管理特性的DSP處理器的結(jié)構(gòu)設(shè)計。該處理器采用4級流水線和增強型的哈佛并行系統(tǒng)結(jié)構(gòu)及完善的時鐘管理模塊,提供了一種DSP處理器的集成設(shè)計。

2010-11-19 14:45:37 21

21 中文錄音編輯處理軟件WAVECN

2010-11-26 15:29:07 23

23 摘 要: DSP/BIOS 是運行在數(shù)字信號處理器(DSP)中的一個小型軟件,它為開發(fā)者提供對程序的控制執(zhí)行和對變量的實時監(jiān)測。而且可以合理地對實時多線程系統(tǒng)進(jìn)行時間規(guī)劃

2006-03-11 12:24:33 1884

1884

基于DSP/BIOS的FIR數(shù)字濾波器設(shè)計與實現(xiàn)

1 引言

數(shù)字信號處理器(DSP)擁有強大的數(shù)字信號處理能力,與其配套的集成可視化開發(fā)環(huán)境CCS(Coder Co

2009-12-16 10:23:04 1252

1252

信號處理器(DSP),信號處理器(DSP)是什么意思

DSP是(digital signal processor)的簡稱,是一種專門用來實現(xiàn)信號處理算法的微處理器芯片

2010-03-26 14:53:54 15467

15467 架構(gòu)設(shè)計是一個非常大的話題,不管寫幾篇文章,接觸到的始終只是冰山一角,更多的是實踐中去體會。這篇文章主要介紹面向?qū)ο驩O、面向方面AOP和面向服務(wù)SOA這三個要素在架構(gòu)設(shè)計中

2011-06-22 10:09:12 1320

1320

提出了~種基于StarFabric互聯(lián)的并行雷達(dá)信號處理機構(gòu)架,并對其進(jìn)行了建模,分析了StarFabric網(wǎng)絡(luò)傳輸性能,設(shè)計了其中的數(shù)字信號處理(DSP)模塊和其它模塊.DSP模塊集成8片C64x DSP和2

2011-08-26 14:30:13 17

17 在水下日標(biāo)檢測和跟蹤系統(tǒng)中,多目標(biāo)方位估計算法起著重要的作用.MUSIC算法是最具代表性的方法}為了滿足目標(biāo)方位估計對高速變時并行處理技術(shù)的要求,針對水下陣列信號處理的實

2011-10-12 16:19:54 41

41 電子發(fā)燒友網(wǎng)站提供《PSCS5圖片處理軟件.exe》資料免費下載

2012-09-25 07:50:10 25

25 電子發(fā)燒友網(wǎng)站提供《最小二乘法數(shù)據(jù)處理軟件.rar》資料免費下載

2012-11-02 16:40:16 27

27 分析了目前軟PLC在實時性方面存在的不足;提出采用基于DSP/BIOS實時內(nèi)核的嵌入式處理器的軟PLC執(zhí)行系統(tǒng)架構(gòu)。首先,通過分析軟PLC執(zhí)行系統(tǒng)的架構(gòu)及工作原理,給出了基于DSP/BIOS的任務(wù)

2013-04-15 19:28:18 15

15 Canopus Edius(非線性編輯軟件)V6.02專業(yè)視頻處理軟件

2015-08-12 18:36:12 3

3 基于LabVIEW的數(shù)據(jù)采集與處理軟件編程技巧。

2016-01-20 16:28:37 43

43 這是一種最小二乘法的數(shù)據(jù)處理軟件,很不錯的,從老師那下載的。

2016-04-29 14:12:14 43

43 箭載電場數(shù)據(jù)處理軟件設(shè)計_程丹丹

2017-03-15 08:00:00 0

0 本文參考ISO26262的要求,同時考慮AUTOSAR代碼生成的兼容性,給出使用Simulink實現(xiàn)軟件架構(gòu)設(shè)計的一些建議。

2017-09-19 14:40:46 36

36 基于FPGA和多DSP的多總線并行處理器設(shè)計

2017-10-19 13:40:31 4

4 DSP_BIOS講座

2017-10-20 11:26:05 3

3 摘要 利用DSP芯片設(shè)計出能夠支持多類信號多路并行處理的軟件,可減少外圍專用算法芯片的使用,降低設(shè)計成本、縮小印制板尺寸、縮短開發(fā)周期。文中介紹了一種利用DSP/BIOS操作系統(tǒng)進(jìn)行快速開發(fā)

2017-10-21 09:53:21 0

0 的軟件,變得更加重要。為滿足需求,文中提出一種基于DSP/ BIOS的軟件架構(gòu),可提高軟件的可維護(hù)性和可重用性,方便算法的裁減添加及程序的跨平臺移植,實現(xiàn)多類信號多路并行處理的軟件快速開發(fā)設(shè)計。 1 DSP/BIOS簡介 DSP/BIOS是TI公司推出的實時

2017-10-21 10:04:18 0

0 多DSP的高速通用并行處理系統(tǒng)研究與設(shè)計

2017-10-23 15:19:06 6

6 要求,因此,需采用專用的數(shù)字信號處理器(DSP)來進(jìn)行高速運算。盡管當(dāng)前的數(shù)字信號處理器已達(dá)到較高水平, 但單片DSP芯片的處理能力還是不能滿足寬帶雷達(dá)的性能要求,需要引入并行處理技術(shù),在本設(shè)計中使用4片DSP芯片組成并行處理

2017-10-31 09:58:04 0

0 等突出優(yōu)點,特別是在夜間、霧天及能見度不良、通視度較差的情況或者復(fù)雜電磁環(huán)境下,是戰(zhàn)場信息感知不可缺少的重要手段之一。 并行DSP處理的目的是采用多個處理單元(DSP)同時對任務(wù)處理以減少任務(wù)的執(zhí)行時間。多DSP并行處

2017-10-31 11:50:02 0

0 摘要:為滿足寬帶雷達(dá)信號處理對處理速度和實時性的要求,提出一種基于4片ADSP-TS201S的DSP并行系統(tǒng)設(shè)計。通過分析比較3種ADSP-TS2 01S的并行處理結(jié)構(gòu),結(jié)合實際需求,采用外部總線

2017-10-31 16:41:04 0

0 TMS320C55x DSP是一種高性能的數(shù)字信號處理器,其強大的并行處理能力能夠進(jìn)一步提高其運算能力。本文介紹了C55xDSP的內(nèi)核結(jié)構(gòu)以及用戶自定義并行指令時必須遵守如下3條并行處理基本規(guī)則

2017-11-03 16:19:47 2

2 針對信號處理數(shù)據(jù)量大、實時性要求高的特點,從實際應(yīng)用出發(fā),設(shè)計了以雙DSP+FPGA為核心的并行信號處理模塊。為了滿足不同的信號處理任務(wù)需求,F(xiàn)PGA可以靈活地選擇與不同的DSP組成不同的信號處理

2017-11-17 06:11:40 2373

2373

架構(gòu)設(shè)計是一個非常大的話題,不管寫幾篇文章,接觸到的始終只是冰山一角,更多的是實踐中去體會。這篇文章主要介紹面向?qū)ο驩O、面向方面AOP和面向服務(wù)SOA這三個要素在架構(gòu)設(shè)計中的位置與作用。 架構(gòu)設(shè)

2017-12-01 11:57:02 487

487

本文主要介紹了DSP/BIOS定義及相關(guān)軟件開發(fā)說明。

2018-06-03 08:00:00 5

5 本視頻介紹數(shù)字信號處理和DSP架構(gòu)的基礎(chǔ)知識。此外還將介紹ADI公司的處理器DSP系列產(chǎn)品,這類產(chǎn)品進(jìn)入不同細(xì)分市場和應(yīng)用的具體方式以及支持DSP系統(tǒng)開發(fā)所需的硬件和軟件工具。

2019-07-08 06:06:00 3933

3933 過程ID:SWE.2 過程名稱:軟件架構(gòu)設(shè)計 過程目的:軟件架構(gòu)設(shè)計過程目的是建立一個架構(gòu)設(shè)計,識別哪些軟件需求應(yīng)該分配給軟件的哪些要素,并根據(jù)已定義的標(biāo)準(zhǔn)評估軟件架構(gòu)設(shè)計。 ? 過程結(jié)果

2021-01-11 10:36:40 2401

2401 可檢測霧滴尺寸特性的水敏紙圖像處理軟件

2021-06-18 15:48:58 12

12 STM32軟件架構(gòu)1、架構(gòu)設(shè)計的意義(1)應(yīng)用代碼邏輯清晰,且避免代碼冗余;(2)代碼通用性,方便軟件高速、有效的移植;(3)各功能獨立,低耦合高內(nèi)聚;2、總體架構(gòu)圖3、結(jié)構(gòu)層說明4、遵循規(guī)則5、優(yōu)劣評估6、STM32實例說明

2021-11-06 09:05:58 26

26 下面將從芯片的架構(gòu)設(shè)計、微架構(gòu)設(shè)計、使用設(shè)計文檔、設(shè)計分區(qū)、時鐘域和時鐘組、架構(gòu)調(diào)整與性能改進(jìn)、處理器微架構(gòu)設(shè)計策略等角度進(jìn)行說明,并以視頻H.264編碼器設(shè)計為例。

2023-05-08 10:42:28 817

817

圖像處理軟件ACDSee下載

2023-06-29 15:08:26 7

7 DSP處理器以其高性能運算能力、并行計算能力、專用指令集和架構(gòu)設(shè)計、高速數(shù)據(jù)存儲和傳輸能力、低功耗設(shè)計和實時性等特點,成為執(zhí)行數(shù)字信號處理任務(wù)的重要工具和設(shè)備。它們廣泛應(yīng)用于音頻、視頻、通信和圖像處理等領(lǐng)域。

2023-08-21 15:27:09 1936

1936 過程ID : SWE.2 過程名稱 : 軟件架構(gòu)設(shè)計 過程目的 : 軟件架構(gòu)設(shè)計過程目的是建立一個架構(gòu)設(shè)計,識別哪些軟件需求應(yīng)該分配給軟件的哪些要素,并根據(jù)已定義的標(biāo)準(zhǔn)評估軟件架構(gòu)設(shè)計。 過程結(jié)果

2023-08-24 09:43:48 447

447

電子發(fā)燒友App

電子發(fā)燒友App

評論