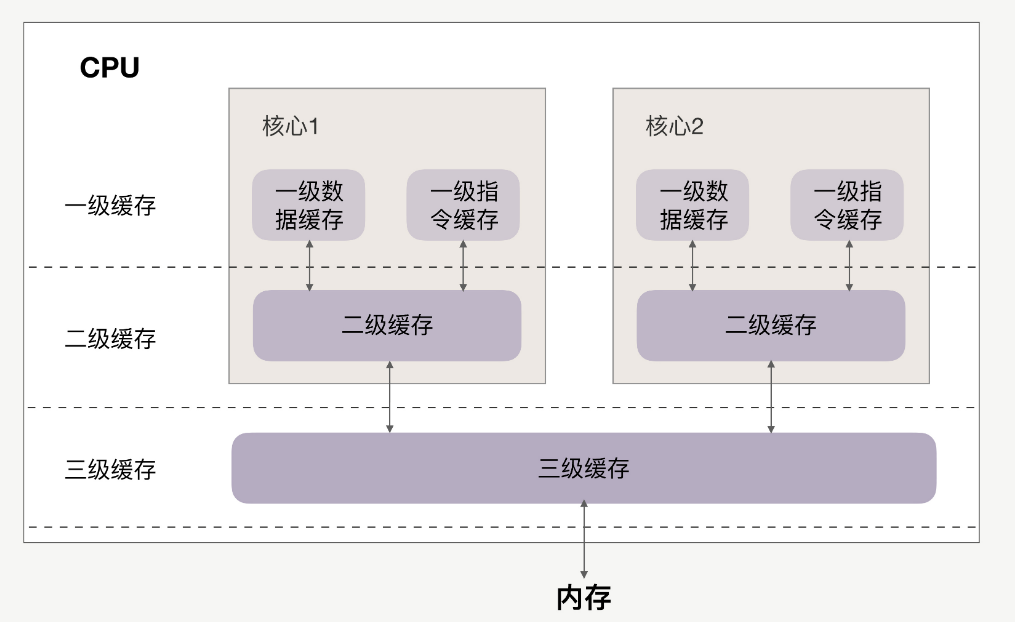

CPU接收到指令后,它會最先向CPU中的一級緩存(L1 Cache)去尋找相關的數據,然一級緩存是與CPU同頻運行的,但是由于容量較小,所以不可能每次都命中。

2022-10-21 09:10:54 1866

1866 A53的L1 Data cache遵從的是MOESI協議,如下所示在L1 data cache的tag中存有MOESI的標記位。

2023-09-01 15:01:21 5024

5024

Cache是位于CPU與主存儲器即DRAM(Dynamic RAM,動態存儲器)之間的少量超高速靜態存儲器SRAM(Static RAM)

2023-10-31 15:07:23 347

347

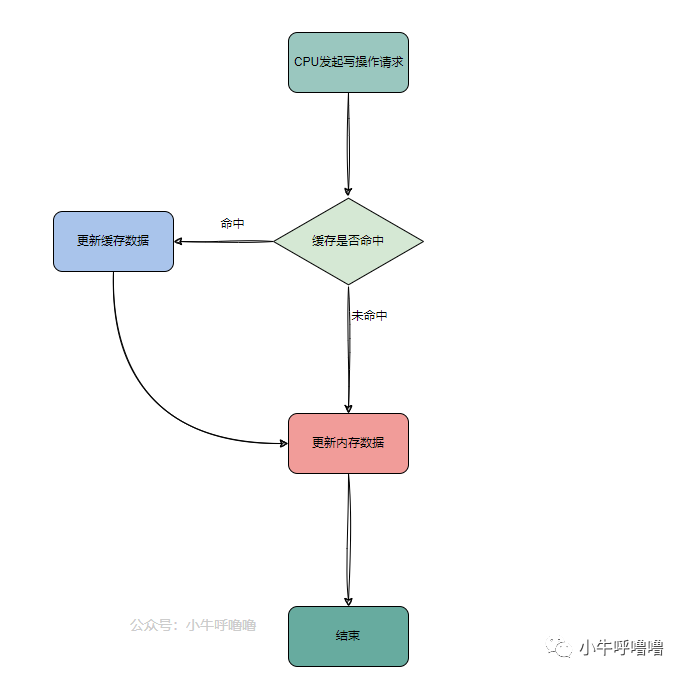

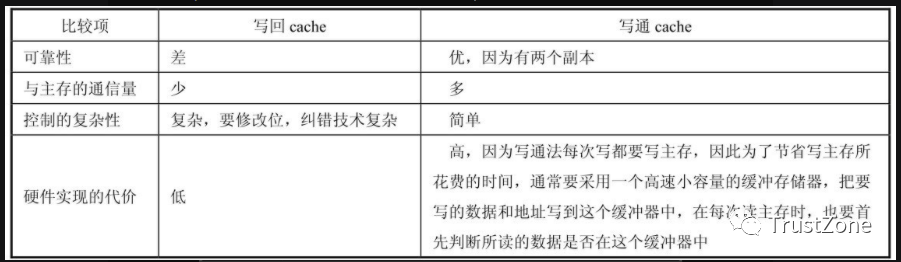

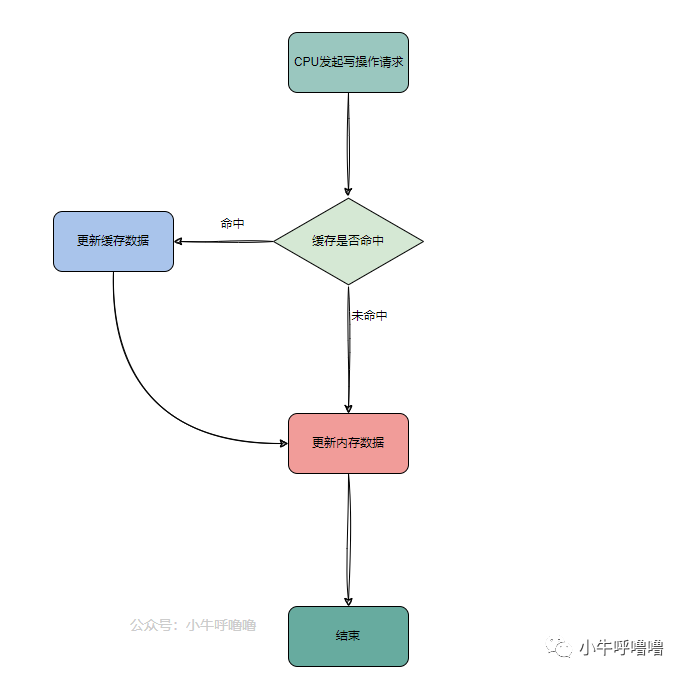

我們介紹`CPU Cache`的組織架構及其進行**讀操作**時的尋址方式,但是緩存不僅僅只有讀操作,還有 **寫操作** ,這會帶來一個新的問題

2023-12-04 15:05:32 460

460

請問:

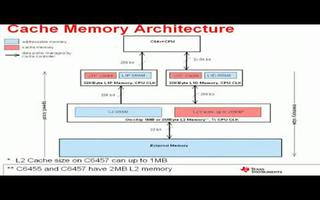

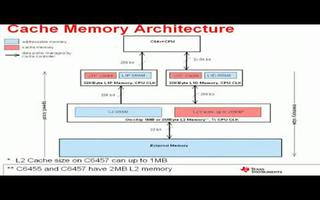

1、如果將L1D CACHE設置為32KB,L1P CACHE設置為32KB,L2 CACHE設置為0KB;

在core的LL2中定義了兩個數組,out1占用32KB存儲空間,out2占用

2018-06-21 13:28:12

Cache為什么還要分I-Cache,D-Cache,L2 Cache,作用是什么?

2023-10-25 06:38:45

Cache即高速緩存,它的出現基于兩種因素:一、CPU的速度和性能提高很快,而主存速度較低且價格高;二、程序執行的局部性特點。將速度較快而容量有限的SRAM構成Cache,可以盡可能發揮CPU

2019-10-12 06:01:10

存儲器的層次結構是怎樣的?由哪些部分組成的?有何特點?Cache的原理是什么?Cache地址的過程是怎樣的?

2021-12-23 09:35:31

cache到 ?ddr里面的數據呢?還是數據自動cache到L1D里面呢?能不能詳細解釋一下cache的工作原理!期待您的答復!謝謝!

2018-06-21 15:10:16

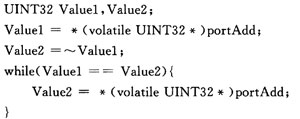

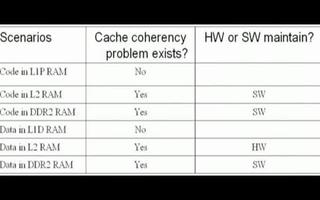

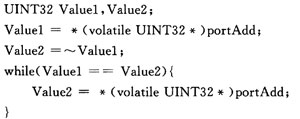

cache有哪些缺點很多時候大家談論cache都只會談及各種好處,比如加快程序執行的速度,減少主存的訪問。但是,cache還引入了沒有cache的系統不存在的一些問題。其中一個缺點就是,程序

2022-06-15 16:16:16

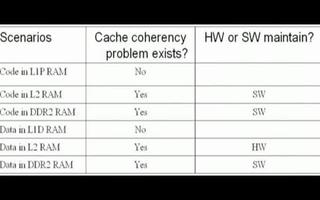

文章目錄1、cache的應用——什么時候需要刷cache1、cache的應用——什么時候需要刷cache(1)、cpu在往內存(src地址)寫數據時,cache中會緩存這些數據,并沒有立即同步到

2021-07-22 08:43:16

ARM處理器中的邏輯cache和物理cache是什么?有沒有哪位大神可以幫忙解決一下這個問題

2022-11-03 15:25:40

cache。這對于那些需要頻繁修改頁表映射的多任務系統具有顯著優勢。使用虛擬地址作為index也有一些硬件優勢,這意味著cache硬件在進行cache look up時不需要進行虛擬地址到物理地址

2022-06-20 15:22:23

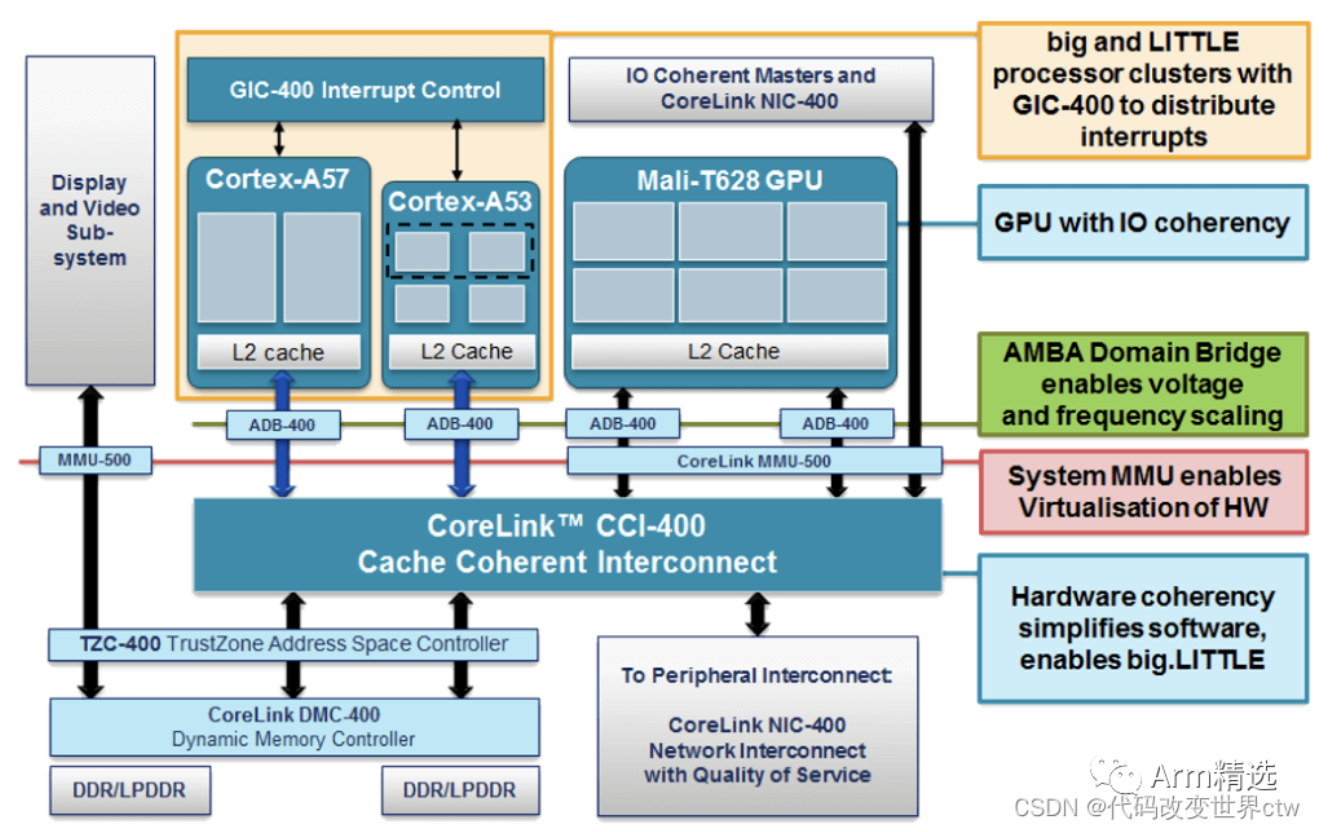

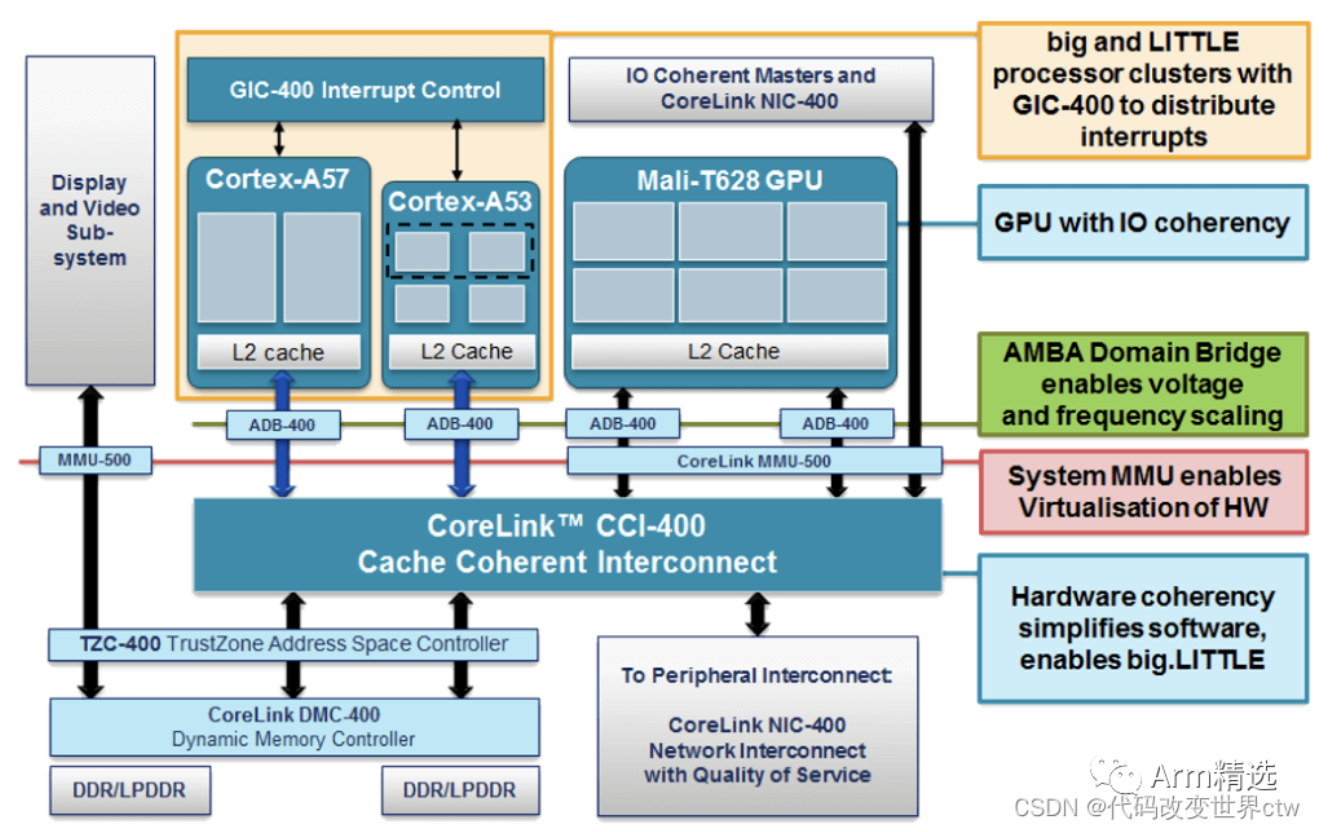

Arm處理器cache的進化Cache對CPU處理器的性能影響毋庸置疑。RISC構架成功的一個重要因素就是cache對內存訪問性能的提升。RISC處理器普遍采用load-store的構架,隨著

2022-12-14 16:17:15

對于其它外設不會修改,即只有CPU進行讀寫的數據,有兩種配置方案:1.將L2 Cache配置為SRAM,數據存于L2 Cache,即數據直接放置于L2 Cache中2.配置L2 Cahce全部為緩存,將數據存于DDR2中,配置此段DDR2相應的MAP寄存器以上兩種方案,哪種方案更優?

2019-08-05 14:50:55

except for not having the U bit.我們可以看到,Cache分為address section和data section兩個部分. 它們實際上就是CPU中的一小塊RAM,這一

2014-12-29 15:42:51

對于沒有接觸過底層技術的朋友來說,或許從未聽說過cache。畢竟cache的存在對程序員來說是透明的。在接觸cache之前,先為你準備段code分析:int arr[10][128];for (i

2022-04-21 11:10:49

設計多級cache可以有很多種方式,可以根據一個cache的內容是否同時存在于其他級cache來分類,即Cache inclusion policy。如果較低級別cache中的所有cacheline

2022-07-20 14:46:15

請教:平臺是6678,ccs5.4,使用CSL庫函數 CACHE_disableCaching 禁止cache 0x8000000地址CACHE_disableCaching(128);調用

2018-12-28 11:12:02

工程師你好:

最近看了6678的cache手冊,仍有下面不確定的問題,請解答(以下都是說的數據cache,不是程序cache)。

1、CPU對L2 RAM和L2 Cache的訪問速度是不是一樣

2018-06-21 07:43:09

幫忙給解答一下一個基本概念,cpu在訪問數據時,如果數據不在L1D和L2中,就需要從DDR等外設中取數,文獻中說過,“cache會prefetch讀取cache_line長度的地址,保證連續的地址上

2018-06-21 17:31:26

CPU Cache是什么?如何查看自己電腦CPU的Cache信息呢?

2021-10-19 08:42:39

請問,用I.MX6UL開發板OKMX6UL,使用Linux的情況下,如何獲取CPU中L1/L2的Cache狀態和大小;如何禁用和使能Cache?

2022-11-29 06:37:16

我最近看6437的cache。話說如果不使能所有cache.那dspcpu也是可以訪問ddr2的是吧。那這個路徑是怎么樣的呢。在手冊上的Block Diagram等都沒看到。都講的是ddr2到l2,l1到cpu這么個cache路徑。按常識肯定是cpu直接訪問了ddr2,只是速度慢點而已。

2018-08-02 07:15:27

總是弄不明白cache_inv,cache_wb以及cache_wbinv都有什么區別,請專家指教!

2018-07-24 07:41:03

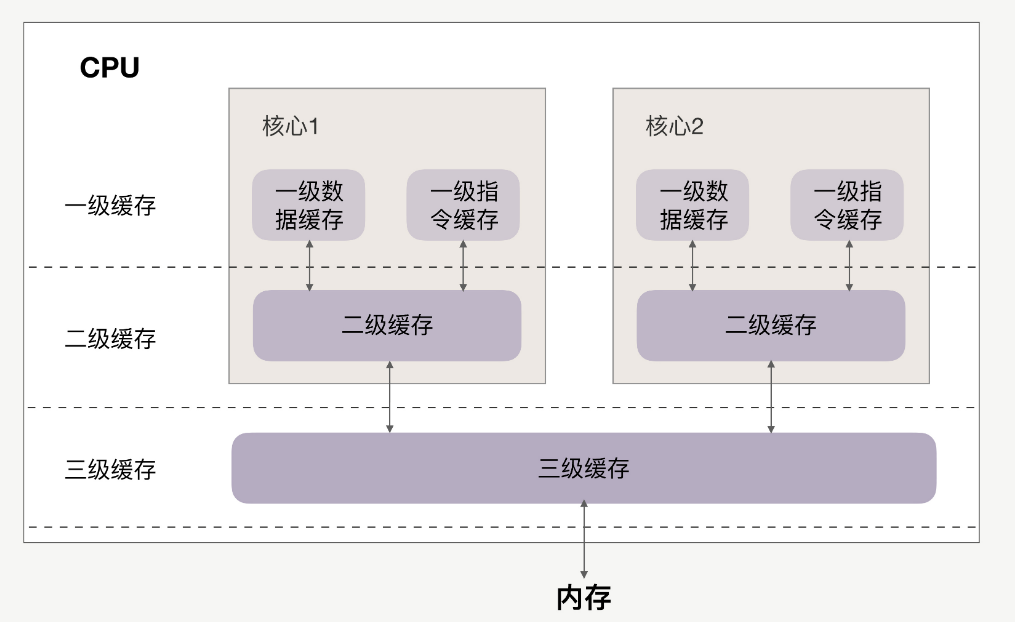

Cycle,且往往被分成 ICache 和 DCache,一般 L1 Cache 是由一個 CPU 核心獨享的L2 Cache 一般有較高的相聯度 (減少 miss rate) ,容量為幾百 KB ~ 幾

2022-09-16 14:31:35

以優化壓縮cache的替換策略為目標,提出一種優化的基于修正LRU的壓縮cache替換策略MLRU-C。MLRU-C策略能利用壓縮cache中額外的tag資源,形成影子tag機制來探測并修正LRU替換策略的錯誤

2009-04-15 09:51:03 36

36 針對嵌入式CPU 指令處理速度與存儲器指令存取速度不匹配問題,本文基于FPGA 設計并實現了可以有效解決這一問題的指令Cache。根據嵌入式五級流水線CPU 特性,所設計指令Cache 的地

2009-08-05 14:27:54 36

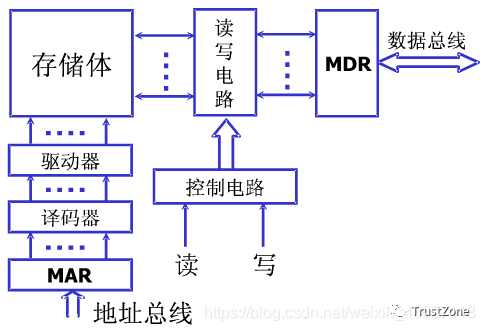

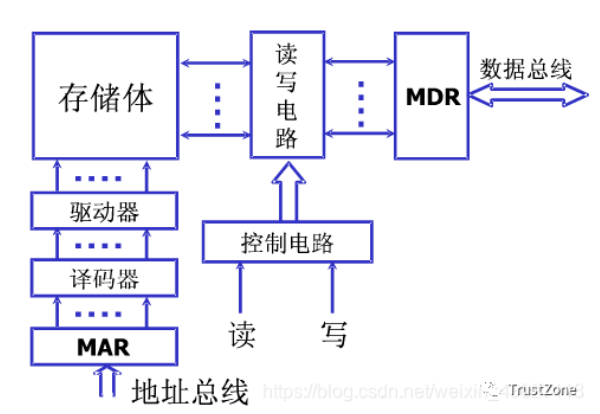

36 Cache的工作原理:Cache的工作原理是基于程序訪問的局部性。對大量典型程序運行情況的分析結果表明,在一個較短的時間間隔內,由程序產生的地址往往集中在存儲器邏輯地址空

2009-09-19 07:48:54 13

13 摘要:在SoC系統中,片上緩存(Cache)的采用是解決片上處理器和片外存儲器之間速度差異的重要方法,Cache中用來存儲標記位并判斷Cache是否命中的Tag電路的設計將會影響到整個Cache的

2010-05-08 09:26:24 11

11 CACHE對于CPU來說非常重要,它們是處理器和內存等數據交換的高速緩沖地帶,可以對使用過的數據和指令進行有選擇的保留,以便以后直接調用,這樣將大大提高系統的速度。

2010-10-04 21:21:18 22

22 Cache結構的低功耗可重構技術分析

在分析Cache性能的基礎上介紹了當前低功耗Cache的設計方法,提出了一種可重構Cache模型和動態

2009-03-29 15:07:55 663

663

什么是緩存Cache

即高速緩沖存儲器,是位于CPU與主內存間的一種容量較小但速度很高的存儲器。由于CPU的速度遠高于主內存,CPU直接

2010-01-23 10:57:13 735

735 什么是Cache/SIMD?

Cache :即高速緩沖存儲器,是位于CPU與主內存間的一種容量較小但速度很高的存儲器。由于CPU的速度遠高于主內存

2010-02-04 11:29:44 515

515 什么是Instructions Cache/IMM/ID

Instructions Cache: (指令緩存)由于系統主內存的速度較慢,當CPU讀取指令的時候,會導致CPU停下來

2010-02-04 11:51:01 583

583 什么是Cache

英文縮寫: Cache

中文譯名: 高速緩存器

分 類: IP與多媒體

解 釋: 信息在本地的臨時存儲

2010-02-22 17:26:39 948

948 高速緩存(Cache),高速緩存(Cache)原理是什么?

高速緩存Cache是位于CPU和主存儲器之間規模較小、存取速度快捷的靜態存儲器。Cache一般由

2010-03-26 10:49:27 6717

6717 cache基本知識培訓教程[2]

相聯度越高(即 n 的值越大), Cache 空間的利用率就越高,塊沖突概率就越低,因而 Cache 的失效率就越低。塊沖突是指一

2010-04-13 16:25:37 1982

1982 降低Cache失效率的方法[2]

表4.7列出了在這兩種極端情況之間的各種塊大小和各種 Cache 容量的平均訪存時間。速度最快的情況: Cache 容量為1KB、4KB、1

2010-04-13 16:33:59 4688

4688 嵌入式編程需注意的Cache機制及其原理

1 Cache的原理 Cache即高速緩存,它的出現基于兩種因素:一、CPU的速度和性能提高很快,而主

2010-05-26 16:40:03 1150

1150

現代高速處理器的設計中對于cache技術的研究已經成為了提高處理器性能的關鍵技術,本文針對在流水線結構中采用非阻塞cache技術進行分析研究,提高cache的命中率,降低缺少代價,提高處理器的性能,并介紹了“龍騰”R2處理器的流水線結構的非阻塞cache 的設計。

2015-12-28 09:54:57 8

8 1 Cache的原理 Cache即高速緩存,它的出現基于兩種因素:一、CPU的速度和性能提高很快,而主存速度較低且價格高;二、程序執行的局部性特點。將速度較快而容量有限的SRAM構成Cache,可以

2017-11-01 16:16:20 0

0 隨著集成電路設計復雜度指數級增長,功能驗證已經越來越成為大規模芯片設計的瓶頸,而在多核處理器中,Cache -致性協議十分復雜,驗證難度大。針對Cache -致性協議驗證提出基于模擬驗證的一種

2017-11-17 17:24:07 2

2 cpu在執行程序所用的指令和讀數據都是針對內存的,也就是從內存中取得的。由于內存讀寫速度慢,為了提高cpu和內存之間數據交換的速度,在cpu和內存之間增加了cache,它的速度比內存快,但是造價

2018-04-02 10:35:06 6404

6404 本文開始闡述了CACHE的概念、CACHE替換機構與讀寫操作,其次介紹了寄存器的原理以及它的主要技術,最后闡述了寄存器和cache兩者之間的區別。

2018-04-11 14:10:33 11827

11827 GPU采用了數量眾多的計算單元和超長的流水線,但只有非常簡單的控制邏輯并省去了Cache。而CPU不僅被Cache占據了大量空間,而且還有有復雜的控制邏輯和諸多優化電路,相比之下計算能力只是CPU很小的一部分

2018-04-28 10:26:00 28332

28332 GPU cache是由Alembic文件派生出來的一種文件格式,為獲取Maya中快速播放的性能專門做了優化。這些性能的提升來自于GPU cache文件求值的方式。GPU cache節點會避開Maya的dependency graph求值機制,把緩存數據直接發送到系統的圖形卡接口進行處理。

2018-04-28 10:29:00 2726

2726 C64+ 系列DSP上Cache 的應用(第一部分)

2018-06-13 01:08:00 3780

3780

C64+ 系列DSP上Cache 的應用(第二部分)

2018-06-13 01:01:00 3661

3661

從Cache-主存模型來看,一方面既要使CPU的訪存速度接近于訪Cache的速度,另一方面為用戶程序提供的運行空間應保持為主存容量大小的存儲空間。在采Cache-主存層次的系統中,Cache對用戶程序而言是透明的,也就是說,用戶程序可以不需要知道Cache的存在。

2018-08-20 15:27:41 4230

4230

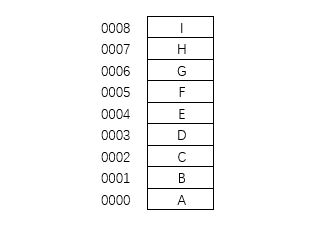

當CPU開始訪問地址0020h時,假設cache已經被完全被設定無效了(invalidated),即沒有cache line包含有效數據。

2018-09-09 10:39:57 7601

7601 當你讀寫文件的時候,Linux內核為了提高讀寫性能與速度,會將文件在內存中進行緩存,這部分內存就是Cache Memory(緩存內存)。即使你的程序運行結束后,Cache Memory也不會自動釋放。

2019-04-26 15:49:14 1085

1085 。 本文簡介了Cache的概念、原理、結構設計以及在PC及CPU中的實現。 Cache的工作原理 Cache的工作原理是基于程序訪問的局部性。 對大量典型程序運行情況的分析結果表明

2019-04-02 14:38:30 1951

1951 文件 Cache 管理是 Linux 內核中一個很重要并且較難理解的組成部分。本文詳細介紹了 Linux 內核中文件 Cache 管理的各個方面,希望能夠對開發者理解相關代碼有所幫助

2019-04-02 14:38:49 344

344 那么什么是 cache?如何利用這一新特性編寫高性能的程序?又有什么要注意的地方嗎?

2019-05-07 15:24:52 7920

7920

更詳細的講,cache的結構其實和內存的結構類似,也包含地址和內容,只是cache的內容除了存的數據(data)之外,還包含存的數據的物理內存的地址信息(tag),因為CPU發出的尋址信息都是針對

2019-06-03 14:24:13 10854

10854

page)即為頁緩存(page cache)。塊緩存(buffer cache),則是內核為了加速對底層存儲介質的訪問速度,而構建的一層緩存。

2021-07-02 14:25:13 2299

2299

CACHE基礎 對cache的掌握,對于Linux工程師(其他的非Linux工程師也一樣)寫出高效能代碼,以及優化Linux系統的性能是至關重要的。簡單來說,cache快,內存慢,硬盤更慢

2021-07-26 15:18:58 1507

1507

Linux內核文件Cache機制(開關電源技術與設計 第二版)-Linux內核文件Cache機制? ? ? ? ? ? ? ??

2021-08-31 16:34:54 4

4 微軟內核構架之Cache管理器(實用電源技術手冊磁性元器件分冊pdf)-微軟內核構架之Cache管理器? ? ? ? ? ? ? ? ? ? ? ?

2021-08-31 16:39:58 10

10 作者:Spongecaptain https://spongecaptain.cool/SimpleClearFileIO/ 1. Page Cache 1.1 Page Cache

2021-10-20 14:12:41 5320

5320

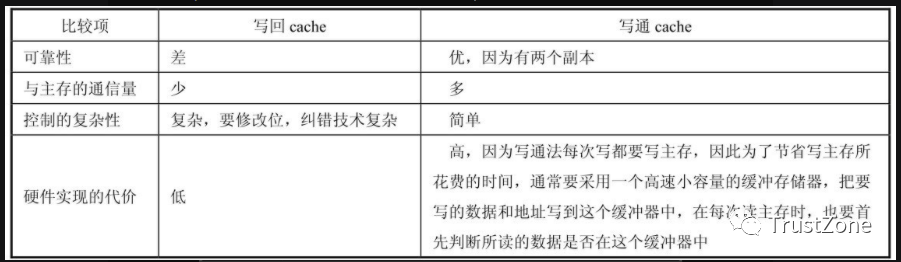

關于cache,大概可以從三個方面進行闡述:內存到cache的映射方式,cache的寫策略,cache的替換策略。 映射方式 內存到cache的映射方式,大致可以分為三種,分別是:直接映射

2021-11-21 11:09:50 2127

2127 關于Cache的其它內容 上面我們所描述情況,在訪問cache前,已經將虛擬地址轉換成了物理地址,其實,不一定,也可是是虛擬地址直接訪問cache,倒底是使用物理地址還是虛擬地址,這就是翻譯方式

2021-11-21 11:12:14 2075

2075 Bbuffer 與 Cache 非常類似,因為它們都用于存儲數據數據,被應用層讀取字節數據。

2022-07-01 10:44:24 2651

2651 電子發燒友網站提供《SALELF 2 MCU Flash Cache指南.pdf》資料免費下載

2022-09-26 15:12:00 0

0 本文會從結構,原理以及應用方面對 MPU 和 Cache 進行分析,主要目的是希望讀者對 Cache 有基本的了解,在具體的實際應用中,使用帶有一級 cache 的 MCU 時,避免常見的錯誤。

2022-09-28 11:05:20 0

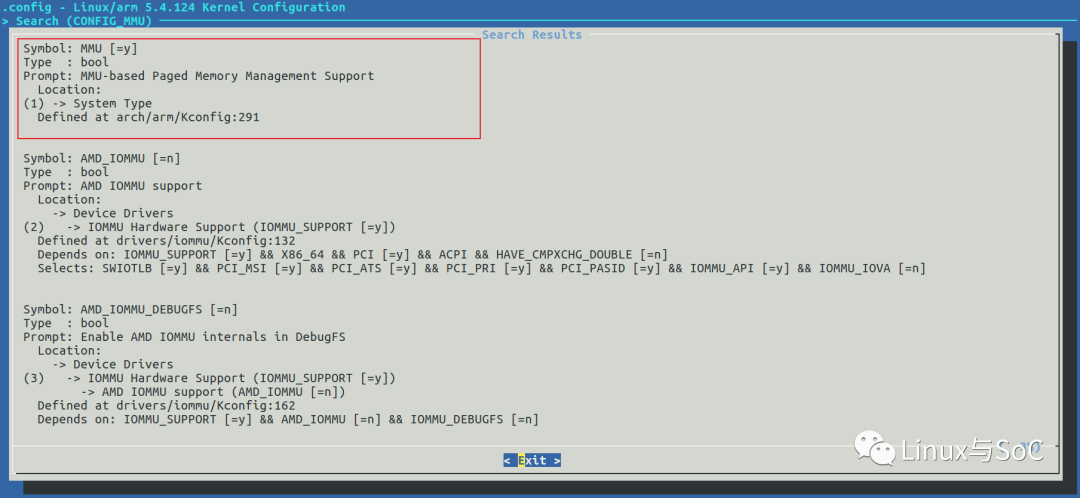

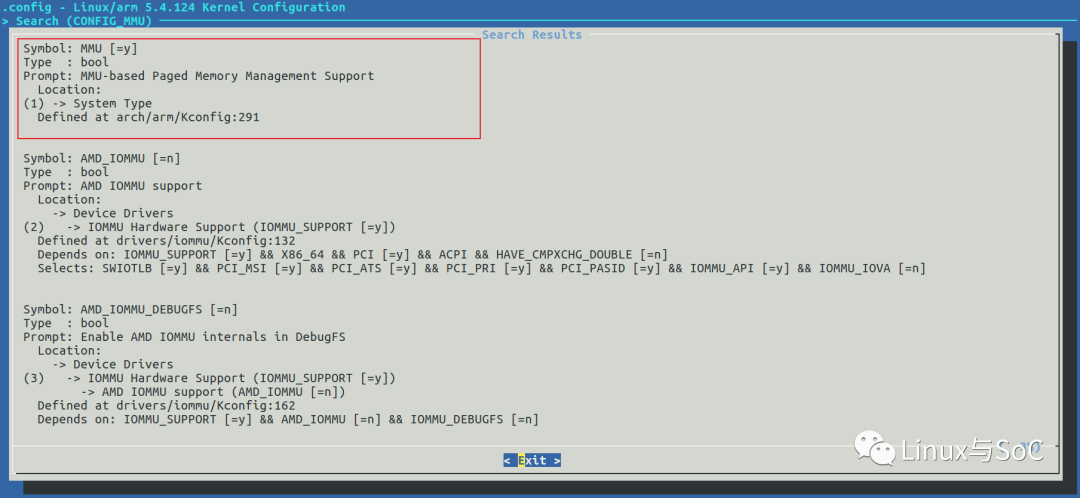

0 對cache的掌握,對于Linux工程師(其他的非Linux工程師也一樣)寫出高效能代碼,以及優化Linux系統的性能是至關重要的。簡單來說,cache快,內存慢,硬盤更慢。在一個典型的現代CPU中比較接近改進的哈佛結構,cache的排布大概是這樣的:

2022-10-18 09:01:12 1195

1195 CPU register的速度一般小于1ns,主存的速度一般是65ns左右。速度差異近百倍。在硬件上,我們將cache放置在CPU和主存之間,作為主存數據的緩存。

2022-11-16 11:17:32 589

589 由于寫入數據和讀取指令分別通過 D-Cache 和 I-Cache,所以需要同步 D-Cache 和 I-Cache,即復制后需要先將 D-Cache 寫回到內存,而且還需要作廢當前的 I-Cache 以確保執行的是 Memory 內更新的代碼

2022-12-06 09:55:56 1163

1163 現代CPU,通常L1 cache的指令和數據是分離的。這樣可以實現2條高速公路并行訪問,CPU可以同時load指令和數據。當然,cache也不一定是一個core獨享,現代很多CPU的典型分布是這樣的,比如多個core共享一個L3。比如這臺的Linux里面運行lstopo命令:

2022-12-06 10:38:50 458

458 當CPU想要訪問主存中的元素時,會先查看Cache中是否存在,如果存在(稱為Cache Hit),直接從Cache中獲取,如果不存在(稱為Cache Miss),才會從主存中獲取。Cache的處理速度比主存快得多。

2022-12-12 09:17:51 469

469 L1 Cache和L2 Cache通常和處理器是在一塊實現的。在SoC中,主存和處理器之間通過總線SYSBUS連接起來。

2023-01-08 10:56:03 566

566 占用非常大的面積,大概在一半以上,而且一個好的 Cache 的設計復雜度非常高,可能比較 CPU 的 Pipeline 還要復雜。這里要考慮成本,設計復雜度,或者其他方面的考慮。你知道 L1

2023-01-11 09:34:49 837

837 所以在linux初級開發者接觸cache時,腦海里會不自覺的思考:硬件行為,都是被ICer設計好的;所以他們也并沒有深究cache的層次結構,也沒有繼續挖掘cache和驅動軟件的千絲萬縷的關系,腦海里想象的拓撲圖,大致是這樣:

2023-03-02 10:34:48 556

556 Cache被稱為高速緩沖存儲器(cache memory),是一種小容量高速的存儲器,屬于存儲子系統的一部分,存放程序常使用的指令和數據。

2023-03-06 15:05:31 2879

2879 Cache存儲器也被稱為高速緩沖存儲器,位于CPU和主存儲器之間。之所以在CPU和主存之間要加cache是因為現代的CPU頻率大大提高,內存的發展已經跟不上CPU訪存的速度。在2001 – 2005

2023-03-21 14:34:53 755

755

在學習Spring Cache之前,筆者經常會硬編碼的方式使用緩存。

2023-05-11 17:40:23 350

350

按照數據關系劃分:Inclusive/exclusive Cache: 下級Cache包含上級的數據叫inclusive Cache。不包含叫exclusive Cache。舉個例子,L3 Cache里有L2 Cache的數據,則L2 Cache叫exclusive Cache。

2023-05-30 16:02:34 418

418

build_mem_type_table()函數的功能是獲取當前CPU的CACHE類型,據此初始化mem_type。

2023-06-05 15:03:49 816

816

? CACHE 的一致性 Cache的一致性有這么幾個層面 1.?????一個CPU的icache和dcache的同步問題 2.?????多個CPU各自的cache同步問題 3.?????CPU

2023-06-17 10:38:26 911

911

Cache對性能的影響首先我們要知道,CPU訪問內存時,不是直接去訪問內存的,而是先訪問緩存(cache)。 當緩存中已經有了我們要的數據時,CPU就會直接從緩存中讀數據,而不是從內存中讀。 CPU

2023-10-04 15:31:00 395

395

LRU(Least Recently Used)算法:該算法會跟蹤每個cache line的age(年齡)情況,并在需要時替換掉近期最少使用的cache line。

2023-10-08 11:10:05 433

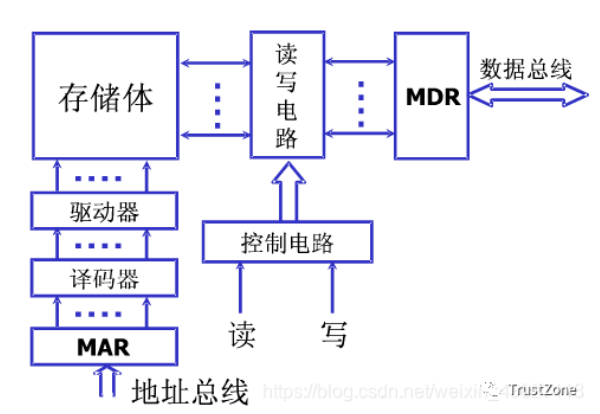

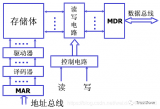

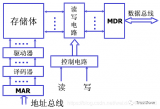

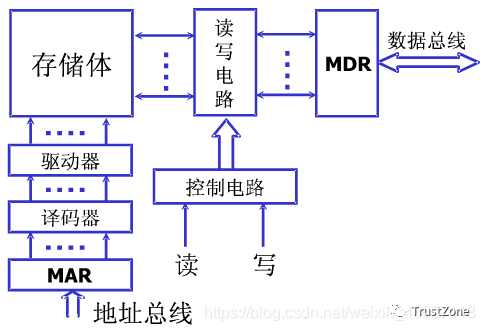

433 Cache是位于CPU與主存儲器即DRAM(Dynamic RAM,動態存儲器)之間的少量超高速靜態存儲器SRAM(Static RAM),它是為了解決CPU與主存之間速度匹配問題而設置的,不能由用戶直接尋址訪問。

2023-10-17 10:37:47 451

451

在cache存儲系統中,把cache和主存儲器都劃分成相同大小的塊。 主存地址由塊號B和塊內地址W兩部分組成,cache地址由塊號b和塊內地址w組成。 當CPU訪問cache時,CPU送來主存地址

2023-10-31 11:21:36 453

453 根據不同的分類標準可以按以下3種方法對Cache進行分類。 ?1)數據cache和指令cache ?● 指令cache:指令預取時使用的cache。 ?● 數據cache:數據讀寫時使用的cache

2023-10-31 11:26:31 371

371

“鎖定”在cache中的塊在常規的cache替換操作中不會被替換,但當通過C7控制cache中特定的塊時,比如使某特定的塊無效時,這些被“鎖定”在cache中的塊也將受到相應

2023-10-31 11:31:21 314

314 具有Cache的計算機,當CPU需要進行存儲器存取時,首先檢查所需數據是否在Cache中。如果存在,則可以直接存取其中的數據而不必插入任何等待狀態,這是最佳情況,稱為高速命中; 當CPU所需信息不在

2023-10-31 11:34:46 403

403

提高高速緩存命中率的最好方法是盡量使Cache存放CPU最近一直在使用的指令與數據,當Cache裝滿后,可將相對長期不用的數據刪除,提高Cache的使用效率。 為保持Cache中數據與主存儲器中數據

2023-10-31 11:43:37 532

532 Cache和存儲器一樣具有兩種基本操作,即讀操作和寫操作。當CPU發出讀操作命令時,根據它產生的主存地址分為兩種情形:一種是需要的數據已在Cache中,那么只需要直接訪問Cache,從對應單元中讀取

2023-10-31 11:48:08 560

560 使用Cache的必要性 所謂Cache即高速緩沖存儲器,它位于CPU與主存即DRAM之間,是通常由SRAM構成的規模較小但存取速度很快的存儲器。 目前計算機主要使用的內存為DRAM,它具有價格

2023-10-31 11:53:54 334

334

電子發燒友App

電子發燒友App

評論