引言

隨著現代科學技術的發展,頻率及時間的測量以及它們的控制技術在科學技術各領域,特別是在計量學、電子技術、信息科學、通信、天文和電子儀器等領域占有越來越重要的地位。從國際發展的趨勢上看,頻率標準的準確度和穩定度提高得非常快,幾乎是每隔6至8年就提高一個數量級。本系統采用DSP的數值控制方式是目前設計控制系統的發展趨勢,這種基于DSP的控制系統能夠用軟件實現復雜的算法,而不需要復雜的模擬電路,具有軟硬件模塊化、測量功能可重組/可選擇的特點。該系統采用TI公司推出的150MHz高速處理能力的高精度定點數字信號控制器TMS320F2812芯片,其豐富的片內資源可以大大簡化硬件電路的設計,有利于提高系統的可靠性,其高效的32位CPU內核、支持浮點運算等特點,為提高系統的測量精度奠定了基礎。該系統具有精度高、實時性好、使用方便、測量迅速,以及便于實現測量過程自動化等優點。

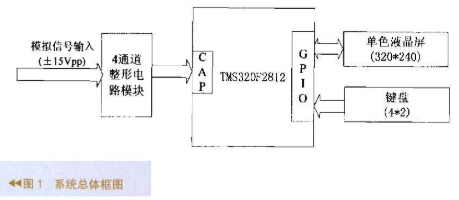

系統總體設計方案

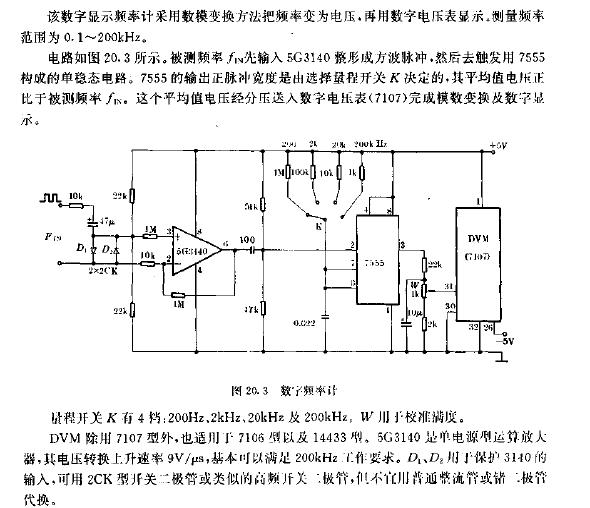

本嵌入式數字頻率計的硬件電路主要包含4個部分:4通道整形電路模塊,TMS320F2812數字信號處理模塊,單色液晶屏模塊(CM320*240)和4*2矩陣鍵盤模塊。系統總體框圖如圖1所示。

4通道整形電路模塊:完成模擬信號整形、衰減功能 。

TMS320F2812數字信號處理模塊:完成軟件濾波,多周期同步測頻算法等。

單色液晶屏模塊:實時顯示瞬時捕獲的頻率值,同時配合鍵盤進行儀表參數設置。

4*2矩陣鍵盤模塊:系統命令的形成與其它參數的輸入設置。

信號處理過程:在鍵盤控制下,TMS320F2812根據4*2鍵盤發出的命令實時地將要轉換的模擬信號經過電壓比較器形成的方波信號直接輸入捕獲單元的輸入引腳,再通過軟件濾波將捕獲到的數據經過多周期同步測量算法處理后直接送到單色液晶屏顯示,當再次進行通道選擇時,可通過鍵盤進行實時調整。

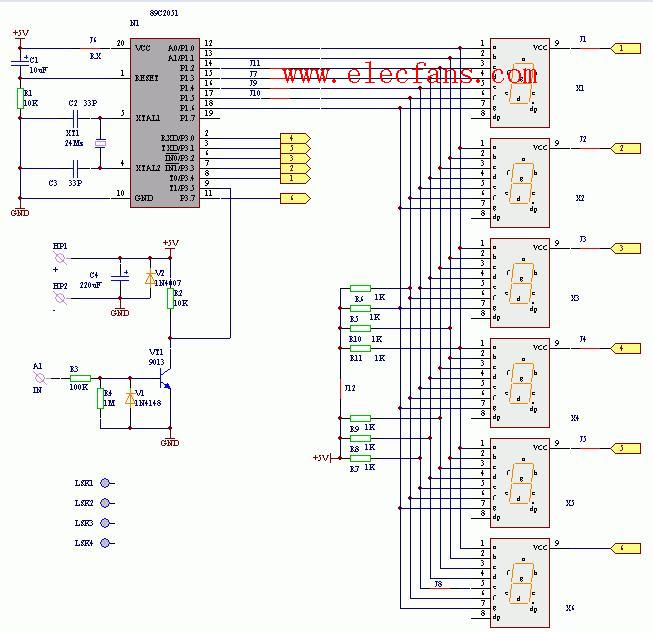

系統硬件設計

本系統在綜合考慮各種硬件條件下,設計出如圖2的系統硬件連接圖。

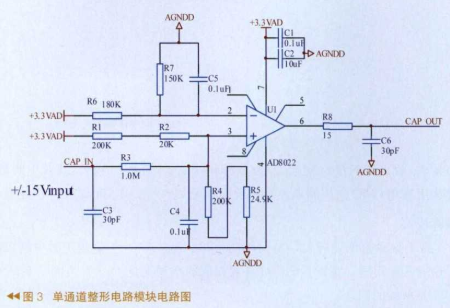

通道整形電路模塊

利用TMS320F2812的捕獲單元設計出硬件測頻電路。由于CAP模塊只能捕獲0V~3V的外界模擬方波信號,模擬信道必須將要轉換的模擬信號轉換后才能輸入CAP模塊。本系統采用ADI公司的AD8022作為前端模擬處理。

AD8022是一款性能優良、價格低廉、具有低噪聲和低失真特性的高性能8引腳雙運算放大器。其內部電路輸入級是NPN差分對,與之對應的后面驅動是PNP對,輸出緩沖級是工作在AB類的放大的射頻跟隨器。當閉環增益提高時,AD8022可驅動更大的容性負載,輸出不會產生震蕩。

本系統采用開環方式實現電壓比較器,可以將-15V~+15V的外界模擬信號,經過電壓求和電路輸出0V~3V的模擬信號(即圖3中的引腳3處),為抑制共模抑制比將其輸入到同相端,而在反相端輸入+1.5V的比較電平,這樣,在輸出端即引腳6處可得到占空比為50%的方波,其中電容C5起抑制高頻噪聲的作用。單通道整形電路模塊電路圖如圖3所示。

單色液晶屏模塊

CM320240是一種圖形點陣液晶顯示器,主要采用動態驅動原理由行驅動控制器和列驅動控制器兩部分組成了320(列)×240(行)的全點陣液晶顯示,此顯示器內含了硬件字庫,編程模式簡潔方便。

該液晶模塊的讀寫周期最小為800ns。如果采用總線方式控制液晶模塊,TMS320F2812讀、寫周期最大值為200ns,不能滿足該液晶模塊的要求,故采用間接控制方式。為節約硬件成本,該系統選用通用GPIO來控制液晶屏的讀寫信號。

鍵盤模塊

由于鍵盤是低速外設,與TMS320F2812連接時存在速度匹配問題。為此,設計時設置相應的全局變量實現與系統的同步。

本系統將鍵盤分為二類:通道選擇鍵(3個)與系統鍵(4個)。通道選擇鍵主要完成系統單通道、雙通道、四通道模式的設定;系統鍵包括停止鍵(停止觀察顯示的頻率)、返回鍵(通道選擇的重新設定)、UP鍵和DOWN鍵(選擇捕獲單元硬件連接方式)。

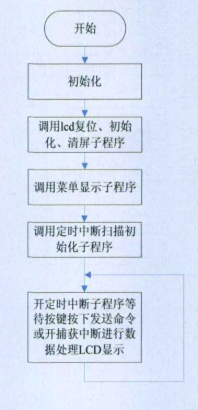

軟件設計

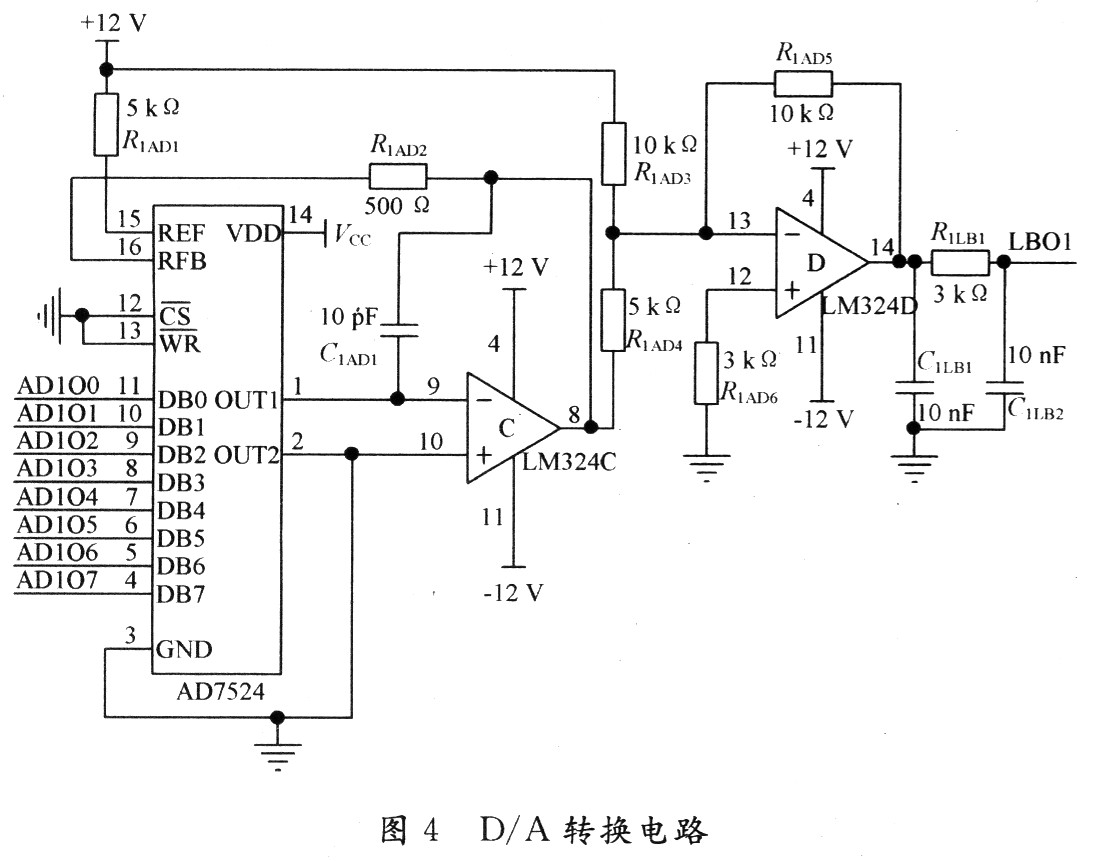

系統軟件設計是本系統的重點,主要包括三部分內容:捕獲中斷測頻子程序、鍵盤定時中斷掃描子程序和LCD顯示處理子程序。系統軟件總體流程圖如圖4所示。

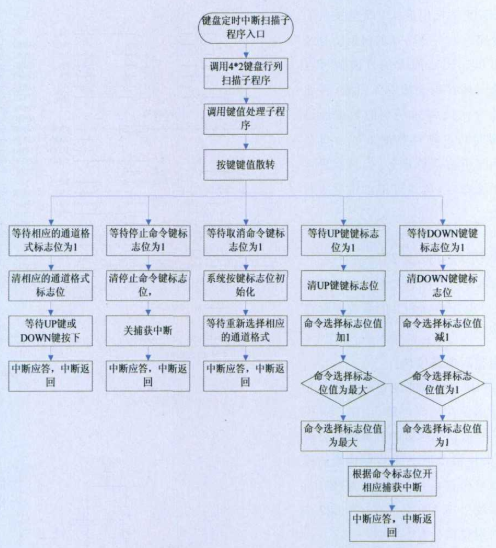

鍵盤定時中斷掃描

為滿足系統實時性要求、完成鍵盤操作的實時響應,本系統設置了一個5ms的時基,采用事件管理器的EVB的time4定時周期中斷來完成。對鍵盤掃描、命令形成與標志位設置功能,都在定時器中斷服務子程序完成。鍵盤定時中斷掃描流程圖如圖5所示。

捕獲中斷測頻

本系統使用TMS320F2812事件管理器模塊的捕獲單元來測頻,捕捉被測信號的有效電平跳變沿,由內部的計數器記錄一個周波內標頻脈沖個數,并通過相應的運算來得到被測頻率的大小。此模塊主要包括捕獲與定時的初始化設置與捕獲中斷子程序兩部分。

捕獲中斷測頻子程序的部分代碼如下:

(1)void InitEv1(void)//捕獲1初始化設置

{

EALLOW;

SysCtrlRegs.HISPCP.all = 0x00;// 外設高速時鐘

EDIS;

EvaRegs.CAPCONA.bit.CAP1EDGE=1; //檢測上升沿,計算周期脈沖寬度

EvaRegs.CAPFIFOA.bit.CAP1FIFO=0; //CAP1FIFO空

EvaRegs.CAP1FBOT=0;//棧底清零

EvaRegs.CAP1FIFO=0;

EvaRegs.EVAIFRC.bit.CAP1INT=1;//清捕獲中斷1標志位

EvaRegs.EVAIMRC.bit.CAP1INT=1; //捕獲1中斷使能

}

(2)interrupt void CAPINT1_isr(void)//捕獲中斷1子程序

{

CAP1_t1=EvaRegs.CAP1FIFO;//

CAP2_t1=EvaRegs.CAP1FIFO;

if(CAP2_t1》CAP1_t1)

temp1=CAP2_t1-CAP1_t1;

else

temp1=CAP2_t1+EvaTimer1InterruptCount*65535-CAP1_t1;

f1= 1171875.0/(float)temp1;

value=f1;

fpart = modf(value, &ipart);

a1=(long)ipart;//獲得頻率的32位整數

*(Uint16 *)0x80008=a1&0x0ffff;//獲的低16位

*(Uint16 *)0x80009=(a1&0xffff0000)》》16;//獲的高16位

EvaRegs.EVAIFRC.bit.CAP1INT=1;//清捕獲中斷1標志位

EvaRegs.EVAIMRC.bit.CAP1INT=1; //捕獲1中斷使能

PieCtrlRegs.PIEACK.bit.ACK3 = 1;//開外設中斷應答

}

LCD顯示處理

LCD的顯示分為信息區與顯示區兩部分。其中信息區包括固定信息(顯示煙臺大學DSP實驗室等),顯示區包括通道號信息與各通道的頻率值信息的顯示。本模塊主要包括LCD的初始化設置與頻率值的顯示等子程序。

實驗結果

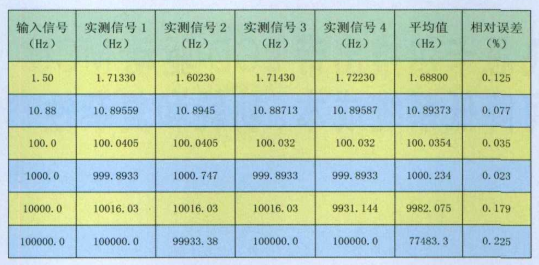

本系統測試了如表1中的6組數據,并做出了誤差分析。輸入信號頻率與實測信號頻率如表1所示。

誤差分析:本系統的誤差主要來自如下兩個方面,即計數脈沖和門控信號不同步以及晶振不穩定。

結束語

本文設計了一種具有高精度和簡單結構特點的測頻系統,由于在實現上簡單,可以滿足低成本的要求,使測頻電路大為簡化,便于工程應用,具有較大的應用價值。

經過反復測試后得出:系統的測頻誤差可達到0.1%,由于采用了實時的鍵盤定時中斷掃描,可以較好地滿足實時性要求。

責任編輯:gt

電子發燒友App

電子發燒友App

評論