DSP是對數字信號進行高速實時處理的專用處理器。在當今的數字化的背景下,DSP以其高性能和軟件可編程等特點,已經成為電子工業領域增長最迅速的產品之一,人們對其性能、功耗和成本也提出了越來越高的要求,迫使DSP廠商開始在單一矽片上集成更多的處理器內核。本文分析了多核DSP必須面臨的挑戰,介紹了一些常見的多核DSP產品。

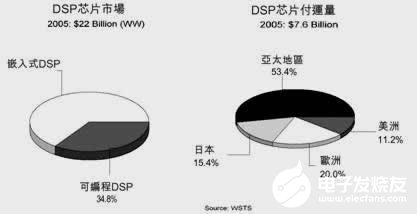

數字信號處理器(DSP)是對數字信號進行高速實時處理的專用處理器。在當今的數字化的背景下,DSP以其高性能和軟件可編程等特點,已經成為電子工業領域增長最迅速的產品之一。據市場研究公司In-Stat的最新報告,全球DSP市場今後將一直保持高速增長,其中2004年的付運量估計為15億顆,2009年該數字可望達到28億顆。其中,浮點DSP的應用市場可望從2004年的10億美元增長到2009年的22億美元。因此,全球DSP市場的前景非常廣闊,DSP已成為數字通信、智慧控制、消費類電子產品等領域的基礎器件,而通信市場2009年的比例可望達到61%。

Forward Concepts公布的DSP/無線市場報告指出,Q2/2006 DSP晶片付運量較Q1上升了3.3%,達21億美元。報告指出,雖然無線依然主宰著DSP市場72%的份額,其Q2增長幅度僅有2.8%,而來自汽車和消費領域的增長則分別高達38.7%和37.2%。數據顯示,亞太地區依然是DSP的主要應用市場,而嵌入式DSP則占據了66%以上的市場份額。

圖1 DSP市場概況

隨著應用領域的擴大以及終端產品性能的日益豐富,人們對DSP系統的性能、功耗和成本提出了越來越高的要求,迫使DSP廠商開始在單一矽片上集成更多的處理器內核,於是多核DSP應運而生。

1、多核DSP關鍵技術

晶片制造工藝技術的進步和SoC設計與驗證水準的提升分別是多核DSP誕生的硬體基礎和軟件基礎。

目前,DSP巨頭德州儀器公司(TI)的DSP晶片生產工藝已經達到75nm水準,能夠在一塊僅有拇指大小的單晶片上集成8個TMS320DSP內核。同時,多核DSP也離不開SoC設計水準的進步。SoC設計可以對整個系統的模型演算法、軟硬體功能、晶片結構、各電路模塊直至器件的設計進行綜合考慮,可以在同樣的工藝條件下,實現更高性能的系統指標。

以下介紹多核DSP必須面對的一些關鍵技術∶軟硬體協同設計、軟硬體協同驗證、IP核生成與復用、高速互連總線、低功耗設計等。

(1)低功耗

多核DSP帶來了更高的性能,但它相比傳統的單核DSP也帶來了更大的功耗。嵌入式應用,例如手機、數碼相機等對功耗非常敏感。在以前的2G通信時代,人們習慣了200小時待機時間的手機,當然很難接受待機時間僅僅為一天的3G手機。因此多核DSP必須解決的第一大技術難題就是如何有效的降低平均功耗。

從硬體技術上來看,可以采用動態電源管理技術,設置全速、半速、休眠等工作模式,根據當前的任務強度和功耗監測信息,及時調整電壓和頻率,關閉暫時不使用的模塊,以降低功耗。另外,根據特定的應用需求,設置專門的協處理器,同樣可以減少DSP內核的運算強度。

從軟件技術上來看,在編譯指導下的多核DSP低功耗優化技術非常具有潛力。低功耗編譯技術主要包括編譯指導的動態電壓調節、多線程功耗模型下的低功耗編譯調度等。在操作系統的支持下,通過合理的調度,使處理器資源與演算法需求相適應,例如在DSP核+MCU的模式下,MCU就不應該處理DSP的有關程式。

(2)互連與存儲系統

隨著晶片面積的增大,長線互連延遲和信號完整性已經成為制約晶片主頻的關鍵因素。當片上DSP核較少時,可用簡單的總線結構或者Crossbar互連;當DSP核較多時可用二維mesh網絡、3D Toru s等進行互連,設計者必須在網絡開銷以及多核之間耦合的程度之間進行權衡,同時還要注意互連拓撲的可擴展性。為提高互連性能,應該采用高頻、高帶寬的超深亞微米片上互連結構,以便高效地實現節點間通信。

針對數據密集型的應用,多核DSP必須解決存儲系統的效率問題。為此,必須要解決一系列關鍵技術,例如應該設計多大的片內存儲器?數據的共用和通信在存儲層次的哪一級來完成?Cache一致性在哪一級實現更合理?是通過片內共用存儲器還是高速總線進行多核之間的通信?存儲結構如何支持多線程的應用?

(3)編譯技術與操作系統

多核DSP能否發揮最高的性能,在很大程度上取決於編譯優化和嵌入式操作系統的有力支持。例如,多核DSP對多線程程式能夠提供較高的性能,但是對于單線程應用的性能反而不高,甚至比單核DSP的性能還要低。

采用硬體動態提取線程是一種方法,但編譯器更要擔負起自動并行化的工作,即將串列程式自動地轉換為等價的多線程并行代碼,使用戶不關心疊代空間劃分、數據共用、線程調度和同步等細節,減輕用戶負擔。 更重要的是多線程優化編譯技術,包括線程并發機制的實現、線程調度、線程級前瞻執行等技術。

多核之間的任務調度是充分利用多處理器性能的關鍵。為滿足實時處理的要求,均衡各處理器負載,需要研究的任務調度機制有分散式實時任務調度演算法、動態任務遷移技術等。已有的幾種嵌入式操作系統,例如μcLinux、PalmOS、WinCE等,都還無法有效地支持多核處理器。嵌入式多核操作系統的研究任重而道遠。

(4)應用開發環境

嵌入式應用的特點決定了開發人員必須能夠在很短的時間內推出能夠為市場所接受的應用系統。為此,多核DSP供應商必須為用戶提供簡便易用的開發、調試環境。但是面向多核處理器的編程環境始終是不成熟的,并行程式開發技術一直難以普及。

為此,我們可以借鑒多核通用微處理器的編程模式,即消息傳遞程式設計模式MPI和基於編譯指導命令的程式設計模式OpenMP。但是,最終的發展趨勢還將是集成化的VSP(Virtual Single Processor,虛擬單處理器模型)開發環境,在這一環境下用戶能夠像開發單處理器程式一樣去開發多核應用系統,在同一平臺上完成編程、調試、編譯優化和連機測試的過程。

例如,Cradle公司在推出CT3600系列多核DSP的同時,還推出了相應的多核開發工具,包括ANSI C編譯器、針對DSP進行了時序優化的Cradle C語言、eCOS實時操作系統、INSPECTORTM代碼開發與調試器和RDS3600硬體開發平臺等,從而為用戶提供了一攬子的解決方案。

2、多核DSP的應用

(1)3G移動通信

多核DSP最重要的應用領域之一就是3G數字移動通信。其中包括基站和移動終端兩方面的應用。基站所使用的DSP更注重高性能,對成本和功耗不是非常敏感。而移動終端要面向具體的用戶,設計時必須在功能、功耗、體積、價格等方面進行綜合考慮,因此移動終端對DSP處理器的要求更加苛刻。

2G數字蜂窩電話的核心處理器都是基於雙處理器結構的,即包含1個DSP和1個RISC微控制器(MCU)。DSP用來實現通信協議棧中物理層協議的功能;而MCU則用來支援用戶操作介面,并實現上層通信協議的各項功能。

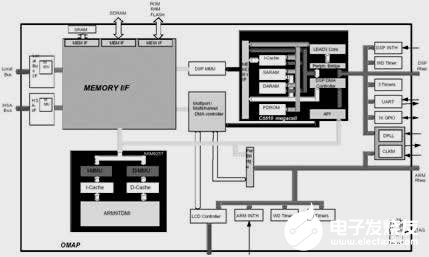

3G數字移動通信標準增加了通信帶寬,并更加強調高級數據應用,例如可視電話、GPS定位、MPEG4播放等。這就對核心處理器的性能提出了更高的要求,即能夠同時支持3G移動通信和數據應用。在現代化的3G系統中,對處理速度的要求大概要超過60-130億次每秒運算。如果用現有的DSP,需要20-80片低功耗DSP晶片才能滿足要求。因此,承擔這一重任的多核DSP處理器晶片必須在功耗增長不大的前提下大幅度提高性能,并且要具備強大的多任務實時處理能力。多核DSP在嵌入式操作系統的實時調度下,能夠將多個任務劃分到各個內核,大大提高了運算速度和實時處理性能。這些特點將使3G手機能夠同時支援實時通信和用戶互動式多媒體應用,支援用戶下載各種應用程式。圖2給出了一種3G通信多核DSP處理器的架構。

圖2 3G通信多核DSP處理器架構

(2)數字消費類電子

DSP是數字消費類電子產品中的關鍵器件,這類產品的更新換代非常快,對核心DSP的性能追求也無越來越苛刻。

由於DSP的廣泛應用,數字音響設備得以飛速發展,帶數碼控制功能的多通道、高保真音響逐漸進入人們的生活。此外,DSP在音效處理領域也得到廣泛采用,例如多媒體音效卡。在語音識別領域,DSP也大有用武之地。Motorola公司等廠商正在開發基於DSP的語音識別系統。

數字視頻產品也大量采用高性能DSP。例如數碼攝像機,已經能夠實時地對圖像進行MPEG4壓縮并存儲到隨機的微型硬盤甚至DVD光碟上。

此外,多核DSP還應用在視頻監控領域。這類應用往往要求具有將高速、實時產生的多路視頻數字信號進行壓縮、傳輸、存儲、重播和分析的功能,其核心的工作就是完成大數據量、大計算量的數字視頻/音頻的壓縮編碼處理。

(3)智慧控制設備

汽車電子設備是這一領域的重要市場之一。現代駕乘人員對汽車的安全性、舒適性和娛樂性等要求越來越高。多核的DSP也將逐漸進軍這一領域。例如在主動防御式安全系統中,ACC(自動定速巡航)、LDP(車線偏離防止)、智慧氣囊、故障檢測、免提語音識別、車輛資訊記錄等都需要多個DSP各司其職,對來自各個傳感器的數據進行實時處理,及時糾正車輛行駛狀態,記錄行駛信息。

3、主流多核DSP介紹

(1)同構多核DSP

這類多核DSP內部集成了若干個結構對等的DSP核,不存在其他處理器核。

A、AD公司Blackfin系列

AD公司Blackfin系列采用雙Blackfin內核(每個內核性能高達756MHz/1512 MMAC,總和達到3024 MMAC),適用於要求苛刻的數字成像和消費類多媒體應用;其328KByte的大片上存儲器可以用作每個內核單獨的L1存儲器系統,以及共用的L2存儲器空間。

圖3 Blackfin系列雙核DSP功能圖

該處理器采用類RISC的寄存器和指令模式,易於編程和編譯優化,同時具有先進的跟蹤、調試和性能監測方式。Blackfin內核采用動態功耗管理技術,可以改變電壓和頻率,從而為便攜式應用提供更長的待機時間,面向應用的外設提供了與多種音頻/視頻轉換器和通用ADC/DAC的無縫連接。

Blackfin系列的主要應用包括∶數碼相機、數碼攝像機、便攜式媒體播放機、數字視頻錄像機、機頂盒、消費類多媒體、汽車可視系統、寬帶無線系統。

B、TI公司TMS320VC5441

TI公司的TMS320VC5441浮點DSP內部集成了4個C54x核,每個核具有192KB的局部存儲器、3個多通道緩沖串口、DMA、定時器等部件。每個子系統都具有獨立的程式和數據空間,可以同時訪問指令和數據。該DSP采用了很多并行訪存指令,可以在一拍內完成2讀 1寫操作,從而大大提高了并行性。片內共用512KB的程式存儲器。圖4給出了該DSP的組成結構。

圖4 TMS320VC5441功能圖

C、飛思卡爾MSC8144

飛思卡爾半導體第三代多核DSP——MSC8144基於下一代SC3400 StarCore技術。這款DSP面向下一代有線和無線基礎設施應用,提供語音、視頻和數據服務,并帶來領先的性能和低系統成本以及顯著提高的通道密度。

圖5飛思卡爾MSC8144功能圖

MSC8144將4個頻率為1GHz的StarCore DSP內核相集成,提供業界最高的千兆赫茲級性能,相當於1個4GHz單核DSP。它在單個產品中集成業界最高的10.5MB嵌入式存儲器,實際上降低了對附加外部存儲器的需求,同時保持具有競爭力的成本和每通道功耗。

MSC8144 DSP基於具有更深流水線的增強型SC3400 DSP內核,該內核能夠提供很高的時鐘速率,并增加了新的單指令多數據(SIMD)指令,提供精確的異常和分支預測。SC3400內核還支持適用於維特比(Viterbi)和視頻演算法的經過改進的專用指令,每個內核周圍都有高效的16KB指令緩存、32KB數據緩存,以及用於存儲和任務保護的MMU(存儲管理單元),使用戶能夠開發強大的軟件。

飛思卡爾的CodeWarrior集成開發環境(IDE)包括高級優化C/C++編譯程式、整合工具、周期和指令精確模擬器、設備驅動和操作系統。該工具箱還帶有一整套硬體開發平臺和參考板設計。同時,OEM還可以注冊購買飛思卡爾及其第三方生態系統合作夥伴的優化多媒體編解碼器和軟件框架。

MSC8144 DSP的主要特性包括∶2個千兆乙太網介面,支援SGMII和RGMII,另外還有16位元UTOPIA介面,支援ATM;QUICC Engine技術實施了雙RISC內核,可以降低DSP內核的通信任務負荷,從而增強整體系統性能;4X/1X Serial RapidIO介面,提供高吞吐量和強大數據包傳輸;2048 TDM DS-0通道,處理與PSTN網絡的連接;10.5M內部存儲器,提供業界最大的嵌入式存儲器;高級DDR-I/II控制器,提供連接高速行業標準存儲器的介面;66MHz的32位元PCI總線介面,提供更多的高速連接。

在有線基礎設施應用方面,MSC8144提供了運營商級中繼、企業VoIP媒體網關、視頻會議服務器等眾多應用的DSP解決方案。另外,MSC8144提供的無線應用包括∶無線語音代碼轉碼,IP多媒體子系統(IMS)網關,視頻多點會議,3G、Super 3G和WiMax基站的基帶卡以及無線網絡控制器(RNC)中的第2層處理。

(2)異構多核DSP

異構多核DSP是最常見的一類多核DSP,其中既包含DSP核,又包含用於控制的MCU(微控制器)核,從而充分發揮DSP的處理速度和MCU的控制功能。

A、TI公司SMJ320C80

TI公司的SMJ320C80是世界上第一個單晶片并行MIMD(多指令多數據)DSP。其中集成了一個性能為100MFLOPS的32位RISC浮點CPU核、4個32位并行處理DSP、一個傳輸控制器(TC)、一個視頻控制器(VC)。所有的處理器通過Crossbar進行耦合,共用50KB的片上RAM,每秒可以完成20億次運算。該處理器主要面向軍用領域。

TI公司的OMAP處理器是這類DSP的典型代表。圖6給出了最新推出的OMAP2420的組成結構。該處理器采用90nm工藝,集成了主頻為330MHz的ARM1136核、TMS320C55x DSP核、2D/3D圖形加速器、圖像與視頻加速器、共用存儲控制器/DMA等,能夠實現30幀每秒VGA解析度的全動態視頻編解碼。

圖6 TI公司OMAP處理器的硬體結構

B、Cradle公司CT3616

Cradle公司是DSP領域的後起之秀,其高性能CT3616處理器內部集成了16個DSP核與8個GPP(通用處理器)核,主頻375MHz,能夠進行16路MPEG4 SP@L3實時編碼,最高DSP性能達到96G MAC運算。可編程I/O是該處理器的另外一大特色,共有144個可編程的I/O引腳,允許用戶自定義介面。該處理器集成的DDR DRAM介面可以掛接333MHz的DDR存儲器。全晶片的功耗僅僅為4.5W,可以應用於音頻/視頻編碼、多路監控、系統控制等領域。

C、瑞薩半導體SuperH系列

瑞薩科技SuperH系列集成了32位元SH-2A CPU核心的DSP產品可用於工業、辦公自動化和消費電子應用的設備控制。由於SH-2A CPU核心與SH-2保持指令的向上相容性,可提供更高的處理性能和ROM編碼效率,可以滿足市場對更高性能的需求。

圖7 瑞薩科技SH-2A核心架構

其中,最近發布的帶有片上閃存的SH7211F集成了可提供卓越實時控制能力的高性能SH-2A CPU核心,在160MHz運行條件下可以實現大約320 MIPS(每秒百萬指令)的高處理性能。與SH-2 CPU核心相比,在同樣的工作頻率下其處理性能大約提高了1.5倍,與運行於80MHz最高工作頻率的SH-2產品相比,性能大約提高了3倍。其指令集的向上相容性保證了可使用現有的程式,同時可以提高大約25%的ROM編碼效率,并可減少存儲程式的存儲器容量。

SH-2A CPU核心在實時能力也有所改進。15個寄存器組專門用於CPU的中斷,中斷處理的反應周期已從SH-2的37個周期減少到SH-2A的6個周期。由於更高的工作頻率和更短的反應周期,在160MHz工作條件下運行的SH-2A的程式開始反應時間的中斷信號已減少到在80 MHz條件下運行的SH-2反應時間的大約1/12。這樣,就可以在中斷事件發生時,實現快速的程式切換,從而提供高質量的實時控制。

SH7211F還包括了適用於諸如AC伺服系統和變頻器等強調實時控制能力的高檔工業設備的各種外設功能。這些功能是具有3相PWM(脈沖寬度調制)輸出能力的、8個12個位A/D轉換器通道,以及2個8位D/A轉換器通道變頻設備使用的MTU2和MTU2S電機控制應用的理想選擇。其通信功能包括有助於外圍設備通信的I2C總線介面通道和具有16級FIFO的4通道串列通信介面。外部數據總線能夠支持閃存ROM、SRAM、SDRAM、突發ROM、多工I/O,這些都可以通過總線狀態控制器進行設置,使各種存儲器能夠進行直接連接而無須使用外部元件。

D、picoChip公司picoArray多重核心處理器

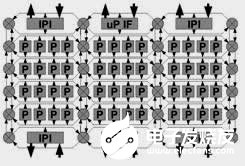

picoChip針對新一代無線系統的picoArray多重核心處理器陣列元件——PC202、PC203及PC205為高整合度、高效能、低成本之DSP。三款元件均內建約200個以上的處理器,提供超過100GIPs與25GMACs的運算效能,大幅領先舊有的單核心DSP。

圖8 picoArray多重核心處理器陣列元件原理

其中,PC202與205亦內建一個性能強悍的ARM9處理器。所有新產品均采用標準C語言或組譯語言撰寫程式碼,讓客戶能利用其開發完整的軟體無線電系統,此外并針對WiMAX(16d與16e)以及WCDMA(包括HSDPA,并能升級至HSUPA)提供完整的參考設計方案。

PC202內建198個數位訊號處理器,以及一個負責控制與MAC功能的ARM 926EJ-S處理器,以鎖定各種追求低成本的應用,例如WiMAX客戶端系統與存取設備、以及WCDMA毫微微蜂巢式(家用基地臺)設備。

PC203內含248個處理器,系專為基地臺(BS)應用所設計,能協助業者開發出支援各種熱門無線通訊協定的產品,例如WiMAX與HSDPA/HSUPA,包括支援如MIMO與波束成型等先進演算法,C203尚能搭配外部控制處理器或網路處理器,開發出大型基地臺產品。

此三款晶片均內建加密引擎,針對高速傅立葉轉換/反向高速傅立葉轉換、Viterbi、以及渦輪高速解碼器(包括符合16e規格的CTC),此功能完全整合至picoChip的互連架構與開發環境,讓業者能輕易進行編程、整合、以及驗證。

另外,每個處理器均為功能完備的DSP,內含16x16乘數器與40位元累加器、內部指令與資料記憶體,采用一套改良式三路超長指令字元(LIW)架構,此意味著處理器可執行乘數-累加(MAC)指令,每個周期最多可處理三個其他指令。PC203與PC205內含的248個處理器,運作時脈達160MHz,即使在針對如Turbo與Viterbi解碼與加密作業時,亦能達到約160 GIPS的無線通訊加速效能。

(3)DSP核+協處理器

這類DSP一般針對某一類應用集成專用的協處理器,從而對DSP實現演算法加速。TI的研究表明,對於像MPEG4編解碼這樣的任務,使用協處理器可以降低50%的DSP負荷,從而平衡系統功耗。

A、TI公司的高性能數字信號處理器TMS320C6416

TI公司的高性能數字信號處理器TMS320C6416是這類多核DSP的典型代表。該DSP除了包含一個功能強大的C64x DSP核之外,還集成了一個維特比協處理器(VCP)和一個Turbo解碼協處理器。其中維特比協處理器用於語音和低碼率數據通道解碼,支持500個8Kb/s碼率的語音通道,并且可以對強制長度、碼率和幀長度等解碼參數進行編程。Turbo協處理器用於高碼率數據通道的解碼,支持35個384Kb/s碼率的數據通道。

B、飛思卡爾MSC8126

飛思卡爾半導體公司的MSC8126也是一個集成了協處理器的多核DSP。該DSP集成了4顆StarCore DSP核、一個Turbo協處理器、一個維特比協處理器、UART介面、4個TDM串列介面、32個通用定時器、乙太網介面及16通道DMA。

圖9飛思卡爾MSC8126內部功能

該DSP在最先進的90nm工藝下生產,在400MHz主頻下,其4個擴展內核可以達到最高每秒6400MMAC(百萬次乘加操作)的性能。除了每個DSP核內包含228KB的M1存儲器之外,片內還集成了476KB的共用M2存儲器。支援可變長指令是該DSP的另外一個特點。

4、DSP展望

Forward Concepts的Will Strauss表示∶DSP技術的演繹趨勢是多重核心處理器。未來10年,全球DSP產品將向著高性能、低功耗、加強融合和拓展多種應用發展,DSP晶片將越來越多地滲透到各種電子產品當中,成為各種電子產品尤其是通信類電子產品的技術核心,將會越來越受到業界的青睞。

據TI預測,到2010年,DSP晶片的集成度將會增加11倍,在單個晶片內將能集成5億蘋晶體管。目前DSP的生產工藝已開始從0.35mm轉向0.25mm、0.18mm,預計到2005年,DSP晶片的工藝將達到0.075mm的更高水準,屆時,將能夠在一塊僅有拇指大小的單個晶片上集成8個DSP內核。

責任編輯:gt

電子發燒友App

電子發燒友App

評論