DSP芯片的BootLoader程序用于實(shí)現(xiàn)用戶程序上電自舉,它有多種工作方式。上電自舉就是將用戶存放在片外的非易失性、慢速的存儲(chǔ)器中的程序裝載到片內(nèi)易失的、高速的存儲(chǔ)空間中,以保證用戶程序在DSP核內(nèi)的高速運(yùn)行。

多核DSP是指由多個(gè)獨(dú)立的DSP子核集成的DSP芯片,且所有DSP子核共享一套片外總線。由于每個(gè)DSP子核內(nèi)部都有其自身獨(dú)立的掩模BootLoader程序,當(dāng)DSP芯片上電或復(fù)位時(shí),所有DSP子核都將自行啟動(dòng)自身獨(dú)立的BootLoader程序,實(shí)現(xiàn)用戶程序的上電自舉。所以,多核DSP的BootLoader程序的實(shí)現(xiàn)方法與單核DSP的BootLoader程序的實(shí)現(xiàn)方法有較大的差異。為此,本文立足于實(shí)踐,以雙核DSP—TMS320VC5421的16位并行EPROM的BootLoader程序的工作方式為例,詳細(xì)闡述了多核DSP的BootLoader程序的實(shí)現(xiàn)方法。

1 BootLoader程序簡(jiǎn)介

1.1 BootLoader程序的四種工作方式

一般的DSP都采用常見的BootLoader程序工作方式來(lái)實(shí)現(xiàn)用戶程序的上電自舉:

·處理器通信口(主端口)HPI方式——通過(guò)DSP芯片與PC機(jī)或DSP芯片與其它DSP芯片之間的主機(jī)通信端口實(shí)現(xiàn)上電自舉;

·8位或16位并行EPROM方式——通過(guò)DSP內(nèi)核的DMA通道實(shí)現(xiàn)上電自舉;

·8位或16位并行I/O方式——通過(guò)DSP芯片的片外并行I/O接口實(shí)現(xiàn)上電自舉;

·8位或16位串行口方式——通過(guò)DSP芯片的串行端口實(shí)現(xiàn)上電自舉。

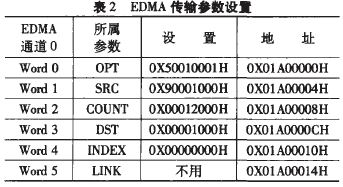

在以上四種工作方式中,最常用的是16位并行EPROM方式。即在DSP芯片上電或復(fù)位時(shí),通過(guò)DMA通道將存儲(chǔ)在核外EPROM中的程序以16位形式存儲(chǔ)到核內(nèi)的程序空間中。

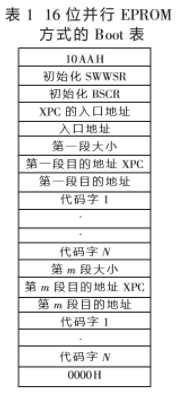

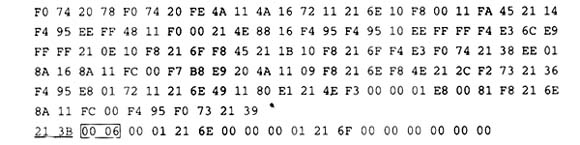

1.2 16位并行EPROM方式的Boot表

各種方式的BootLoader程序都有其固定格式的Boot表,用來(lái)實(shí)現(xiàn)用戶程序的上電自舉。16位并行EPROM方式的Boot表如表1所示。表中的第1表項(xiàng)存放BootLoader程序工作方式控制字,用于DSP芯片上電或復(fù)位時(shí)確認(rèn)該Boot表是否為16位并行EPROM工作方式的Boot表。該表項(xiàng)內(nèi)容為10AAH,表示DSP內(nèi)核認(rèn)為該Boot表是16位并行EPROM工作方式的BootLoader程序的Boot表;否則DSP內(nèi)核認(rèn)為該Boot表不是16位并行EPROM的方式的Boot表;第2表項(xiàng)存放DSP特殊寄存器SWWSR在上電或復(fù)位時(shí)被賦予的初始化數(shù)值;第3表項(xiàng)存放DSP特殊寄存器BSCR在上電或復(fù)位時(shí)被賦予的初始化數(shù)值;第4表項(xiàng)存放用戶程序?qū)⒁淮娣旁贒SP核內(nèi)程序空間的頁(yè)地址;第5表項(xiàng)存放用戶程序?qū)⒁淮娣诺紻SP核內(nèi)程序空間的頁(yè)內(nèi)偏移地址;從第6表項(xiàng)開始依次存放用戶程序第m段代碼的長(zhǎng)度N。用戶程序第m段代碼將要被存放到DSP核內(nèi)程序空間的頁(yè)地址,用戶程序第m段代碼將要被存放到DSP核內(nèi)程序空間的頁(yè)內(nèi)偏移地址,用戶程序第m段代碼的第1個(gè)字,第2個(gè)字,……,第N個(gè)字;Boot表的最后表項(xiàng)存放Boot表結(jié)束字0000H,表示Boot表到此結(jié)束。因此DSP內(nèi)核要實(shí)現(xiàn)BootLoader程序,在上電復(fù)位后首先要申請(qǐng)到片外數(shù)據(jù)、地址總線的控制權(quán),然后再根據(jù)Boot表完成用戶程序上電自舉過(guò)程。[page]

1.3 16位并行EPROM工作方式Boot表的生成

所有BootLoader程序所需的Boot表的數(shù)據(jù)結(jié)構(gòu)都是通過(guò)執(zhí)行包含-v548參數(shù)的鏈接命令和Hex500轉(zhuǎn)換命令的程序形成的。在鏈接過(guò)程中確定用戶程序和數(shù)據(jù)的存放地址,在Hex500轉(zhuǎn)換過(guò)程中定義BootLoader程序的工作方式和用戶程序執(zhí)行的入口地址等。

為了生成16位并行EPROM方式的Boot表,首先,在鏈接程序時(shí)必須設(shè)置-v548選項(xiàng);然后使用TI公司DSP開發(fā)工具自帶的HEX500.EXE文件,根據(jù)用戶的COFF格式的代碼生成Boot表中的相應(yīng)內(nèi)容。

HEX500.EXE可執(zhí)行文件一般使用以下幾種參數(shù):

(1) *.out : 用戶的COFF格式的程序;

(2) -e : 確定用戶程序的入口點(diǎn);

(3) -a : 以ASCII形式,根據(jù)用戶的*.out文件輸出對(duì)應(yīng)的HEX文件;

(4) -boot: 實(shí)現(xiàn)用戶程序的裝載;

(5) -bootorg : 確定生成哪種形式的Boot表;

(6) -memwidth: 確定引導(dǎo)方式的位數(shù);

(7) -O *.hex : 輸出的HEX文件的名稱。

例如:

hex500 ti.out /*根據(jù)ti.out文件生成Boot表*/

-e 0x4000 /*用戶程序的入口點(diǎn)為0x4000*/

-a /*以ASCII形式輸出HEX文件*/

-boot /*裝載用戶的程序ti.out*/

-bootorg PARALLEL

/*生成并行EPROM方式的Boot表*/

-memwidth 16 /*生成16位的Boot表*/

-o ti.hex /*生成的HEX文件名為ti.hex*/

執(zhí)行完該HEX500.EXE命令后,系統(tǒng)會(huì)創(chuàng)建一個(gè)文件名為ti.hex的ASCII文件,然后用戶根據(jù)ti.hex文件內(nèi)容對(duì)EPROM進(jìn)行編程就能產(chǎn)生上述的16位并行EPROM工作方式的Boot表.

2 多核DSP的BootLoader程序的實(shí)現(xiàn)

目前TI公司已經(jīng)不再局限于生產(chǎn)單核DSP。為了提高用戶程序運(yùn)行的效率,TI公司又推出了2核、4核等多核DSP。在實(shí)現(xiàn)多核DSP上電自舉時(shí),每一個(gè)子核都需要申請(qǐng)片外總線的控制權(quán)。對(duì)于單核DSP而言,只有一個(gè)DSP內(nèi)核,對(duì)應(yīng)一個(gè)BootLoader程序,DSP核可以永遠(yuǎn)擁有片外總線的控制權(quán)。但對(duì)于多核DSP而言,由于只有一套片外總線,所以片外總線的控制權(quán)不允許也不可能永遠(yuǎn)被其中的某一個(gè)DSP子核所擁有。因此,多核DSP需要片外總線仲裁機(jī)制,以避免片外總線沖突。

下面以雙核DSP—TMS320VC5421的16位并行EPROM方式的BootLoader程序?qū)崿F(xiàn)過(guò)程為例,詳細(xì)闡述多核DSP的BootLoader程序的實(shí)現(xiàn)。

2.1 TMS320VC5421結(jié)構(gòu)簡(jiǎn)介

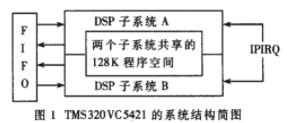

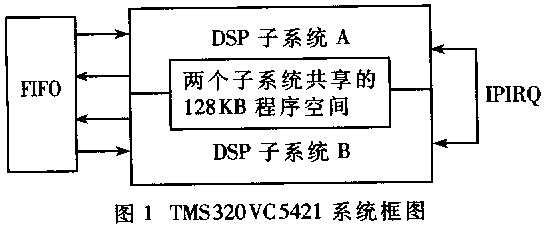

TMS320VC5421 16位定點(diǎn)雙核DSP,它集中了早期TMS320C54X系列DSP的優(yōu)點(diǎn),并提供了許多新的功能。其內(nèi)部結(jié)構(gòu)與TMS320C54X系列的其它款式DSP有很大的不同,其簡(jiǎn)單結(jié)構(gòu)框圖如圖1所示。

由于每個(gè)DSP子核的工作頻率是100MHz,所以它的工作速率可達(dá)到200MIPS,且它的每一個(gè)DSP子核都具備單核DSP(如TMS320VC5402)的所有特性。

2.2 TMS320VC5421的16位并行EPROM工作方式的BootLoader程序的選擇

TMS320VC5421的兩個(gè)DSP子核在DSP芯片上電或復(fù)位時(shí),能否啟動(dòng)各自的BootLoader程序以完成上電自舉功能,是由每個(gè)子核自身的XIO和GPIO0/ROMEN兩個(gè)管腳決定的。在DSP芯片上電或復(fù)位時(shí),每個(gè)DSP子核自動(dòng)檢測(cè)自身的XIO和GPIO0/ROMEN兩個(gè)管腳,如果對(duì)應(yīng)的XIO和GPIO0/ROMEN兩個(gè)管腳都為高電平,則啟動(dòng)自身的BootLoader程序完成用戶程序的上電自舉。[page]

每個(gè)DSP子核啟動(dòng)BootLoader程序后,采用哪一種BootLoader程序的工作方式是由各自的GPIO1管腳的狀態(tài)和各自以DMA方式從核外數(shù)據(jù)空間0000H地址單元讀入的數(shù)據(jù)決定的:檢測(cè)GPIO1管腳,如果GPIO1管腳為高電平,則采用串行口EEPROM的BootLoader工作方式,否則采用并行EPROM的BootLoader工作方式。若DSP子核的DMA通道讀入核外數(shù)據(jù)空間0000H單元中的數(shù)據(jù)為10AAH,則采用16位并行EPROM的BootLoader工作方式;若讀入的數(shù)據(jù)為xx08H或xxAAH,則采用8位并行EPROM的BootLoader工作方式。否則將重新判斷GPIO1管腳的電平,進(jìn)入死循環(huán)。

2.3 TMS320VC5421的BootLoader程序片外總線沖突的解決

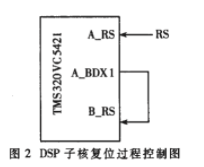

DSP核的BootLoader程序總是在DSP核上電或復(fù)位時(shí)啟動(dòng),且一啟動(dòng)BootLoader程序,對(duì)應(yīng)的DSP核就要申請(qǐng)核外的總線控制權(quán)。因此為了避免多核DSP的各個(gè)DSP子核啟動(dòng)BootLoader程序時(shí)引起的片外總線沖突,可通過(guò)控制每個(gè)DSP子核的復(fù)位過(guò)程,使每個(gè)DSP子核在不同的時(shí)間內(nèi)啟動(dòng)自身的BootLoader程序來(lái)解決片外總線沖突的問(wèn)題。

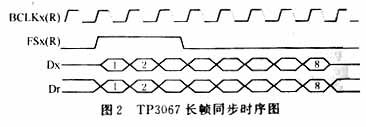

為了實(shí)現(xiàn)兩個(gè)DSP子核復(fù)位過(guò)程的分離,應(yīng)采用如圖2所示的DSP子核復(fù)位過(guò)程控制方法。

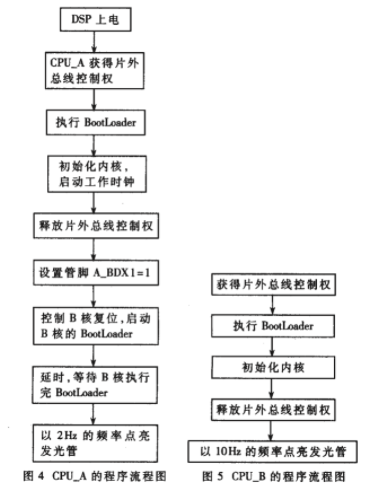

由于TMS320VC5421中A核擁有倍頻的鎖相環(huán)電路,所以首先復(fù)位A核,啟動(dòng)A核的BootLoader程序,實(shí)現(xiàn)A核的用戶程序上電自舉。然后再由A核的用戶程序控制B核的復(fù)位過(guò)程,啟動(dòng)B核的BootLoader程序,實(shí)現(xiàn)B核的用戶程序上電自舉。

在A核的BootLoader程序執(zhí)行完后,A核就會(huì)執(zhí)行自身的用戶程序代碼。A核的用戶程序代碼釋放片外總線的控制權(quán),并且控制B核的復(fù)位管腳,促使B核啟動(dòng)自身的BootLoader程序。如果此時(shí)A核中的用戶代碼又申請(qǐng)片外總線控制權(quán)或正在使用片外總線,就會(huì)造成片外總線沖突。解決此沖突的辦法有如下兩個(gè):

·粗略估計(jì)B核的BootLoader程序執(zhí)行時(shí)間,在A核的有效程序代碼前加一個(gè)延遲程序。

·在A核的有效程序代碼前加入一個(gè)死循環(huán)程序,當(dāng)B核BootLoader程序執(zhí)行完后,B核通知A核,A核就跳出這個(gè)死循環(huán)程序,開始執(zhí)行自己的有效代碼。

2.4 TMS320VC5421的16位并行EPROM工作方式的BootLoader程序的編程實(shí)現(xiàn)

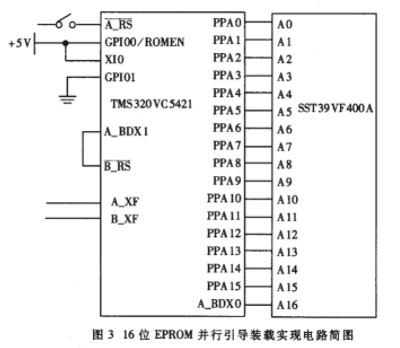

首先設(shè)計(jì)一個(gè)簡(jiǎn)單的電路圖,如圖3所示。在DSP的A_XF和B_XF兩個(gè)管腳分別連接一個(gè)發(fā)光二極管,A核以2Hz的頻率點(diǎn)亮發(fā)光二極管,B核以10Hz的頻率點(diǎn)亮發(fā)光二極管。將128K的FLASH(SST39VF400A)分成兩頁(yè),每頁(yè)為64K。FLASH的頁(yè)的選擇由TMS320VC5421的A_BDXO管腳控制。當(dāng)A_BDX0為低電平,即FLASH的A16地址線為低電平時(shí),選中FLASH的第一頁(yè),由FLASH的A0~A15地址線選擇頁(yè)內(nèi)地址,用于存放A核的16位并行EPROM工作方式的Boot表。當(dāng)A_BDX0為高電平,即FLASH的A16地址線為高電平時(shí),選中FLASH的第二頁(yè),由FLASH的A0~A15地址線選擇頁(yè)內(nèi)地址,用于存放B核的16位并行EPROM工作方式的Boot表。

CPU_A和CPU_B的程序流程圖分別如圖4和圖5所示。

(1)片外總線沖突的解決

估算B核執(zhí)行BootLoader程序所需的時(shí)間后,在A核的用戶有效程序之前,加一段延遲程序。

延遲的時(shí)間計(jì)算如下:

TMS320VC5421DSP的DMA通道從片外數(shù)據(jù)空間讀取一個(gè)字到片內(nèi)數(shù)據(jù)空間,需要7個(gè)指令周期時(shí)間。

統(tǒng)計(jì)用戶程序大小,將對(duì)應(yīng)Boot表中的所有段的大小相加:N1+N2+...=N。

延遲的時(shí)間為N×7=7N個(gè)指令周期。

由上面所述的方法可知,只需在開始執(zhí)行A核的有效程序之前加一段延遲7N個(gè)指令周期的代碼即可。

(2)生成Boot表

對(duì)CPU_A來(lái)說(shuō),以A核程序流程圖建立一個(gè)項(xiàng)目Ati.msk。產(chǎn)生Ati.out文件后,進(jìn)入該目錄的DOS環(huán)境,鍵入:

hex500 Ati.out-a-e 0x4000h-boot-bootorg PARALLEL-memwidth 16-romwidth 16-o Ati.hex

生成A核的16位并行EPROM工作方式的Boot表。

對(duì)CPU_B來(lái)說(shuō),同樣以B核程序流程圖建立一個(gè)項(xiàng)目Bti.msk。產(chǎn)生Bti.out文件后,進(jìn)入該目錄的DOS環(huán)境,鍵入:

hex500 Bti.out-a -e 0x4000h-boot-bootorg PARALLEL-memwidth 16-romwidth 16-o Bti.hex

生成B核的16位并行EPROM工作方式的Boot表。

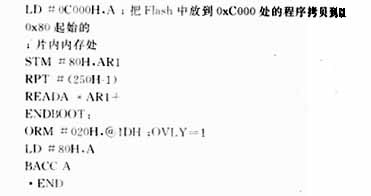

在實(shí)現(xiàn)雙核DSP的上電自舉后,A核和B核的用戶程序?qū)?huì)被存放在核內(nèi)程序空間的不同頁(yè)面上。如從DMA的角度觀看:A核的用戶程序?qū)⒈淮娣旁贏核的程序空間的第0頁(yè)上;B核的用戶程序?qū)⒈淮娣旁贐核的程序空間的第2頁(yè)上。因此A核的Boot表不需要修改,而B核的Boot表中的所有存放頁(yè)地址的表項(xiàng)中的內(nèi)容要更改為2。

(3)FLASH編程實(shí)現(xiàn)

根據(jù)FLASH芯片的控制時(shí)序,編寫一個(gè)簡(jiǎn)單的DSP程序,用于將A核的Boot表寫入FLASH的低64K,將B核的Boot表寫入FLASH的高64K。

3 上電試驗(yàn)結(jié)果

將電路上電后,A核控制的發(fā)光二極管開始閃爍,B核控制的發(fā)光二極管也開始閃爍,且A核發(fā)光二極管閃爍頻率要低于B核發(fā)光二極管閃爍頻率。由此現(xiàn)象可得出:A核與B核的BootLoader實(shí)現(xiàn)成功,未產(chǎn)生片外總線沖突;A核以2Hz的頻率點(diǎn)亮發(fā)光二極管,B核以10Hz的頻率點(diǎn)亮發(fā)光二極管。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論