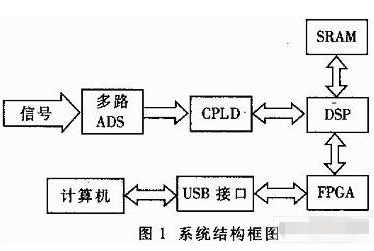

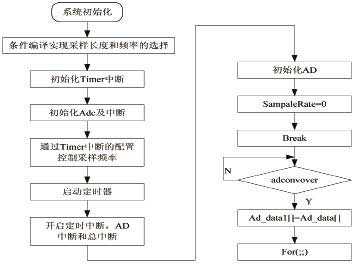

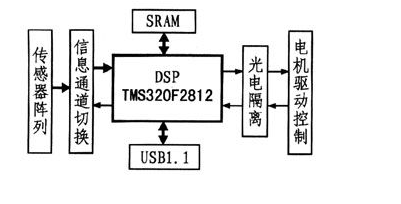

隨著DSP芯片功能越來越強,速度越來越快,性價比的不斷提高以及開發工具的日趨完善,廣泛用于通信、雷達、聲納、遙感、生物醫學、機器人、控制、精密機械、語音和圖像處理等領域。作為計算機接口之一的USB(Universal Serial Bus)口具有勢插拔、速度快(包括低、中、高模式)和外設容量大(理論上可掛接127個設備)的特性,使其成為PC機的外圍設備擴展中應用日益廣泛的接口標準。本文設計并實現了基于DSP的USB口數據采集分析系統,該系統的DSP負責數據的采集和運算處理,處理結果通過USB口送計算機顯示分析,其結構如圖1所示。

該結構圖中,CPLD和FPGA實現模塊接口,包括串并轉換、8位和32位數據總線間的轉換、SRAM等功能。采樣結果經過CPLD送至DSP運算處理(FFT變換、相關分析、功率譜分析等)后,由FPGA和USB接口送至主控計算機存儲和顯示。計算機應用程序易于實現豐富的圖形界面,具有良好的人機接口。

1 模數模塊

本系統主要用于振動信號和噪聲分析,要求采樣精度高,采樣頻率不超過100kHz。根據要求選用CRYSTAL公司的CS5396。該芯片原本用于立體聲采樣,基于∑-Δ結構,采樣精度高,24位分辨率,120dB的動態范圍;采樣頻率32kHz、44.1kHz、48kHz、96kHz可選;內部集成采樣保持器、模擬低通濾波器、數字濾波器,同時還具有時采樣功能;兩路同時采樣,串行輸出,串行數據由CPLD轉換成24位并行數據;由于該芯片量程是4V,差分輸入,所以模擬部分只需再加上簡單量程放大電路即可。這樣模擬電路十分簡單,抗干擾能力強、精度高。

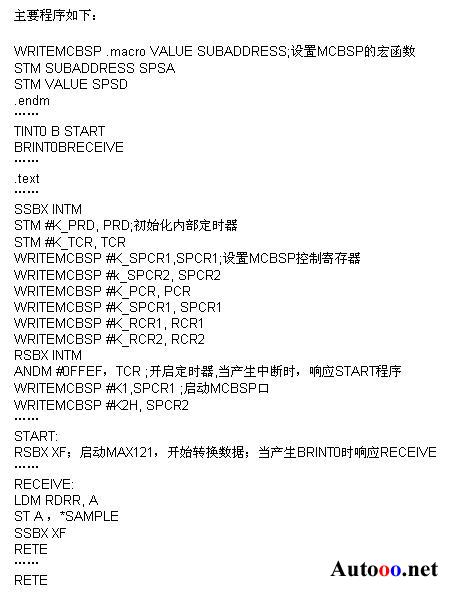

2 DSP處理器

選擇DSP處理器時主要考慮其運算速度、總線寬度和性價比。本系統采樣結構24位,最好選用32位DSP;系統要進行實時信號分析、模態分析等,要求有較高運算速度,所以選用TI公司的32位浮點DSP——TMS320VC33。該芯片采用哈佛結構,6級流水線操作,指令執行周期7ns,外設包括一個DMA控制器和一個緩沖串口。

N點復數FFT變換約做2N×Log2N次實數乘法運算和3N×Log2N實時加法運算。TMS320VC33的乘法、加法都是單周期指令,取N=1024,不計內存訪問和其它時間,則一次FFT所需時間為:10×5120×17ns約0.9ms。而按96KSPS的采樣頻率計算,1024點的采樣時間約10ms,可見該DSP速度足以滿足要求。

該DSP啟動模式可選,上電后執行駐留在低地址空間的BOOTLOADER;然后根據4個中斷輸入信號的狀態判斷啟動模式,可以從RAM、ROM或串行口啟動。本系統選擇串行口方式。這樣,DSP程序可以直接從PC下載送至DSP接口,做到在系統調試,具有極大的靈活性。

3 USB接口

USB協議的實現基于網絡的思想,是一種共享式的總線,在總線上數據以包(Packet)的形式發送。USB的數據傳送有4種模式:塊傳輸(Bulk Transfers)、中斷傳輸(Interrupt Transfers)、同步傳輸(Isochronous Transfers)、控制傳輸(Control Transfers)。當需要快速傳輸大批量的準確數據時,一般采用塊傳輸模式;當傳輸實時性較強的數據時,采用中斷傳輸模式。

當USB設備插入計算機時,計算機和USB設備之間產生一個枚舉過程。計算機檢測到有設備插入,自動發出查詢請求;USB設備回應這個請求,送出設備的Verdor ID和Product ID;計算機根據這兩個ID裝載相應的設備驅動程序,完成枚舉過程。

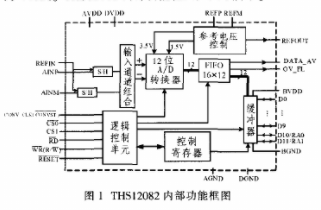

由于USB協議非常復雜,開發者不可能在底層基礎上進行開發。目前,市場上對USB協議進行封裝的接口芯片,如:National Semiconductor公司的USBN9602、Plilips公司的PDIUSBD12等。本系統選用CYPRESS公司的帶單片機內核的EZ-USB系列的AN2131QC.該芯片遵從USB1.0規范(12Mbps),將8051單片機內核、智能USB接口引擎、USB收發模塊、存儲器、串行口等集成一起,從而減少芯片接口時序。其內部結構如圖2(虛線內是芯片部分)。

EZ-USB的8051代碼(Firmware)可以固化在ROM內;更好的方案是通過USB口從主機下載到內部RAM,這樣,易于修改、調試和更新。之所以能下載代碼是因為芯片一上電完全在硬件上自動完成枚舉過程,不需要Firmware。完成枚舉后便可作為一個USB設備(叫做缺省USB設備)與計算機通訊,此時即可進行Firmware下載。下載完后,8051內核脫離RESET狀態開始執行代碼。可以通過Firmware對USB設備重新配置,這個重新配置過程叫做再枚舉。

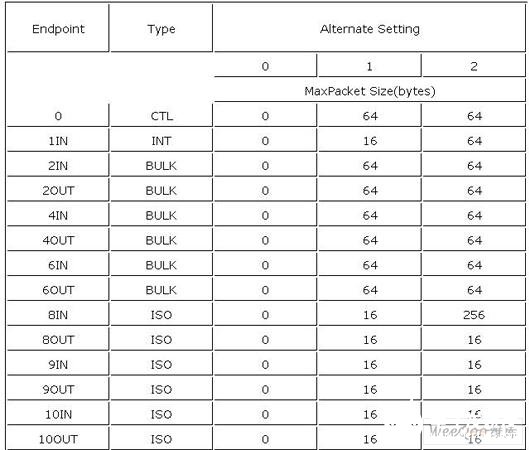

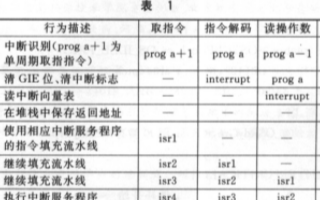

在EZ-USB中,缺省USB設備的接口中包括14個Endpoints,如表1所示。

表1 缺省USB端點(Endpoint)

計算機與USB設備的數據通信主要包括兩個方面:一是讀取采樣數據;二是給USB設備發送控制命令。發送控制命令先發送一個命令包(消息),然后根據情況發送后續數據或從設備讀取響應數據。因此,根據EZ-USB芯片的功能,直接使用缺省配置中的6個Endpoint。

Endpoit OUT2 BULK:用來發送控制命令包。

Endpoint IN2 BULK:接收從USB設備發來的DSP消息。

Endpoint IN4 BULK:用來從USB設備讀取數據,如讀取采樣數據、配置參數等。

Endpoint OUT4 BULK:用來向USB設備發送數據,如下載8051程序、下載FPGA程序等。

Endpoint OUT6 BULK:作輔助判斷用,當PC傳送完大量數據至USB設備時,向該端口寫任意數據以起到通知USB設備的作用。

Endpoint IN1 INT:用來從USB設備讀取響應信號,如下載FPGA程序是否成功的標志等。

在缺省配置基礎上可以編寫適合需要的代碼,如果對8051編程經驗豐的話,完全可以在不需要調試工具的情況下編寫Firmware。

本系統Firmware結構建立在對消息隊列不斷服務基礎上,即構建一個消息隊列,當接收到任何一方(DSP或計算機)的消息時,將其放入消息隊列。消息的接收是通過中斷服務程序來實現的。當處理完一個消息時,從消息隊列取出下一個消息進行處理。這種軟件結構非常簡單,思路清晰,對調試十分有利。

USB設備驅動程序基于WDM。WDM型驅動程序是內核程序,與標準的Win32用戶態程序不同。采用了分層處理的方法。通過它,用戶不需要直接與硬件打它道(在USB驅動程序中尤為明顯),只需通過下層驅動程序提供的接口號訪問硬件。因此,USB設備驅動程序不必具體對硬件編程,所有的USB命令、讀寫操作通過總線驅動程序轉給USB設備。但是,USB設備驅動程序必須定義與外部設備的通訊接口和通訊的數據格式,也必須定義與應用程序的接口。

本系統的驅動程序是在Compuware Numega Driver-Works的基礎上采用面向對象語言C++開發的。Driver-Works可以很快構造出驅動程序的框架。主要構造了兩個類:Class USBDAC和class USBDACDevice。Class USBDAC繼承了class Kdriver,負責裝載驅動程序和創建功能設備對象時要做的一些操作。Class USBDACDevice繼承了class KpnpDevice,是驅動程序的主要部分,負責設備啟動、停止的操作以及與設備的數據通訊。API函數調用和CreateFile ()、ReadFile ()、WriteFile ()、DeviceIO-Control ()、CloseFile()等的實現也在class USBDACDevice中完成。

Class USBDAC的定義如下:

class USBDAC : public Kdriver

{

SAFE_DESTRUCTORS

public:

/*Driver Entry (),

在系統引導或I/O管理器裝入驅動程序時,調用這個例程。執行大量的初始化函數,包括建立到其它驅動程序的指針、查找和定位由驅動程序使用的任何硬件資源等,不過,這部分工作大多由基類Kdriver完成。*/

virtual NTSTATUS DriverEntry(PUNICODE_STRING RegistryPath);

/*AddDevice(),創建一個Device對象。調用其構造函數對設備初始化,創建設備的名稱等。*/

virtual NTSTATUS AddDevice(PDEVICE_OBJECT Pdo);

Int m_Unit;

};

Class USBDACDevice的定義如下:

Class USBDACDevice : public KpnpDevice

{

// Constructors

public:

SAFE_DESTRUCTORS

USBDACDevice(PDEVICE_OBJECT Pdo,ULONG Unit);

~USBDACDevice ();

// Member Functions

public:

…

//添加自己的成員函數

NTSTATUS USBDAC_GetACK(int &);

NTSTATUS USBDAC_StartADConversion(void);

NTSTATUS USBDAC_StopADConversion(void);

NTSTATUS USBDAC_DownloadFPGA(KIrp);

NTSTATUS USBDAC_Download8051(KIrp);

NTSTATUS USBDAC_SetChannelParameter(PUCHAR,ULONG,int);

…

};

4 FPGA

FPGA模塊主要實現單片機與DSP間的數據緩沖、8位數據線與32位數據線間的轉換、單片機同步串口和DSP緩沖串口的切換。要求FPGA能實現豐富的內部RAM和準確的時鐘控制。根據需要選用XILINX公司的XCV50TQ144。該器件采用SRAM 查找表結構,具有系統內可再編程(ISP)和運行間可再配置等特性。系統初始化時由USB口下載FPGA程序,通過單片機串口對其進行線配置。

本系統可廣泛用于振動、噪聲測試分析。可以在WINDOWS95/98/NT下開發各類動態測試與信號處理的應用程序,根據需要加載已經編制的各種DSP算法,使其具有信號分析、模態分析、聲學分析、環境測試、長時間記錄等功能。

責任編輯:gt

電子發燒友App

電子發燒友App

評論