去年的時候,拋磚引玉的寫了一篇“硬件定義軟件?還是軟件定義硬件?”的文章,現在再看,發現很多考慮不全面不深刻的地方。繼續拋磚,與大家深入探討此話題。

今天這篇文章,我們主要關注如下話題:

超異構計算,為什么需要開放生態?

開放生態應該由硬件定義還是軟件定義?

什么樣的生態才算開放?

1.1 CPU指令集架構ISA

ISA(Instruction Set Architecture,指令集架構),是計算機體系結構與編程相關的部分(不包含組成和實現)。ISA定義了:指令集、數據類型、寄存器、尋址模式、內存管理、I/O模型等。

CPU圖靈完備,是可自運行的處理器:CPU主動從指令內存讀取指令流,然后譯碼后執行;指令執行會涉及到數據的載入(Load)、計算和存儲(Store)。

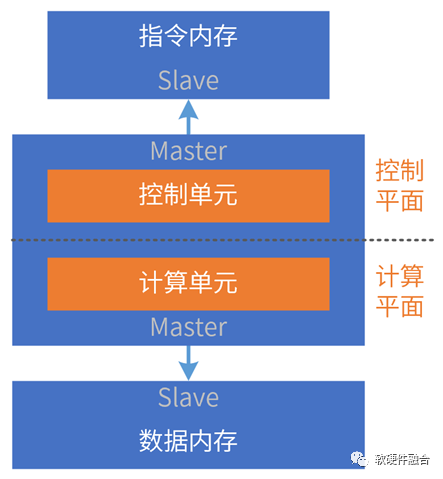

我們可以把處理器簡單地分為控制平面和計算平面兩部分。

CPU是指令流驅動計算的處理引擎。

1.2 (CPU視角的)GPU架構

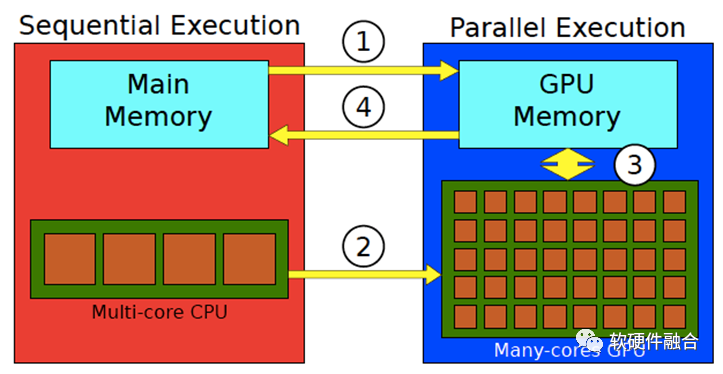

架構側重軟硬件之間的交互“接口”,而微架構側重具體實現。因此,GPU架構通常指的是CPU視角看到的GPU“接口”。從CPU視角看GPU的處理流程:

CPU把數據準備好,并保存在CPU內存中;

將待處理的數據從CPU內存復制到GPU內存(處理①);

CPU指示GPU工作,配置并啟動GPU內核(處理②);

多個GPU內核并行執行,處理準備好的數據(圖中的③處理);

處理完成后,將處理結果復制回CPU內存(處理④);

CPU把GPU的結果進行后續處理。

1.3 ASIC專用處理引擎

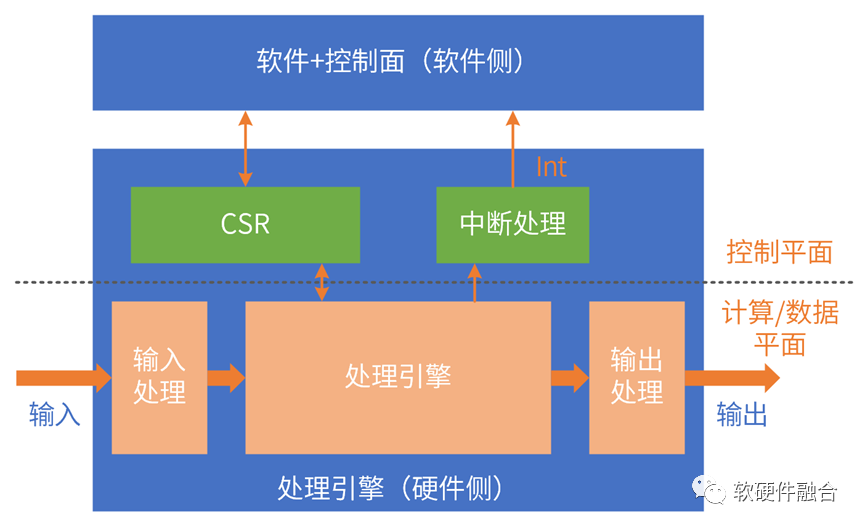

ASIC功能邏輯完全確定:通過驅動程序和CSR和可配置表項交互,以此來控制硬件運行。

ASIC覆蓋的場景較小,并且類型多種多樣;即使同一場景,不同廠家實現依然存在差別;ASIC場景碎片化,毫無生態可言。

和GPU類似,ASIC的運行依然需要CPU的參與:

數據的輸入:數據在內存準備好,CPU控制ASIC引擎的輸入邏輯,把數據從內存搬到處理引擎;

ASIC的運行控制:控制CSR、可配置表項、中斷等;

數據的輸出:CPU控制ASIC引擎的輸出邏輯,把數據從引擎搬到內存,等待后續處理。

ASIC是數據流驅動計算的處理引擎。

1.4 DSA領域專用架構

DSA是在ASIC基礎上的回調,具有一定的可編程能力,覆蓋場景更多,性能和ASIC同量級。

DSA經典案例:

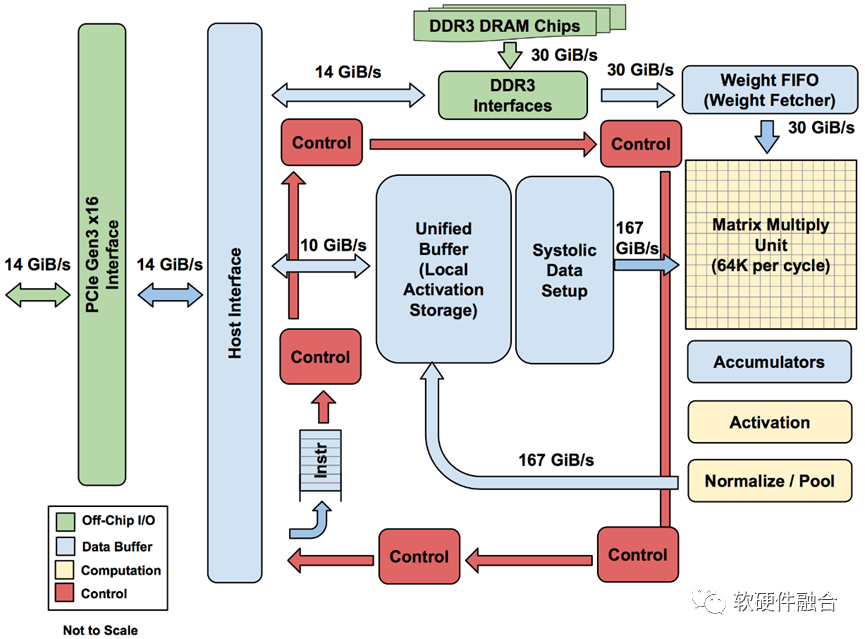

AI-DSA,如谷歌TPU;

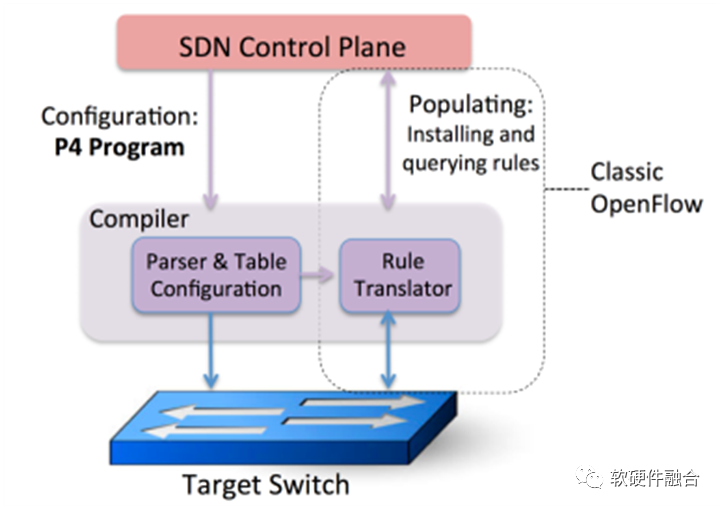

網絡DSA,如Intel Barefoot P4-DSA網絡交換芯片。

1.5 小結:從CPU到ASIC,架構越來越碎片化

指令是軟件和硬件的媒介,指令的復雜度(單位計算密度)決定了系統的軟硬件解耦程度。

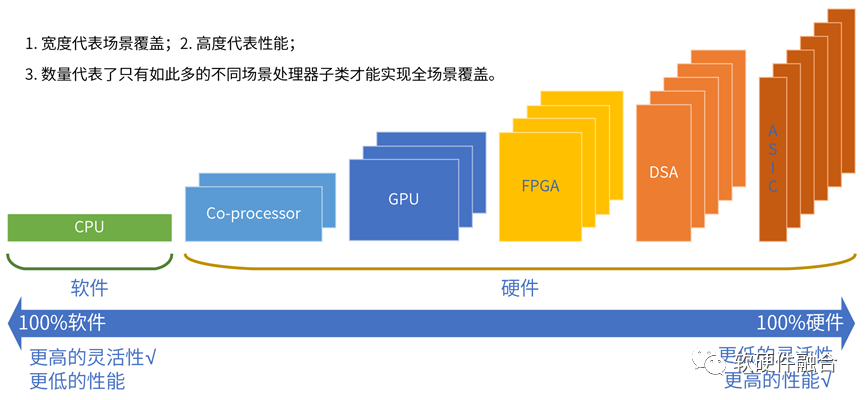

按照指令的復雜度,典型的處理器平臺大致分為CPU、協處理器、GPU、FPGA、DSA、ASIC。

世間萬物由基本粒子組成,復雜處理由基本計算組成。

指令復雜度越高,單個處理器引擎覆蓋的場景就會越小,處理器引擎的形態就會越多。

從CPU到ASIC,處理器引擎越來越碎片化,構建生態越來越困難。

2 計算架構:從異構到超異構

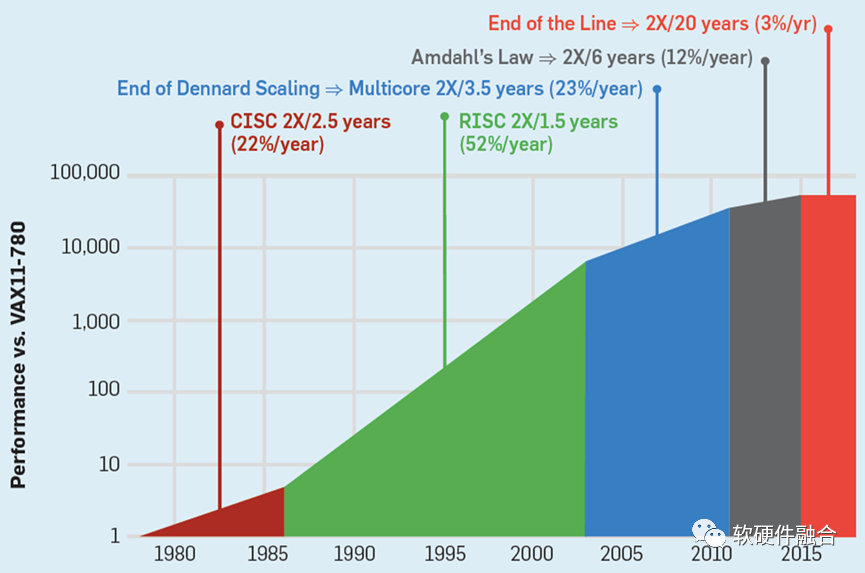

2.1 CPU性能瓶頸,引發連鎖反應

在云計算、邊緣計算以及一些超級終端的復雜計算場景,對靈活性的要求遠高于對性能的要求。

CPU通用靈活性好,在符合性能要求的情況下,各類復雜計算場景,CPU依然是最優選擇。

對算力的需求不斷增加,不得不通過各種異構加速方式進行性能優化。

實踐證明,在復雜計算場景,提升性能的同時,不能損失通用靈活性(言外之意,目前很多技術方案損害了靈活性)。

2.2 異構計算存在的問題

復雜計算的挑戰:系統越復雜,需要選擇越靈活的處理器;性能挑戰越大,需要選擇越偏向定制的加速處理器。本質矛盾是:單一處理器無法兼顧性能和靈活性;即使我們拼盡全力平衡,也只“治標不治本”。

CPU+xPU異構計算中的xPU,決定了整個系統的性能/靈活性特征:

GPU靈活性較好,但性能效率不夠極致;

DSA性能好,但靈活性差,難以適應復雜計算場景對靈活性的要求。案例:AI落地困難。

FPGA功耗和成本高,需要一些定制開發,落地案例不多。

ASIC功能完全固定,難以適應靈活多變的復雜計算場景。

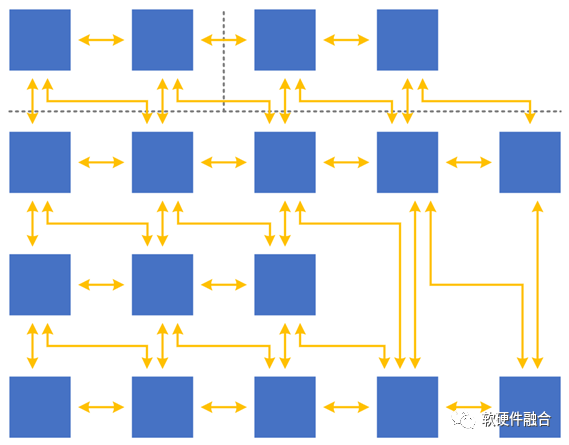

異構計算還存在計算孤島的問題:

異構計算面向某個領域或場景,領域之間的交互困難。

服務器物理空間有限,無法多個物理加速卡,需要把這些加速方案整合;

需要強調的是:整合,不是簡單的拼湊,而是要架構重構。

2.3 超異構存在的前提條件:復雜系統和超大規模

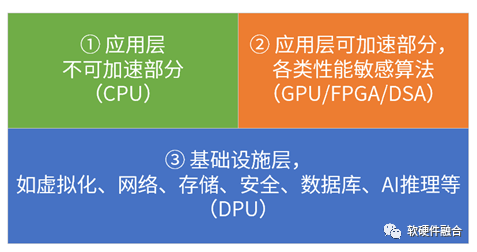

基礎特征:①超大規模的計算集群;②復雜宏系統,是由分層分塊的組件(系統)組成。

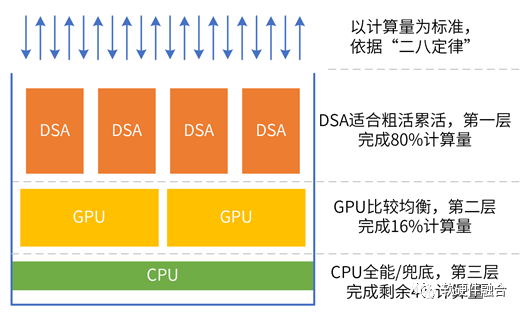

單服務器的宏系統復雜度,以及超大規模的云和邊緣計算,使得“二八定律”在系統中普遍存在,因此,可以把:相對確定的任務沉淀到基礎設施層,相對彈性的沉淀到彈性加速部分,其他繼續放在CPU(CPU兜底)。

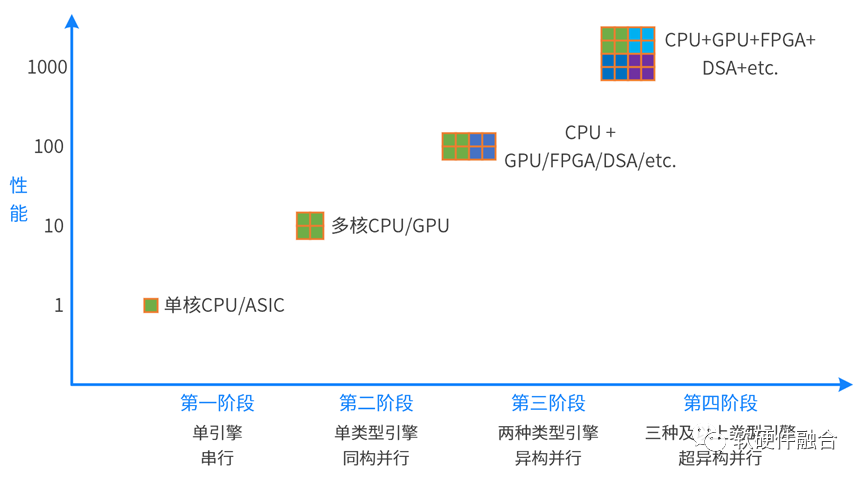

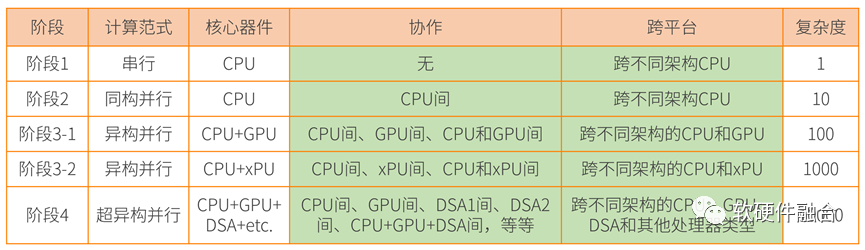

2.4 從異構并行到超異構并行

計算從單核的串行走向多核的并行;又進一步從同構并行走向異構并行。未來,計算需要進一步從異構并行走向超異構并行。

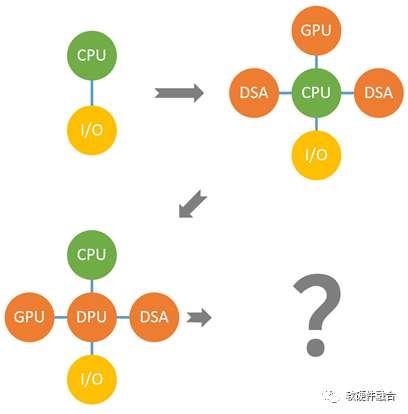

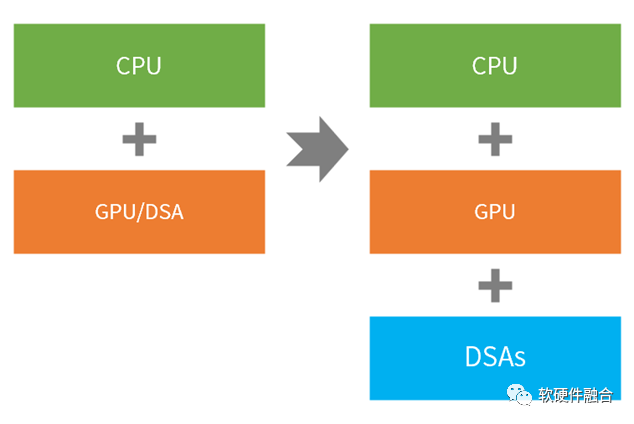

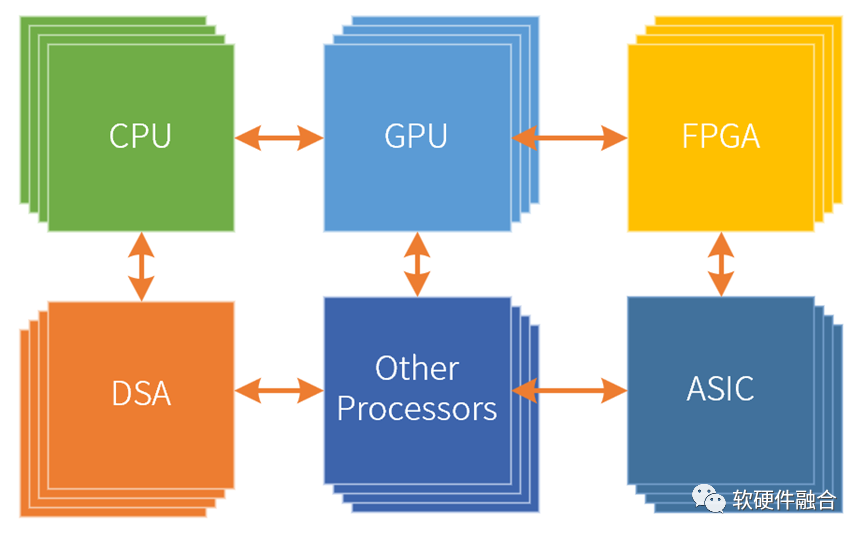

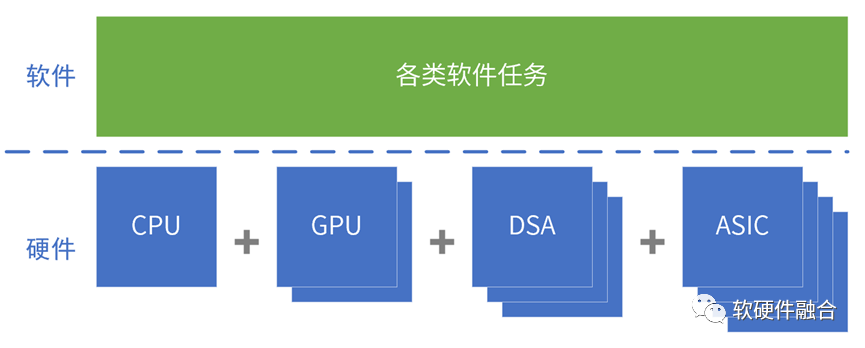

異構計算是CPU+xPU的兩個層次的處理引擎類型,而超異構計算則是CPU+GPU+DSA的三個層次的處理引擎類型。

超異構計算,不是簡單的集成,而是把更多的異構計算整合重構,各類型處理器間充分的、靈活的數據交互,形成統一的超異構計算宏系統。

2.5 Intel:超異構、XPU和oneAPI

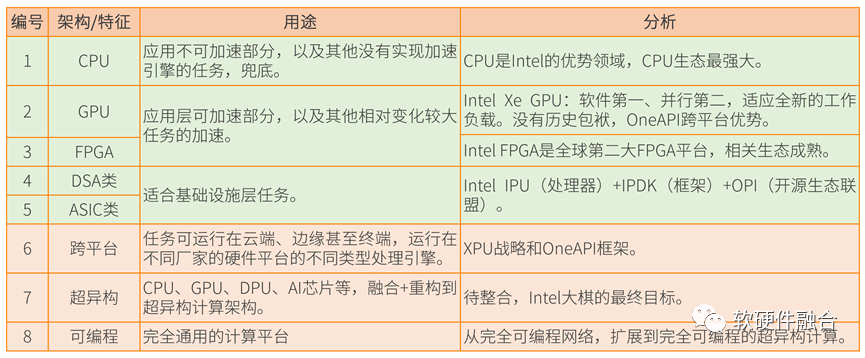

2019年,Intel提出超異構計算相關概念;目前為止,Intel沒有完全符合超異構概念的產品。

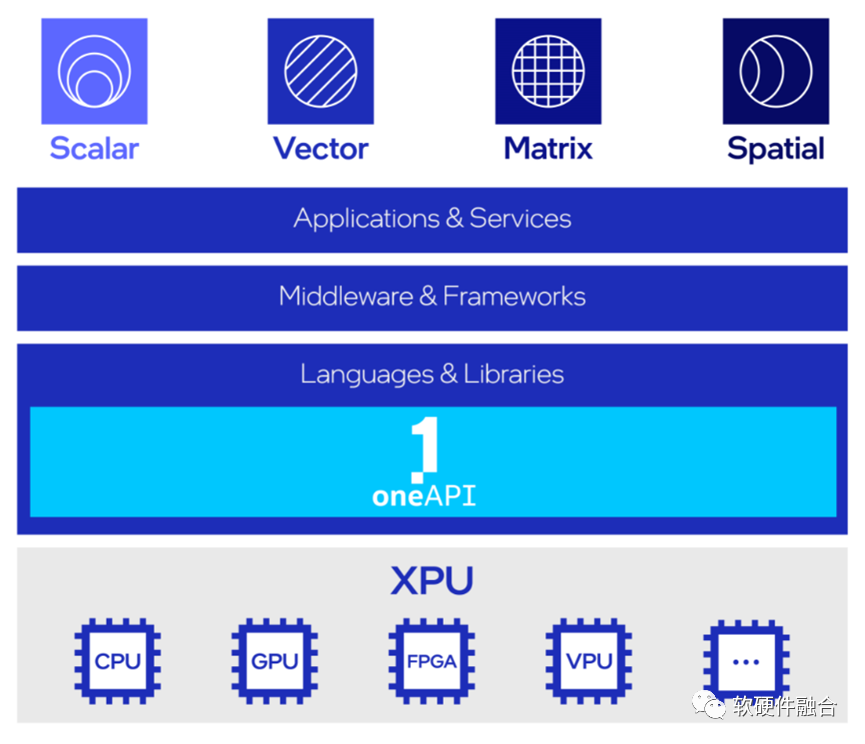

超異構計算的基礎引擎是XPU,XPU是多種架構的組合,包括CPU、GPU、FPGA 和其他加速器;

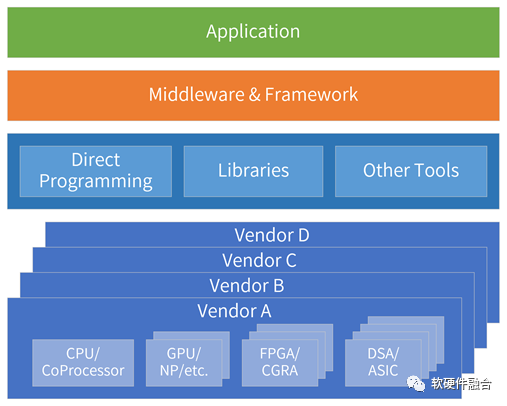

oneAPI是開源的跨平臺編程框架,底層是不同的XPU處理器,通過OneAPI提供一致性編程接口,使得應用跨平臺復用。

2.6 Intel超異構分析

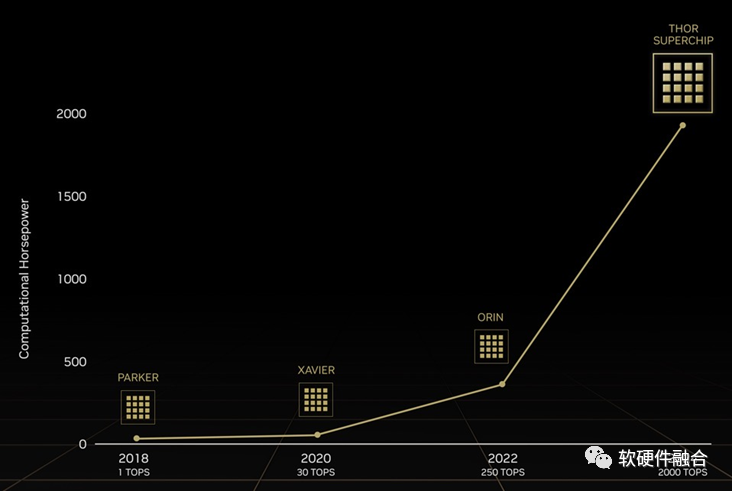

2.7 NVIDIA自動駕駛Thor

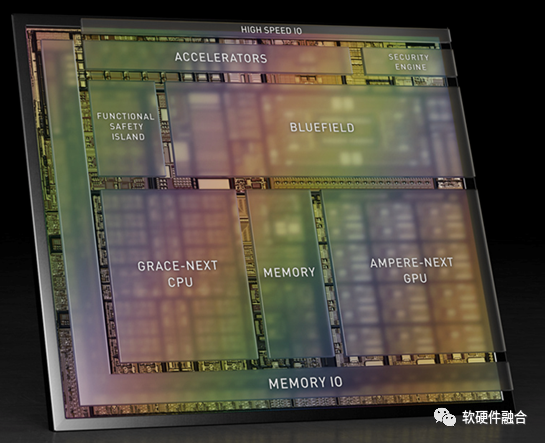

(上圖為Atlan架構示意圖,Atlan和Thor架構相同,性能上有差異)

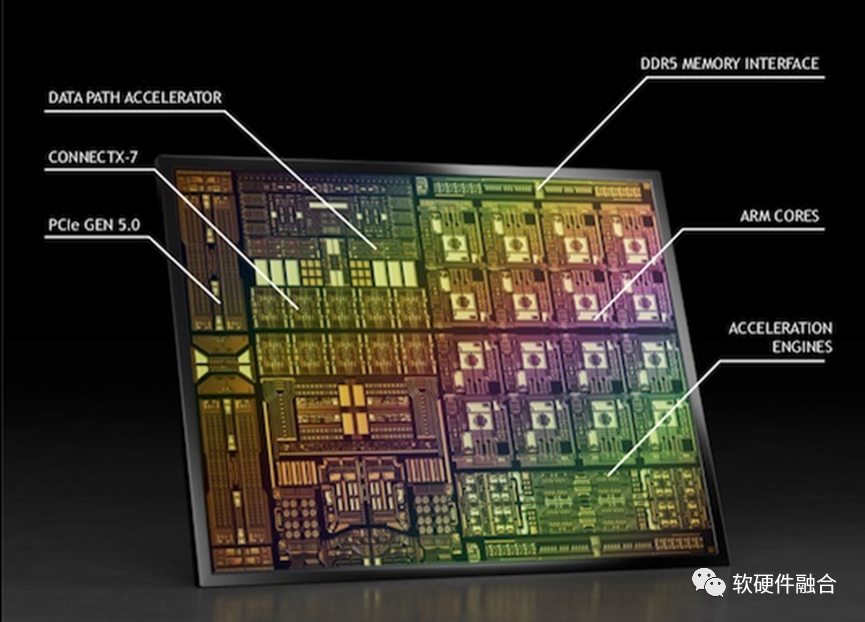

NVIDIA自動駕駛Thor芯片,由數據中心架構的CPU+GPU+DPU三部分組成,算力高達2000TFLOPS的超異構計算芯片。

Thor是把傳統多個DCU(SOC)的功能融合成單個超異構處理芯片。

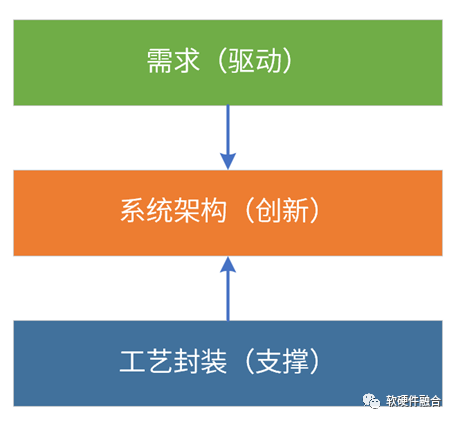

2.8 為什么是現在?

首先,是需求驅動。軟件新應用層出不窮,兩年一個新熱點;并且,已有的熱點技術仍在快速演進。元宇宙是繼互聯網和移動互聯網之后的下一個互聯網形態,要想實現元宇宙級別的體驗,需將算力提升1000倍。

其次,工藝和封裝支撐。工藝封裝持續進步,工藝10nm以下,芯片從2D->3D->4D。Chiplet使得在單芯片層次,可以構建規模數量級提升的超大系統。系統規模越大,超異構的優勢越明顯。

最后,系統架構需要持續創新。通過架構創新,在單芯片層次,實現多個數量級的性能提升。挑戰:異構編程很難,超異構編程更是難上加難;如何更好地駕馭超異構,是成敗的關鍵。

2.9 小結:超異構設計和開發難度呈指數上升

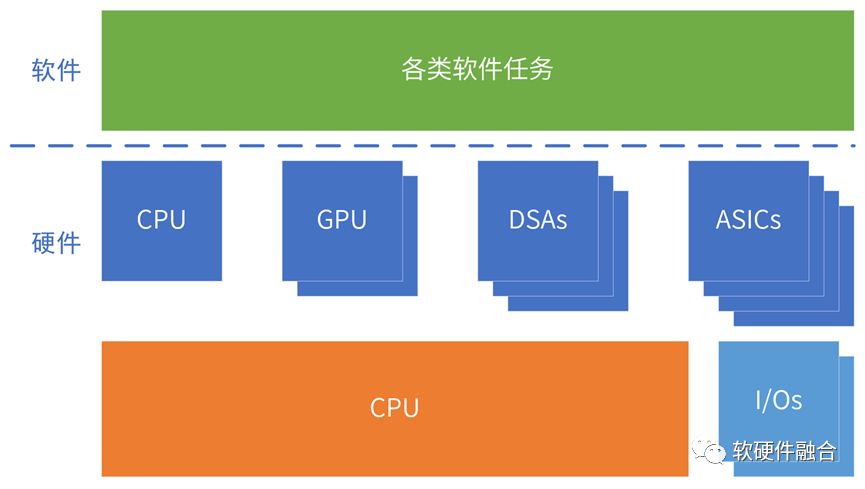

軟件需要跨平臺復用,跨①不同架構、②不同處理器類型、③不同廠家平臺、④不同位置、⑤不同設備類型。

如此復雜的超異構該如何駕馭?

3 開放架構和生態的現狀

3.1 開放架構和生態綜述

系統必然是在某個層次開放:

用戶接口:應用程序必須提供UI供用戶使用。

開發庫:指提供函數的代碼,開發者可以從自己的代碼中調用這些函數來處理常見任務,如CUDA庫等。

操作系統:提供系統調用接口。

硬件需要提供硬件接口/架構,給系統軟件調用,如I/O接口、CPU架構、GPU架構等。

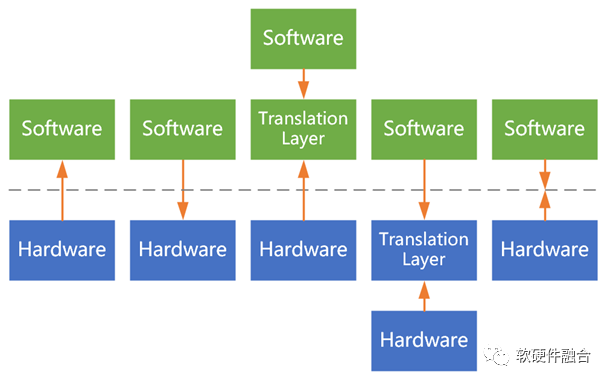

互操作性:不同的系統、模塊一起協同工作并共享信息的能力。系統堆棧的相鄰兩層,遵循配對的接口協議進行交互;如果接口不匹配,就需要有接口轉換層。

開放接口/架構及生態:基于互操作性,形成標準的開放的接口/架構;大家遵循此接口/架構開發產品和服務,從而形成開放生態。

3.2 RISC-V:開放CPU架構

x86架構主要應用在PC和數據中心領域,ARM架構主要應用在移動領域,目前也在向PC和服務器領域拓展。

為了給芯片提供低成本CPU,加州大學伯克利分校開發了RISC-V, RISC-V已成為行業標準的開放ISA。

理論上可通過靜態編譯、動態翻譯等方式,實現跨不同CPU架構運行。但都存在損耗及穩定性等問題,需要很多移植方面的工作。

一個平臺上的程序難以在其他平臺上運行(靜態),運行時跨平臺(動態)更是難上加難。

理想情況,如果形成RISC-V的開放生態,沒有了跨平臺的損耗和風險,大家可以把精力專注于CPU微架構及上層軟件的創新。

RISC-V的優勢:

免費。指令集架構免費獲取,不需要授權,沒有商業上掣肘。

開放性。任何廠家就可以設計自己的RISC-v CPU,大家共建一套開放的生態,共榮共生。

簡潔高效。沒有歷史包袱,ISA更高效。

標準化。最關鍵的價值。如果RISC-v變成主流架構,就沒有了跨平臺等成本或代價。

3.3 GPU架構生態

目前,GPU還沒有像CPU RISC-V一樣,有標準化的、開源的ISA架構。

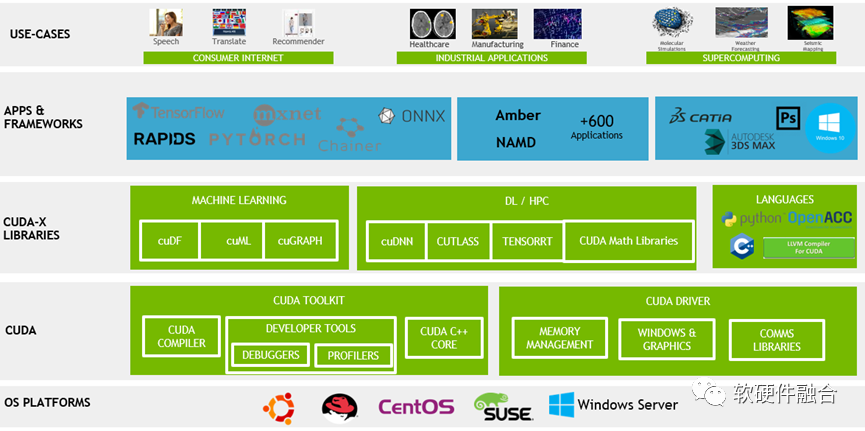

CUDA是NVIDIA GPU的開發框架,向前兼容。

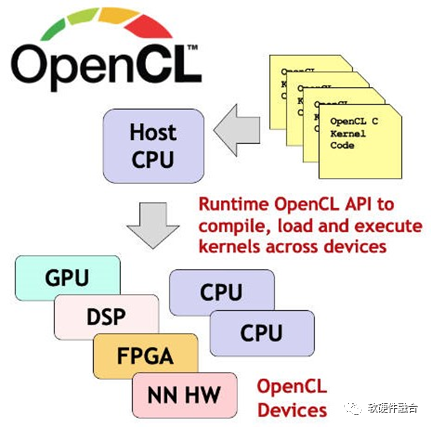

OpenCL是完全開放的異構開發框架,可以跨CPU、GPU、FPGA等處理引擎。

3.4 DSA,混戰

①DSA領域多種多樣,即使同一領域,②不同廠家的DSA架構仍不相同,甚至③同一廠家不同代產品的架構也不相同。

最典型的AI-DSA場景,目前就處在各種DSA架構混戰的階段。

要想構建DSA的生態:

軟件定義,不需要開發應用,兼容已有軟件生態;

少量編程(許多DSA編程,類似靜態配置腳本),門檻較低的標準的領域編程語言;

開放架構,防止架構過多導致的市場碎片化。

DSA架構一般來說分為靜態和動態兩部分:

靜態部分。類配置腳本,通過編譯器映射到具體的DSA引擎,編程實現DSA引擎的具體功能。

動態部分。DSA的動態部分通常不是編程實現,而是跟已有軟件進行適配;相當于是把軟件的數據平面/計算平面卸載到硬件,控制平面依然在軟件;符合軟件定義的思路。

3.5 DSA/ASIC集成平臺:NVIDIA DPU

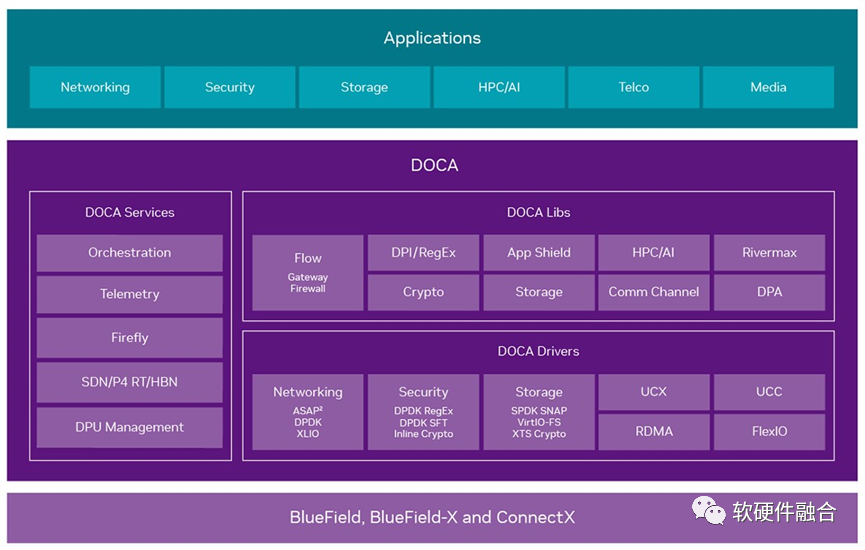

DPU集成虛擬化、網絡、存儲、安全等DSA/ASIC引擎,DOCA框架:庫文件、運行時和服務、驅動程序組成。

DPU/DOCA是非開源/開放的封閉架構、平臺和生態。

3.6 DSA/ASIC集成平臺:Intel IPU

和NVIDIA DPU類似,Intel IPU集成虛擬化、網絡、存儲、安全等DSA/ASIC引擎。

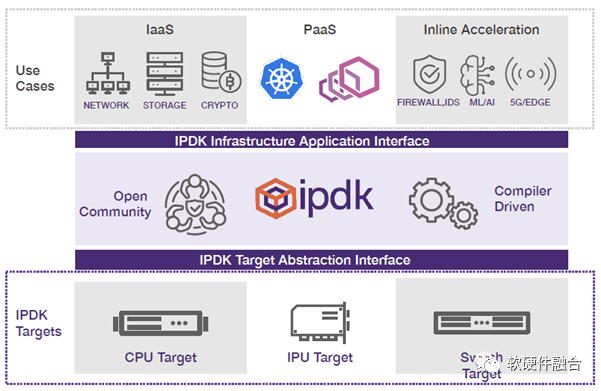

IPDK是開源的基礎設施編程框架,可運行在CPU、IPU、DPU或交換機。

Intel和Linux基金會的OPI項目:為基于 DPU/IPU 類技術的下一代架構和框架,培育一個標準的開放生態系統。

Intel IPU/IPDK/OPI是開源/開放的架構、平臺和生態。

3.7 硬件使能:Hardware Enablement

隨著數據中心演變成虛擬機、裸金屬機和容器的組合,OpenStack社區擴大成新的OpenInfra社區。

旨在推進開放基礎設施領域技術發展,包括:公共云、私有云、混合云,以及AI/ML、CI/CD、容器、邊緣計算等。

Ubuntu硬件使能版本:為了更好地支持最新的硬件,會經常更新內核版本,不太適合企業用戶。

OpenInfra硬件使能:軟件組件需要在云和邊緣環境使能硬件,包括GPU、DPU、FPGA等。

在硬件加速/軟件卸載的語境下,硬件使能可以理解成:

軟件要支持硬件加速,“硬件加速原生”;

如果存在硬件加速的資源,則采用硬件加速模式;

如果不存在硬件加速的資源,則繼續采用傳統的軟件運行模式。

4 硬件定義軟件,還是軟件定義硬件?

4.1 系統的控制平面和計算平面

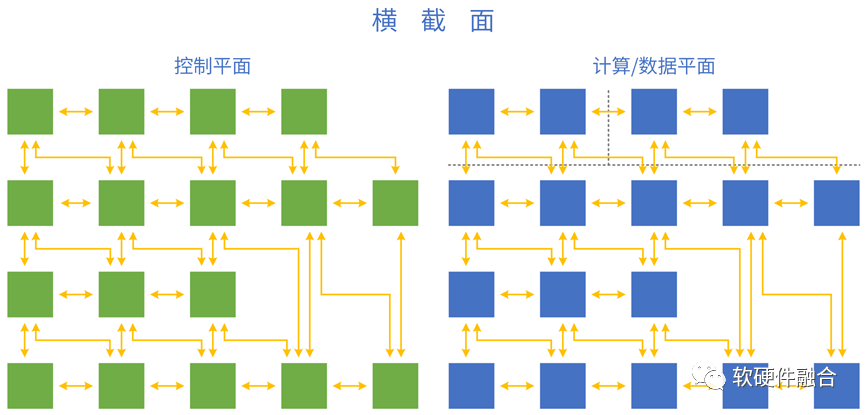

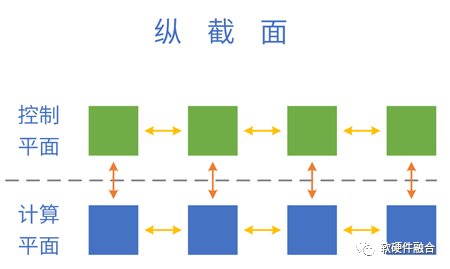

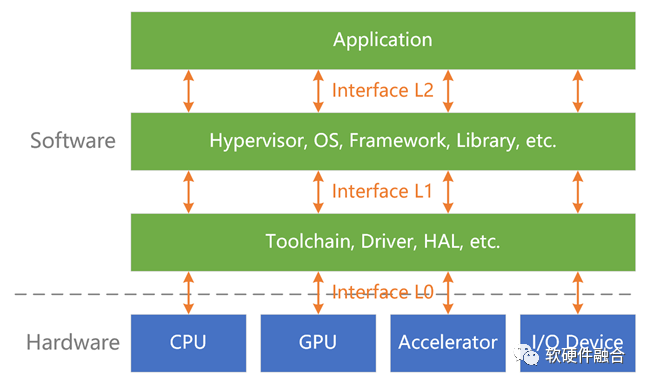

把分層分塊的系統,映射到軟硬件具體實現:控制平面運行在CPU,計算/數據平面運行在CPU、GPU、DSA等處理引擎。

4.2 泛義的軟硬件接口

泛義的接口:

塊和塊之間、層和層之間的接口;

軟件和軟件之間、硬件和硬件之間、軟硬件之間的接口。

軟件和硬件之間的接口:

硬件定義接口,軟件適配;

軟件定義接口,硬件適配;

硬件/軟件定義接口,軟件接口適配層;

硬件/軟件定義接口,接口適配層卸載;

軟件硬件設計遵循標準接口(要求:標準、高效、開源、迭代)。

4.3 什么是硬件/軟件定義?

系統是由軟件和硬件組成,也必然是軟硬件協同的。從軟硬件的相互關系和影響,闡述軟件定義和硬件定義。

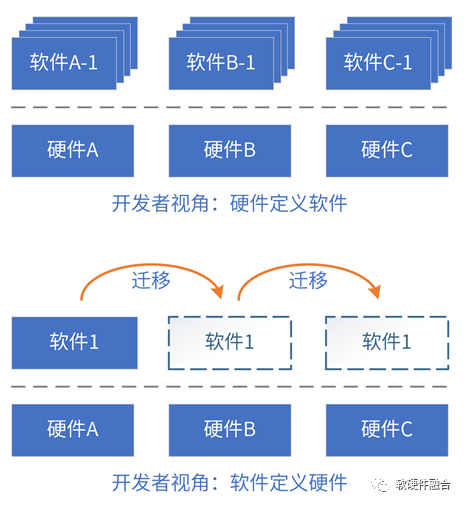

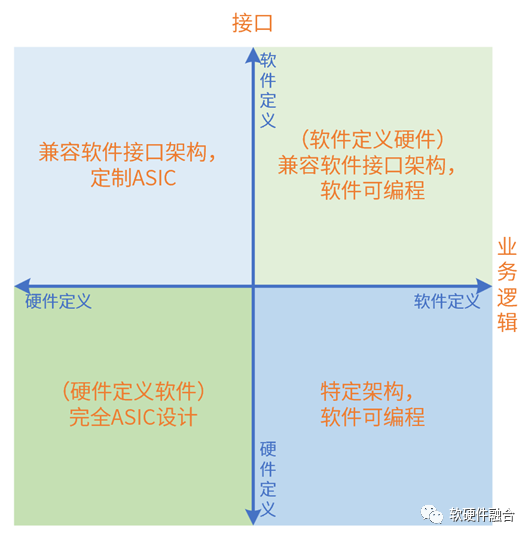

評價標準:系統的業務邏輯由誰決定;軟件和硬件的交互接口(架構)由誰決定。

“硬件定義軟件”定義為:系統的業務邏輯以硬件實現為主,軟件實現為輔;軟件依賴于硬件提供的接口構建。

“軟件定義硬件”定義為:當一個系統的業務邏輯以軟件實現為主,硬件實現為輔;或者硬件引擎是軟件可編程的,硬件引擎按照軟件編程的邏輯執行操作;硬件依賴于軟件提供的接口構建。

4.4 硬件/軟件定義的依據:系統復雜度

硬件定義軟件,還是軟件定義硬件,跟系統復雜度是休戚相關的。

系統復雜度較小,迭代較慢。可以快速設計優化的系統軟硬件劃分,先硬件開發,然后開始系統層和應用層的軟件開發。

量變引起質變,隨著系統復雜度上升,系統迭代快,直接實現一個完全優化的設計難度很大。系統實現變成了演進式:

前期系統不夠穩定,算法和業務邏輯在快速迭代,需要快速實現想法。這樣,基于CPU的軟件實現就比較合適;

隨著系統發展,算法和業務邏輯逐漸穩定,后續逐步優化到GPU、DSA等硬件加速來持續優化性能。

硬件定義還是軟件定義?本質上是系統定義。系統的復雜度過高,實現難以一次到位,于是系統的實現,變成了持續優化和迭代的過程。

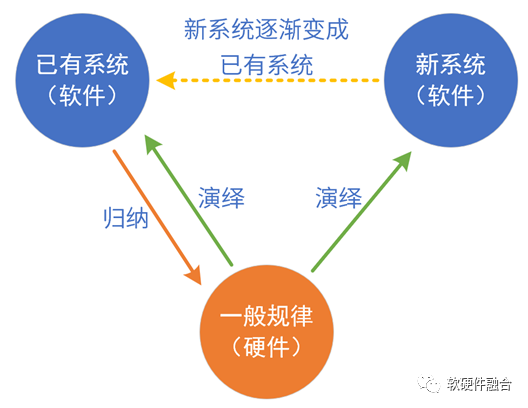

4.5 硬件/軟件定義的本質:歸納和演繹

硬件/軟件定義的本質,是通過歸納和演繹實現系統及系統的發展。從長期和發展的視角看,系統是由軟硬件共同定義的。我們以典型的處理引擎實現進行分析:

CPU:把所有領域歸納出共性(最基本的指令),這個共性“放之四海皆準”。也即是說,相對其他平臺,“CPU不需要再歸納”,只需要持續演繹新的領域和場景。軟件定義:CPU已經是成熟的軟件平臺,可以基于CPU快速實現系統原型,當系統的算法和業務邏輯穩定后,可通過硬件加速進行性能優化。

GPU:把很多個領域歸納出共性,然后硬件實現共性,軟件實現個性。GPU平臺實現后,可以持續演繹新的領域新的場景。GPU是足夠通用、成熟的并行計算開發平臺。

DSA:把某個領域多個場景的業務邏輯進行歸納:硬件實現共性部分,軟件實現個性部分。DSA平臺實現后,可以在此領域演繹新的場景。

ASIC:具體場景的算法和業務邏輯直接變成硬件,軟件只是基本的控制作用。直接映射,談不上歸納和演繹。

5 總結:軟硬件共同定義,超異構開放生態

5.1 軟件原生支持硬件加速

軟件原生支持硬件加速:

軟件架構調整,控制面和計算/數據面分開;

控制面和計算/數據面接口標準化;

硬件加速資源的發現能力,自適應選擇軟件計算/數據面或硬件計算/數據面。

數據的輸入,可以來源于軟件,也可以來源于硬件;

數據的輸出,可以去向軟件,也可以去向硬件。

5.2 完全可編程

完全可編程,不是CPU可編程,而是在極致優化性能基礎之上的可編程。完全可編程是分層的可編程體系:

基礎設施層可編程。基礎設施層Workload不經常變化,可以采用DSA架構。

彈性應用可編程。支持主流GPU編程方式,可以把常見應用通過DSA,實現更高效率的加速。

應用可編程。應用不確定性最大,仍然運行在CPU。同時,CPU負責兜底,所有其他不適合加速或沒有加速引擎的任務都在CPU運行。

實現完全可編程的同時,性能數量級的提升:

從整個系統看,絕大部分是DSA加速的,因此系統的性能效率接近于DSA;

Chiplet+超異構,系統規模數量級提升,系統性能數量級提升;

從用戶角度,應用運行在CPU,用戶體驗到的是100%的CPU可編程。

5.3 開放接口和架構

ASIC/DSA覆蓋的領域/場景較小,芯片對場景的覆蓋(相比CPU、GPU)越來越碎片化。

構建生態越來越困難。需要從硬件定義,逐步轉向軟件定義。

超異構計算,包括CPU、GPU,也包括多種DSA、ASIC類型的處理器。

異構的引擎架構越來越多,必須構建高效的、標準的、開放的接口和架構體系,才能構建一致性的宏架構(多種架構組合)平臺,才能避免場景覆蓋的碎片化。

5.4 計算需要跨不同類型處理器

超異構包含CPU、GPU、FPGA、DSA等不同類型的處理器,計算任務需要跨不同類型的處理器運行。

oneAPI是Intel開源的跨平臺編程框架,通過oneAPI提供一致性編程接口,使得應用可以跨不同類型處理器運行。

更廣泛的,不僅僅是跨不同類型的處理器,還要能跨不同廠家的芯片平臺。

5.5 超異構開放生態

要想提升算力利用率,就需要把一個個孤島的計算資源,整合成統一的資源池。

需要通過跨平臺融合,實現計算資源池化:

維度一:跨同類型處理器架構。如軟件可以跨x86、ARM和RISC-v CPU運行。

維度二:跨不同類型處理器架構。軟件需要跨CPU、GPU、FPGA和DSA等處理器運行。

維度三:跨不同的芯片平臺。如軟件可以在Intel、NVIDIA等不同公司的芯片上運行。

維度四:跨云網邊端不同的位置。計算可以根據各種因素的變化,自適應的運行在云網邊端最合適的位置。

維度五:跨不同的云網邊服務供應商、不同的終端用戶、不同的終端設備類型。

超異構時代,必須要形成開放的生態,才能讓計算資源形成一個整體,才能滿足元宇宙等應用場景對算力數量級提升的要求。

5.6 軟硬件共同定義:超異構開放生態

首先,是超異構計算架構。CPU+GPU+FPGA+DSA等多種架構處理引擎組成的超異構計算;實現既要又要:接近CPU的靈活性,接近ASIC的性能效率,以及多個數量級提升的性能。

其次,要平臺化&可編程。兩個一切:軟件定義一切,硬件加速一切;兩個完全:完全可軟件編程的硬件加速平臺,完全由軟件編程決定業務邏輯;一個通用:足夠的通用性,滿足多場景、多用戶的需求,滿足業務的長期演進。

最后,要標準&開放。架構/接口標準、開放,持續演進;擁抱開源開放的生態;支持云原生、云網邊端融合;用戶無(硬件、框架等)平臺依賴。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論