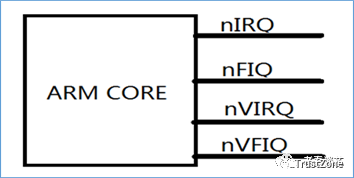

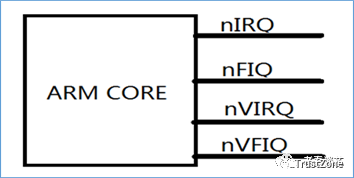

/ FIQ 由外部硬件觸發的中斷。 2、軟中斷 soft interrupt 由系統調用的中斷事件,由軟件產生的中斷事件。 3、復位 Reset 4、未定義指令 5、數據異常 例如數據越界等。 中斷: ARM 有兩級外部中斷:1、FIQ;2、IRQ。 但大多數的嵌入式系統都有多于兩個的外部中斷

2020-10-07 15:22:00 3038

3038

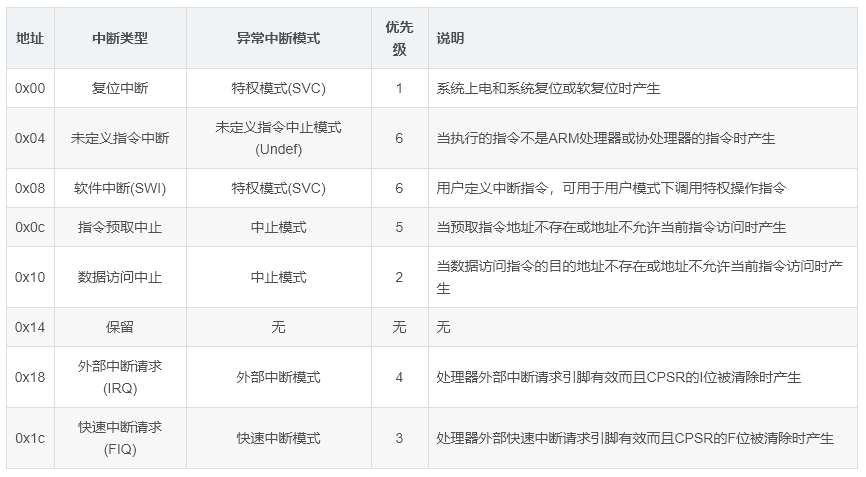

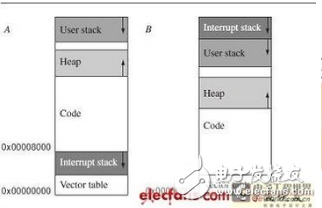

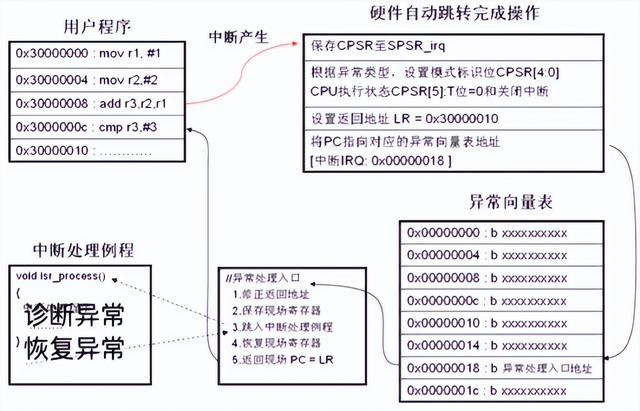

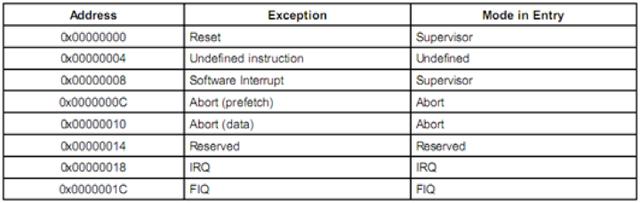

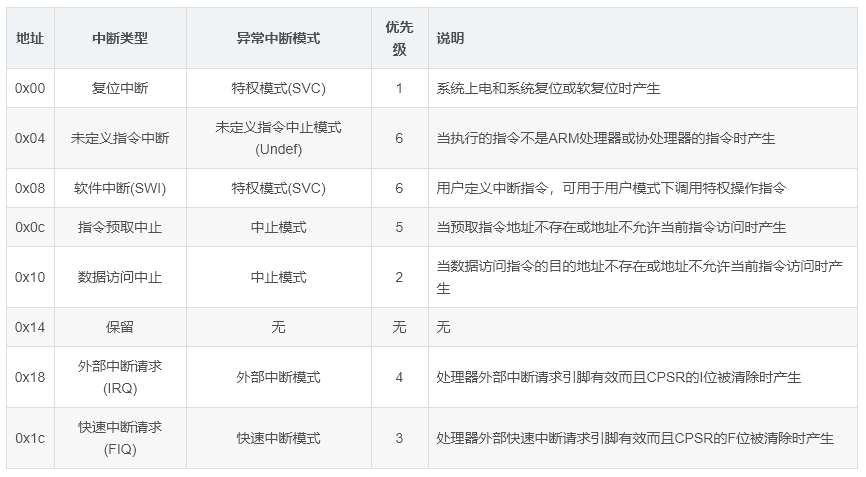

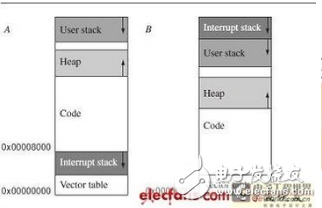

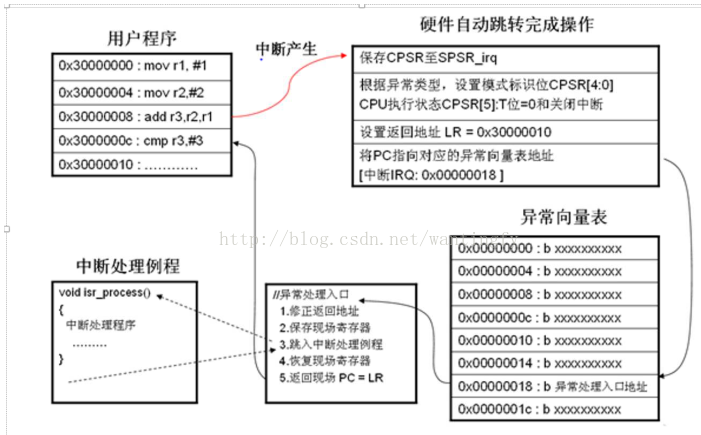

基礎知識 ARM體系架構的處理器中通常將低地址32字節作為中斷向量表,當中斷產生時會執行以下操作: ① 保存處理器當前狀態,設置中斷屏蔽位和各條件標志位 ② 設置當前程序狀態寄存器CPSR中相應

2020-11-21 11:10:27 2274

2274

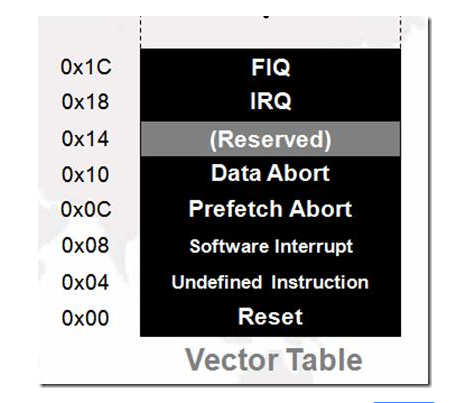

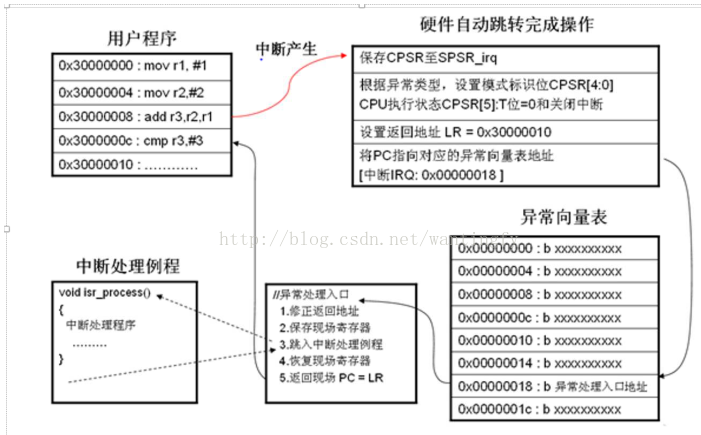

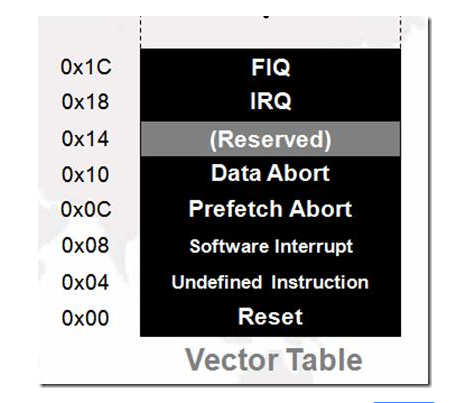

01、ARM中斷體系 ① ARM體系中,在存儲地址的低位,固化了一個32字節的硬件中斷向量表。 ② 異常中斷發生時,程序計數器PC所指的位置不同,異常中斷就不同。中斷結束后,中斷不同,返回地址

2020-11-27 11:01:11 5505

5505

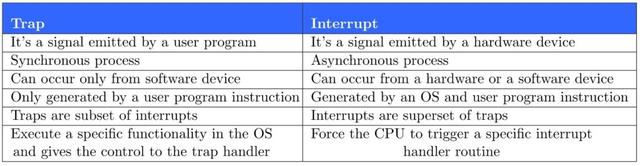

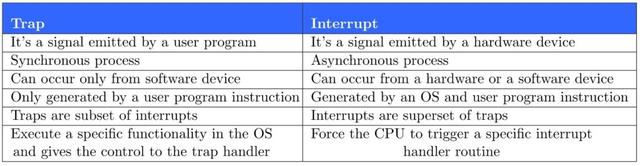

異常和中斷會暫停程序以響應硬件或軟件中的意外事件。中斷是異步事件,異常是同步事件,但是中斷和異常之間的區別也取決于具體情況。

2023-09-14 15:20:18 949

949

1、中斷和異常它支持16-4-1=11 種系統異常(同步)(保留了 4+1 個檔位),外加 240 個外部中斷輸入(異步)。在 CM3 中取消了 FIQ 的概念(v7 前的 ARM 都有這個 FIQ

2022-04-27 16:04:21

1、ARM中斷等待與異常處理優化中斷等待(延時):從檢測到某中斷請求,到執行了其服務例程的第一條指令時,已流逝的時間。可能造成中斷等待的情況:CPU正在處理另外一個相同或更高優先級的異常CPU正在

2022-05-10 17:21:48

對于ARM的處理器,中斷給處理器提供了觸覺,使處理器能夠感知到外界的變化,從而實時的處理。本系列博文,是以ARM cortex-A系列處理器,來介紹ARM的soc中,中斷的處理。ARM

2022-04-06 10:12:14

處理器模式和內部多線程和外部多處理器的處理器結構。在嵌入式系統中具有重要意義的異常中斷技術在S3C4510B系統中也體現了ARM體系獨有的一些的特點。本文根據S3C4510B系統的特點,分析了該系統中

2020-03-31 07:59:41

請問ARM與DSP間中斷通訊時,DSP端對應的是哪幾個中斷事件?

2018-06-21 02:19:07

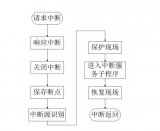

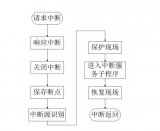

表:異常處理的大致流程主要針對中斷進行講解,其他的類似2. 中斷異常當手機接到一個電話時,電話模塊他會接到這個信號,電話和手機內部的CPU通過某個管腳相連,電話模塊通過這個管教把信號發給CPU,CPU

2022-04-26 09:37:10

。 當I位和F位為0時,irq pin上有中斷信號過來時,就會打斷arm的當前工作,并且切換到IRQ模式下,跳到相應的異常向量表(vector)位置去執行代碼。這個過程是自動的,但是返回到被中斷打斷

2017-10-13 21:16:06

中斷向量表|異常處理過程中斷隨機產生之后,怎么跳轉到中斷的處理程序中去(中斷向量表)SWI軟中斷指令:模擬CPU外面的某個硬件的管腳產生中斷信號4. 軟中斷處理程序實例原作者:西二旗指南

2022-05-05 10:16:31

ARM處理器中斷處理的理解

2012-08-20 12:36:05

ARM處理器異常相應過程:1、保存處理器當前狀態、中斷屏蔽位以及各個條件標志位。將當前程序狀態寄存器CPSR保存到對應的SPSR寄存器中實現。每個異常中斷都有對應的物理SPSR寄存器。2、設置

2021-12-14 08:57:34

在ARM處理器中一條指令的執行分為取指、譯碼、執行三個階段,由于指令流水線的存在造成當前執行的指令的地址是PC-8(ARM指令集),那么當前執行指令的下一條指令的地址應該是PC-4,所以在異常產生

2017-03-02 15:08:27

在ARM處理器中一條指令的執行分為取指、譯碼、執行三個階段,由于指令流水線的存在造成當前執行的指令的地址是PC-8(ARM指令集),那么當前執行指令的下一條指令的地址應該是PC-4,所以在異常產生

2017-03-07 16:40:45

,SWI異常中斷處理函數分為兩級,第一級的SWI處理函數用于從SWI指令中提取24位的立即數即中斷號,通第一級函數通過匯編語言、內嵌匯編來完成。第二級SWI異常中斷處理程序實現各個SWI的具體功能,第二級

2017-01-10 15:09:37

的異常向量地址取下一條指令執行,從而跳轉到相應的異常處理程序處。如果異常發生時,處理器處于Thumb狀態,則當異常向量地址加載入PC時,處理器自動切換到ARM狀態。ARM微處理器對異常的響應過程用偽碼

2011-01-27 11:13:20

的異常向量地址取下一條指令執行,從而跳轉到相應的異常處理程序處。如果異常發生時,處理器處于Thumb狀態,則當異常向量地址加載入PC時,處理器自動切換到ARM狀態。ARM微處理器對異常的響應過程用偽碼

2011-01-27 14:19:05

異常就是正在執行的指令,由于各種軟件或硬件故障被打斷,比如,在讀數據或指令時,訪問存儲器失敗、產生了一個外部硬件中斷等。當這些情況發生時,在ARM系統里,由異常和中斷處理程序做出相應的處理,當處理

2013-04-08 10:53:07

跳轉到從0x0地址開始的異常中斷向量表的0x18處,在向量表的0x18處,最簡單的指令為”B HandlerIRQ”。那程序員所要關心的就是實現具體的異常處理程序(HandlerIRQ)。當用ARM

2013-05-24 10:30:42

跳轉到從0x0地址開始的異常中斷向量表的0x18處,在向量表的0x18處,最簡單的指令為”B HandlerIRQ”。那程序員所要關心的就是實現具體的異常處理程序(HandlerIRQ)。當用ARM

2013-08-09 16:15:24

在學習與開發ARM處理器的過程中,一個不能繞開的話題就是異常處理流程。它在ARM的體系架構中,占據著不可動搖的重要地位。此處就以Coterx-A系列的ARM處理器簡單分析一下異常中斷處理流程。說異常

2016-11-11 09:55:57

在學習與開發ARM處理器的過程中,一個不能繞開的話題就是異常處理流程。它在ARM的體系架構中,占據著不可動搖的重要地位。此處就以Coterx-A系列的ARM處理器簡單分析一下異常中斷處理流程。說異常

2016-10-14 16:15:42

不同的異常中斷處理程序,返回地址以及使用的指令是不同的。ARM處理器對異常中斷的響應過程如下:(1).保存處理器當前狀態、中斷屏蔽位以及各條件標志位。這是通過將當前程序狀態寄存器CPSR的內容保存到將要執行

2020-08-28 08:09:17

ARM異常中斷返回的幾種情況異常中斷返回的幾種情況: 重要基礎知識:R15(PC)總是指向“正在取指”的指令,而不是指向“正在執行”的指令或正在“譯碼”的指令。一般來說,人們習慣性約定將“正在執行

2016-07-22 11:32:45

PC 就行了,具體指令為 MOV PC,LR(PC=A+4=LR)白話解釋:對于 SWI 和未定義指令異常: 發生異常時 pc 沒有更新,根據 ARM 的三級流水線原理,pc 沒有更新,仍然等于

2017-05-05 14:47:47

[學習引導]ARM異常中斷返回的幾種情況 異常中斷返回的幾種情況: 重要基礎知識:R15(PC)總是指向“正在取指”的指令,而不是指向“正在執行”的指令或正在“譯碼”的指令。一般來說,人們習慣性

2016-03-31 16:09:03

ARM嵌入式開發:中斷體系結構1)中斷簡介中斷,指計算機運行過程中,出現異常后,計算機停止當前工作保存當前狀態,然后轉向對這些異常的處理,在處理完成后再返回到停止時的狀態,繼續運行。2)ARM體系

2020-08-27 09:31:02

經典ARM微處理器包括7種異常:1、 復位異常2、 未定義指令異常3、 軟件中斷異常4、 預取指令異常5、 數據異常6、 IRQ(中斷)7、 FIQ(快速中斷)異常,單片機為中斷,籠統來講可以把異常

2021-07-16 07:04:57

、填寫什么值,就不細述了。這里用的單片機是FS4412多核ARM芯片。中斷的實現過程(程序的角度)中斷發生后,硬件自動跳轉到異常向量表中對應異常類型的位置,然后進行處理。處理過程,先進行現場保護(數據進棧

2020-08-31 08:22:53

ARM異常處理:只要正常的程序流被暫時中止,處理器就進入異常模式。例如響應一個來自外設的中斷。在處理異常之前,ARM內核保存當前的處理器狀態,這樣當處理程序結束是可以恢復執行原來的程序。注意:如果

2020-04-20 10:52:02

M0內核支持的資源Cortex-M0處理器最多支持32個外部中斷(通常稱作IRQ),還有一個被稱作不可屏蔽中斷的特殊中斷。中斷事件的異常處理通常被稱作中斷服務程序(ISR)。除此之外,M0處理器還

2021-12-21 06:50:48

Arm?-based 32-bit MCUs》的第89頁,文檔是給出的RTC的中斷事件是喚醒不了的:

這里請問,RTC的alarm中斷事件能否喚醒standby或者shutdown模式下?

2023-08-08 07:22:06

PC 就行了,具體指令為 MOV PC,LR(PC=A+4=LR)白話解釋:對于 SWI 和未定義指令異常: 發生異常時 pc 沒有更新,根據 ARM 的三級流水線原理,pc 沒有更新,仍然等于

2016-09-23 14:35:11

[學習引導]ARM異常中斷返回的幾種情況 異常中斷返回的幾種情況: 重要基礎知識:R15(PC)總是指向“正在取指”的指令,而不是指向“正在執行”的指令或正在“譯碼”的指令。一般來說,人們習慣性

2016-07-25 11:19:25

異常就是正在執行的指令,由于各種軟件或硬件故障被打斷,比如,在讀數據或指令時,訪問存儲器失敗、產生了一個外部硬件中斷等。當這些情況發生時,在ARM系統里,由異常和中斷處理程序做出相應的處理,當處理

2015-07-27 15:31:14

異常就是正在執行的指令,由于各種軟件或硬件故障被打斷,比如,在讀數據或指令時,訪問存儲器失敗、產生了一個外部硬件中斷等。當這些情況發生時,在ARM系統里,由異常和中斷處理程序做出相應的處理,當處理

2013-03-22 16:20:47

異常就是正在執行的指令,由于各種軟件或硬件故障被打斷,比如,在讀數據或指令時,訪問存儲器失敗、產生了一個外部硬件中斷等。當這些情況發生時,在ARM系統里,由異常和中斷處理程序做出相應的處理,當處理

2013-03-22 16:34:17

中斷指計算機CPU獲知某些事,暫停正在執行的程序,轉而去執行處理該事件的程序,當這段程序執行完畢后再繼續執行之前的程序。整個過程稱為中斷處理,簡稱中斷,而引起這一過程的事件稱為中斷事件。

2021-12-10 06:21:07

復制到發生的異常模式下SPSR中; b.模式切換:將CPSR模式位強制設置為與異常類型相對應的值,同時處理器進入到ARM執行模式,禁止所有IRQ中斷,當進入FIQ快速中斷模式時禁止FIQ中斷; c.

2018-05-10 10:58:33

中斷異常(SWI)和未定義異常(Undefined interrupt),CPU內部只有這幾個異常發生時其才會跳轉到異常向量表(即中斷向量)處執行特定的代碼。 所有連接在中斷處理器上的設備產生的中斷

2022-05-30 09:23:57

關于異常處理,分為三部分:ARM異常和模式:core處理異常時的操作,幾種模式介紹。Vector table:異常優先級lr偏移:幾種異常如何返回異常和中斷處理簡介在嵌入式系統中異常處理是核心之一

2021-12-14 09:23:07

時間內響應中斷次數。二、異常源在ARM體系結構中,存在7種異常處理。當異常發生時,處理器會把PC設置為一個特定的存儲器地址。這一地址放在被稱為向量表(vector table)的特定地址范圍內,向量

2022-08-18 15:26:04

' a6 nt當我們程序定義了該中斷,并且在程序運行的時候產生了 IRQ/FIQ 中斷,則此時的芯片運行過程:①中斷處理器利用IRQ請求線來告訴ARM,②ARM切換到 IRQ/FIQ 模式運行不同點

2022-04-13 11:44:12

,因為接下去的處理過程中使用的部分功能 只有ARM指令能完成, 而thumb指令完不成 (2)改變處理器模式,進入產生的異常對應的異常模式 (3)設置CPSR來禁止剛產生的同種類型的異常。 例

2022-04-26 09:29:21

以 ARM7TDMI處理器為例,詳細介紹 ARM內核的三種中斷:常規中斷、快中斷和軟件中斷;結合應用,給出優化的中斷處理程序的ARM指令代碼,對電子設計人員有較大的參考價值。

2009-04-09 10:01:19 18

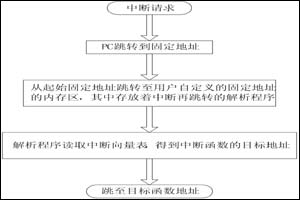

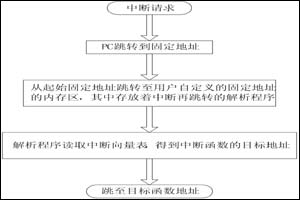

18 摘要:本文首先簡要概述了ARM處理器的異常中斷種類、響應和返回過程;然后重點討論了中斷解析程序的原理和實現,并分別給出了普通中斷和向量中斷的處理示例流程圖和詳細

2006-03-11 12:18:54 760

760

uCOS II在ARM處理器上移植過程中的中斷處理

uCOS II是一個源碼公開、可移植、可固化、可剪裁和搶占式的實時多任務操作系統,其大部分源碼是用ANSI C編寫,與處理器硬

2010-01-25 11:14:24 1532

1532 一.ARM處理器異常及其對應的模式當一個異常發生時,ARM處理器總是切換到ARM狀態(即非Thumb狀態)。Thumb指令集沒有包含進行異常處理時需要的一些指令

2011-04-18 08:34:05 2379

2379

在ARM體系結構中,硬件產生的外部中斷( IRQ) 具有單一的程序入口。為了識別中籽源,進而運行對應的中斷服務例程( ISR) ,程序需讀取中斷懸掛寄存器,獲得中斷號。在這種方式中,程序必須通

2011-06-27 15:45:24 64

64 對ARM處理器的普通中斷處理、任務切換中斷處理、可重人中斷處理和基于優先級的可重人性中斷處理的上下文保存技術進行分析與總結。為保證理論的正確性,核心的程序代碼都經過了

2011-07-06 12:08:09 4166

4166

以三星的 S3C4510 嵌入式平臺為基礎,討論了ARM7系統的中斷設計方案,包括ARM7中斷系統的特點、三星S3C4510的配置、中斷向量表的建立等,提出了中斷處理的一些優化措施

2011-08-16 14:15:12 198

198 文中介紹ARM9系列嵌入式微處理器的中斷體系結構 ,論述 Windows CE.net 的中斷處理過程 ,并在此基礎上給出基于 EP9301 微處理器的 Windows CE.net 4. 2 下進行中 斷程序開發的實例 。

2016-03-14 16:11:18 0

0 ARM單片機是大多數新手選擇的入門切入點,但由于知識的不足,在設計過程中新手們經常會遇到這樣或那樣的問題,ARM異常中斷返回就是這樣一種令人頭疼的問題。在ARM的使用問題中異常中斷返回是新手們較為苦惱的問題,本文就將對ARM異常中斷的集中情況進行總結,并給出了一些解決方法。

2016-04-28 10:52:56 1145

1145 ARM體系中的異常中斷及其應用

2017-09-22 16:51:52 4

4 3.4 異常中斷處理 異常或中斷是用戶程序中最基本的一種執行流程和形態。這部分主要對ARM架構下的異常中斷做詳細說明。 ARM有7種類型的異常,按優先級從高到低的排列如下:復位異常(Reset

2017-10-18 13:29:56 1

1 11.7 異常中斷產生指令(斷點指令) Thumb異常中斷產生指令與ARM指令集下的異常中斷指令十分相似。同ARM指令集相同,Thumb指令集中同樣包含兩條異常中斷產生指令:軟件中斷指令SWI用于

2017-10-19 09:32:58 0

0 當異常中斷發生時,系統執行完當前指令后,將跳轉到相應的異常中斷處理處執行。當異常中斷處理程序執行完成后,程序返回到發生中斷指令的下一條指令處繼續執行。在進入異常中斷處理程序時,要保存被中斷程序的執行線程。從中斷處理程序退出時要恢復被中斷程序的執行現場。

2017-12-16 08:57:03 4440

4440 嵌入式系統要求對異常及中斷處理器能快速響應。文中分析了ARM體系結構下 異常處理 特點,提出一種基于 ARM處理器 的高效異常處理解決方案,以LPC3250硬件平臺為基礎,對該方案進行了設計與實現

2018-02-03 03:38:01 1139

1139

本文介紹A了RM S3C4510B系統 的 異常中斷 機制,包括異常中斷的分類,響應與返回;中斷處理程序的安裝與調用;SWI,IRQ中斷的實例與關鍵代碼。隨著人們對于電子產品的要求越來越高

2018-02-03 05:32:01 1561

1561

ARM單片機是大多數新手選擇的入門切入點,但由于知識的不足,在設計過程中新手們經常會遇到這樣或那樣的問題,ARM異常中斷返回就是這樣一種令人頭疼的問題。在ARM的使用問題中異常中斷返回是新手們較為苦惱的問題,本文就將對ARM異常中斷的集中情況進行總結,并給出了一些解決方法。

2018-02-08 09:29:45 6187

6187

ARM單片機是大多數新手選擇的入門切入點,但由于知識的不足,在設計過程中新手們經常會遇到這樣或那樣的問題,ARM異常中斷返回就是這樣一種令人頭疼的問題。在ARM的使用問題中異常中斷返回是新手們較為苦惱的問題,本文就將對ARM異常中斷的集中情況進行總結,并給出了一些解決方法。

2018-05-26 07:11:00 2800

2800 ARM中異常中斷的類型問題分析總結 一、ARM中異常中斷的類型: 異常中斷名稱 含義 復位(Reset) 當處理器復位引腳有效時,系統產生復位異常中斷,程序跳轉到復位異常中斷處理程序處執行。復位

2018-04-05 10:51:00 1148

1148 以前,我一直很疑惑這個“ ARM異常 、 中斷以 及他們的 向量表 ”是怎么回事,他們到底是怎么實現的,沒有想到今天偶然看到(ARM System Developers Guide

2018-06-14 10:34:00 3975

3975

在處理器中,所謂中斷,是一個過程,即CPU在正在執行程序過程中,遇到外部/內部緊急事件需要處理,暫時中止當前程序執行轉而去

2018-06-27 10:06:00 7077

7077

第六講:GPIO、中斷和事件--《為ARM初學者導航》

2018-07-02 00:22:09 4368

4368

關于各種中斷在中斷返回時還需要給LR減去一個不同的偏移量的問題我覺得沒必要深入研究了,這還要涉及到ARM指令的流水線技術,平時寫中斷代碼都是用C寫的,沒必要知道這個。用到時再去查表即可。

2018-08-27 17:45:34 18582

18582

中斷處理過程可分為中斷響應、中斷處理和中斷返回三個階段。

2018-11-06 14:31:24 16719

16719

1. 在匯編中保存現場,然后調用C語言編寫的中斷處理程序,任務處理完成之后,再返回到匯編中恢復現場,并返回到斷點。其中C語言編寫的中斷處理程序,通過switch語句對INTOFFSET進行判斷,然后散轉執行對應的服務函數。

2018-11-15 16:17:02 817

817 器核的接口緊密相連,可以實現低延遲的中斷處理和有效處理地處理晚到的中斷。嵌套向量中斷控制器管理著包括核異常等中斷。

2018-11-16 15:35:40 7627

7627

ARM體系結構中,存在7種異常處理。當異常發生時,處理器會把PC設置為一個特定的存儲器地址。這一地址放在被稱為向量表(vector table)的特定地址范圍內。向量表的入口是一些跳轉指令,跳轉到專門處理某個異常或中斷的子程序。

2019-03-20 10:25:32 7

7 快速中斷請求(FIQ)要求具有最高優先級。如果分配給FIQ 的請求多于1 個,VIC將中斷請求“相或”后向ARM 處理器產生FIQ 信號。當只有一個中斷被分配為FIQ 時可實現最短的FIQ 等待時間

2019-09-27 17:26:00 14

14 當ARM異常中斷發生時,系統執行完當前指令后,將跳轉到相應的異常中斷處理程序處執行。當異常中斷處理程序執行完成后,程序返回到發生中斷指令的下條指令處執 行。在進入異常中斷處理程序時,要保存被中斷程序的執行現場,從異常中斷處理程序退出時,要恢復被中斷程序的執行現場。

2020-06-17 10:05:12 7046

7046 一、實驗目的(1)、學會使用 Embest IDE 編寫簡單的 C語言程序并進行調試;(2)、了解不同中斷觸發方式對中斷產生的影響;(3)、理解 S3C44B0X 處理器的中斷響應過程;(4)、熟練掌握如何進行 ARM 處理器中斷處理的軟件編程方法。

2020-07-14 16:42:00 21

21 外部中斷請求(IRQ) 當處理器的外部中斷請求引腳有效,而且CPSR的寄存器的I控制位被清除時,處理器產生外部中斷請求異常中斷。系統中個外設通過該異常中斷請求處理服務。

2020-08-27 14:21:29 2354

2354 概述 1.前言 中斷與異常在任何體系架構的芯片上都不會完全一樣。在arm的m系列芯片上需要理解NVIC,這個相對較為容易,而對于高端一些的芯片,中斷的處理就會復雜許多。比如arm上的gic

2021-01-07 10:41:46 3028

3028 異常是能夠引起程序流偏離正常流程的事件,當異常發生時,正在執行的程序就會被掛起,處理器轉而執行一塊與該事件相關的代碼(異常處理)。事件可以是外部輸入,也可以是內部產生的,外部產生的事件通常被稱作中斷

2021-10-12 17:14:18 4165

4165 慕課蘇州大學.嵌入式開發及應用.第二章.入門與軟件框架.ARM Cortex-M0+中斷機制和中斷編程步驟0 目錄2 入門與軟件框架2.7 ARM Cortex-M0+中斷機制和中斷編程步驟

2021-11-03 13:51:01 10

10 GIC 硬件原理GIC,Generic Interrupt Controller。是ARM公司提供的一個通用的中斷控制器。主要作用為:接受硬件中斷信號,并經過一定處理后,分發給對應的CPU...

2021-12-04 17:36:05 2

2 正常情況下一次紅外遙控按鍵應該產生16次外部中斷。診斷代碼卻顯示執行了32次外部中斷服務函數,也就是說一次中斷事件,產生了兩次中斷...

2022-01-25 19:00:02 3

3 我們可以假設ARM核心有兩根中斷引腳(實際上是看不見的),一根叫 irq pin, 一根叫fiq pin。在ARM的cpsr中,有一個I位和一個F位,分別用來禁止IRQ和FIQ。

2022-04-07 10:29:51 2918

2918 GIC 硬件原理 GIC,Generic Interrupt Controller。是ARM公司提供的一個通用的中斷控制器。主要作用為:接受硬件中斷信號,并經過一定處理后,分發給對應的CPU進行處理

2022-07-08 09:34:40 1647

1647 中斷是指計算機運行過程中,出現某些意外情況需主機干預時,機器能自動停止正在運行的程序并轉入處理新情況的程序,處理完畢后又返回原被暫停的程序繼續運行。

2023-02-01 17:04:56 653

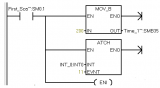

653 在200SMART系列PLC中共有三大類中斷事件,分別是:I/O中斷:I/O 中斷包括上升/下降沿中斷、高速計數器中斷和脈沖串輸出中斷。

2023-06-20 14:11:56 3869

3869

可以使用指令“ATTACH”為硬件中斷事件指定一個組織塊 (OB)。

2023-07-20 10:42:59 1067

1067

arm中斷是怎么實現的? 首先,了解什么是中斷。中斷是指在CPU執行某個程序時,突然發生的一些事件需要CPU立即停止正在執行的程序并去執行該事件相應的程序,這個過程叫做中斷。中斷是系統中一個重要

2023-09-05 16:22:23 618

618 正確處理,處理器可能會崩潰或數據損毀。ARM處理器有七種異常模式,即:重置模式、用戶模式、FIQ模式、IRQ模式、監督模式、中斷模式和異常模式。 1. 重置模式 當ARM處理器啟動時,它將進入重置模式。在這種模式下,處理器處于其最初狀態

2023-09-05 16:22:25 2036

2036 當異常中斷發生時,程序將當前執行指令的下一條指令的地址存入新的異常模式的鏈接寄存器LR中(R14_<mode>),以便程序在異常處理完后,能正確返回原程序。

2023-10-18 17:25:43 302

302 arm處理器有哪些中斷源?arm處理器對異常中斷的響應過程? ARM處理器是一種廣泛使用的嵌入式處理器,運行著各種不同類型的應用程序。為了保證應用程序的穩定性和正確性,ARM處理器需要在遇到異常

2023-10-19 16:35:59 675

675 機制。ARM處于操作系統和硬件之間,因此異常處理機制在有效性、安全性、可靠性方面必須經過充分測試和驗證。 ARM異常指令是程序中不受控制的分支或其他例外情況,如硬件故障、訪問非法地址、非法指令、軟件中斷等。雖然大多處理器都有異常響應和處理

2023-10-19 16:36:05 454

454 ARM異常返回值的合法值有哪些?各返回值分別代表什么? ARM異常返回值的合法值包括:中斷(IRQ)、中止(ABORT)、未定義指令(UND)、系統調用(SWI)、數據終端(DATA ABORT

2023-10-19 16:36:08 374

374 ARM中的異常中斷是如何實現進入中斷程序的?如何進入呢? 在計算機系統中,異常和中斷是兩個常見的概念。 在ARM中,異常和中斷的主要目的是幫助處理器響應與系統操作相關的事件。 由于處理器必須同時執行

2023-10-19 16:36:11 481

481 ARM9中斷中(C語言)如何實現復位功能,而不是返回中斷前的狀態? 在ARM9處理器的中斷中,當系統發生異常時,處理器會暫停正在執行的指令并處理中斷請求。處理中斷的方式有兩種,一種是通過向處理器發送

2023-10-19 16:42:43 641

641 時執行,處理中斷事件。 使能和禁止 IRQ 中斷是通過控制 CPSR 寄存器的 IRQ 位來實現的。當 IRQ 位為 1 時,IRQ 中斷是禁止的;當 IRQ 位為 0 時,IRQ 中斷是使能的。在特權

2023-10-19 16:42:46 612

612 在ARM處理器中,當一個中斷信號被觸發時,中斷控制器會發出一個中斷請求,并將該請求傳遞給CPU。 CPU接收到中斷請求后,會根據中斷號在中斷向量表中查找對應的中斷服務程序入口地址。 中斷

2023-10-30 17:19:02 731

731 今天來看一下中斷及ARM體系中對中斷的處理,直接進入正題。 中斷是指計算機運行過程中,出現某些意外情況需主機干預時,機器能自動停止正在運行的程序并轉入處理新情況的程序,處理完畢后又返回原被暫停的程序

2023-11-07 17:11:52 217

217

ARM中斷的實現是通過中斷控制器和異常模式實現的。ARM處理器通過中斷控制器來接收和處理外部的中斷信號,而異常模式用于處理內部的異常事件。本文將詳細介紹ARM中斷的原理和實現方式。 一、ARM中斷

2024-01-05 15:18:11 206

206

電子發燒友App

電子發燒友App

評論