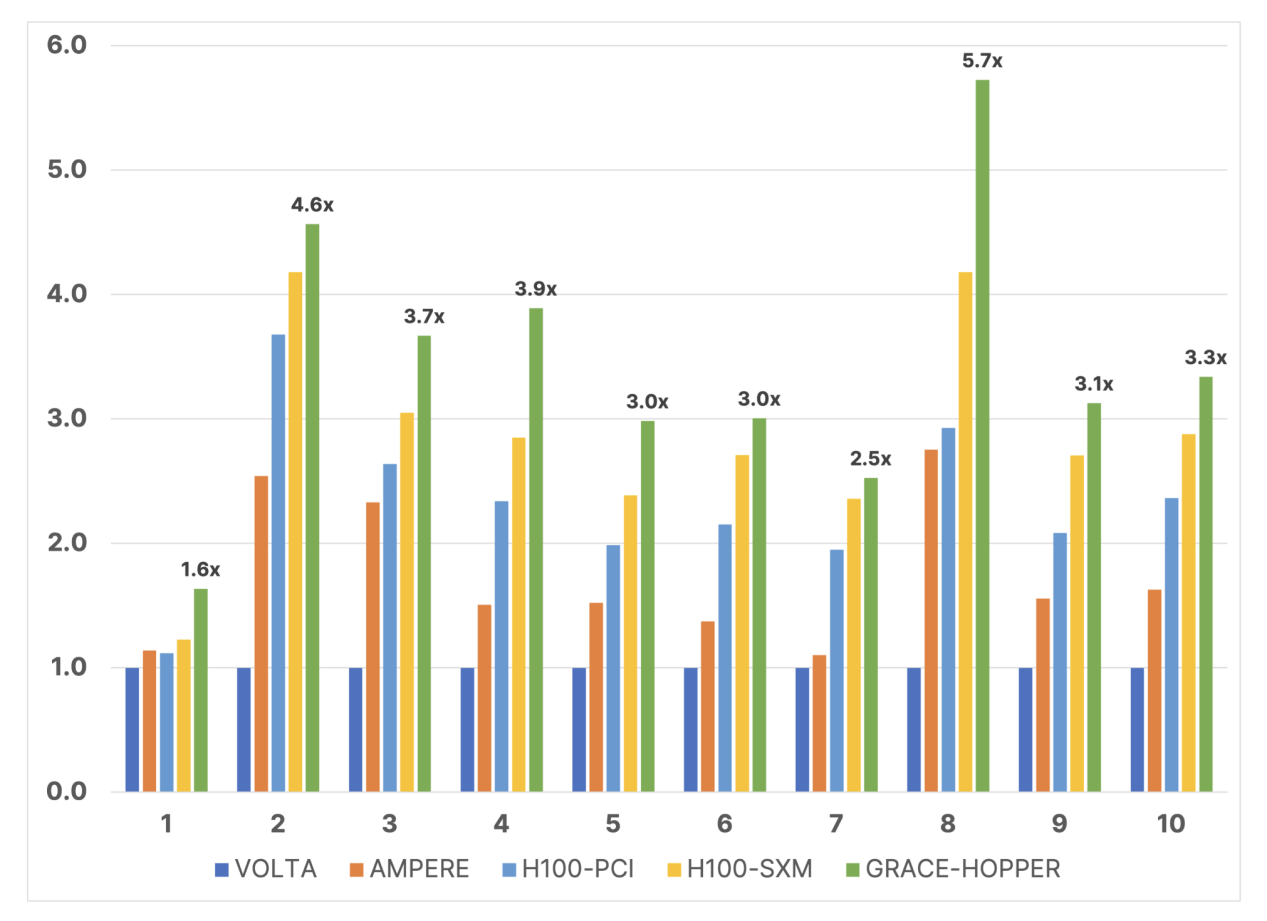

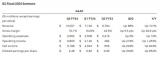

Nvidia 今天宣布,已向最新版本的 MLPerf 提交了其 Grace Hopper CPU+GPU Superchip 及其 L4 GPU 加速器的首個基準測試結果,MLPerf 是一項行業標準 AI 基準測試,旨在為衡量人工智能性能提供一個公平的競爭環境。不同的工作負載。今天的基準測試結果標志著 MLPerf 基準測試的兩個值得注意的新第一:添加了新的大型語言模型 (LLM) GPT-J 推理基準測試和改進的推薦模型。Nvidia 聲稱,在 GPT-J 基準測試中,Grace Hopper Superchip 的推理性能比其市場領先的 H100 GPU 之一高出 17%,并且其 L4 GPU 的性能高達英特爾 Xeon CPU 的 6 倍。

隨著該行業迅速發展到更新的人工智能模型和更強大的實施,該行業正在以驚人的速度發展。同樣,由 MLCommons 機構管理的 MLPerf 基準也在不斷發展,以通過新的 v3.1 修訂版更好地反映人工智能領域不斷變化的性質。

GPT-J 6B 是自 2021 年以來在現實工作負載中使用的文本摘要模型,現已在 MLPerf 套件中用作衡量推理性能的基準。與一些更先進的人工智能模型(例如 1750 億參數的 GPT-3)相比,GPT-J 60 億參數的 LLM 相當輕量,但它非常適合推理基準的角色。該模型總結了文本塊,并在對延遲敏感的在線模式和吞吐量密集型的離線模式下運行。MLPerf 套件現在還采用了更大的 DLRM-DCNv2 推薦模型(參數數量增加了一倍)、更大的多熱點數據集以及能夠更好地表示真實環境的跨層算法。

有了這個背景,我們可以在這里看到 Nvidia 的一些性能聲明。請注意,Nvidia 本身將這些基準提交給 MLCommons,因此它們可能代表高度調整的最佳情況。

Nvidia 還喜歡指出,它是唯一一家為 MLPerf 套件中使用的每個 AI 模型提交基準的公司,這是一個客觀真實的聲明。有些公司完全缺席,比如 AMD,或者只提交了一些選定的基準測試,比如英特爾的 Habana 和谷歌的 TPU。缺乏提交的原因因公司而異,但看到更多競爭對手加入 MLPerf 圈就太好了。

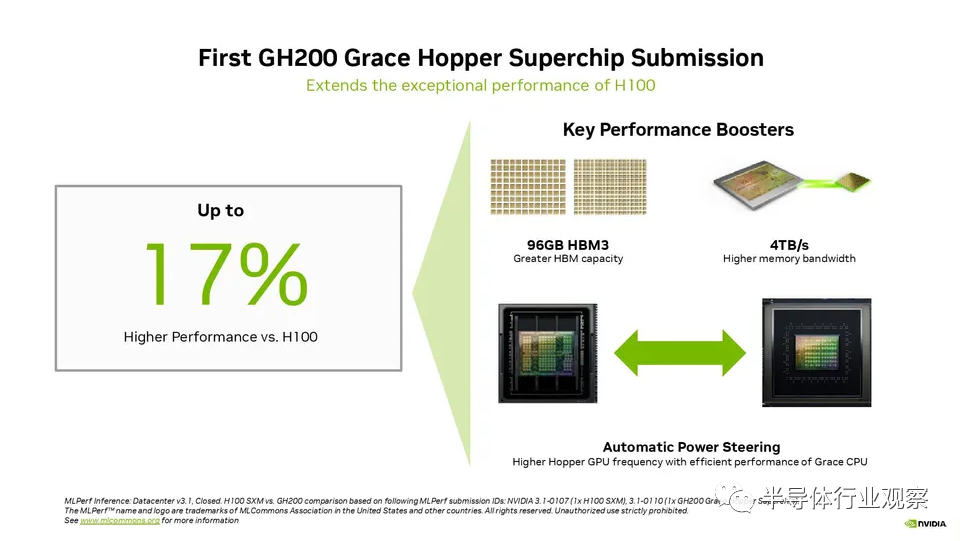

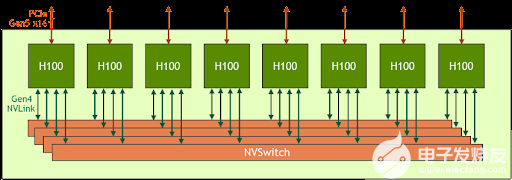

Nvidia 提交了第一個 GH200 Grace Hopper Superchip MLPerf 結果,強調 CPU+GPU 組合的性能比單個 H100 GPU 高出 17%。從表面上看,這令人驚訝,因為 GH200 使用與 H100 CPU 相同的芯片,但我們將在下面解釋原因。自然,配備 8 個 H100 的 Nvidia 系統的性能優于 Grace Hopper Superchip,在每項推理測試中都處于領先地位。

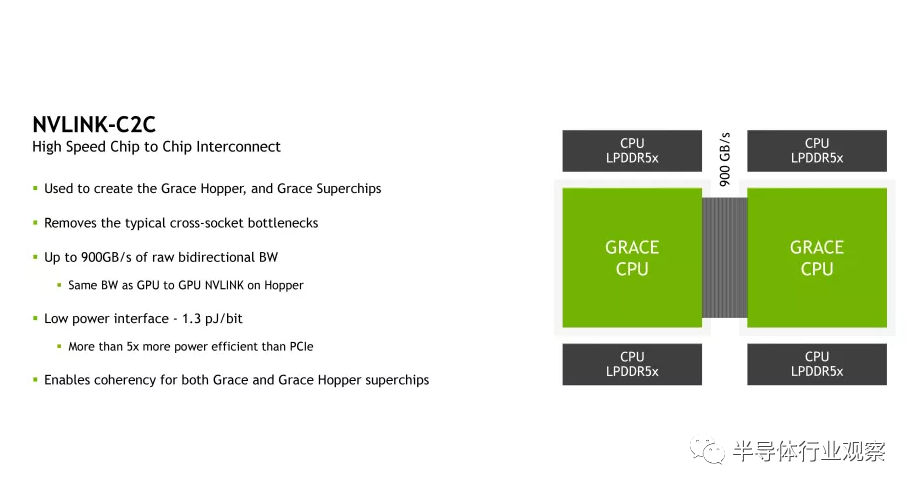

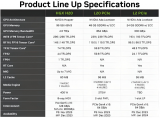

提醒一下,Grace Hopper Superchip 在同一塊板上結合了 Hopper GPU 和 Grace CPU,在兩個單元之間提供了具有 900GB/s 吞吐量的C2C 鏈路,從而提供了典型 PCIe 帶寬的 7 倍CPU 到 GPU 數據傳輸的連接,提高了 GH200 的可訪問內存帶寬,并通過包含 96GB HBM3 內存和 4TB/s GPU 內存帶寬的連貫內存池進行了增強。相比之下,在 HGX 中測試的對比 H100 僅具有 80GB 的 HBM3 (下一代 Grace Hopper 型號將在 2024 年第二季度擁有 144GB 的 HBM3e,速度快 1.7 倍)。

Nvidia 還推出了一種名為“ Automatic Power Steering”的動態動力轉移技術,該技術可以動態平衡 CPU 和 GPU 之間的功率預算,將溢出預算轉向負載最大的單元。這項技術被用于許多競爭性的現代 CPU+GPU 組合中,因此它并不新鮮,但它確實允許 Grace Hopper Superchip 上的 GPU 享受比 HGX 更高的電力傳輸預算,因為電力從Grace CPU——這在標準服務器中是不可能的。完整的 CPU+GPU 系統以 1000W TDP 運行。

大多數推理繼續在 CPU 上執行,隨著更大的模型變得越來越普遍,這種情況在未來可能會發生變化;對于 Nvidia 來說,用 L4 等小型低功耗 GPU 取代用于這些工作負載的 CPU 至關重要,因為這將推動大批量銷售。本輪 MLPerf 提交還包括 Nvidia L4 GPU 的第一批結果,該推理優化卡在 GPT-J 推理基準測試中的性能是單個 Xeon 9480 的 6 倍,盡管在超薄外形卡中功耗僅為 72W,不需要輔助電源連接。

Nvidia 還聲稱,通過測量 8 個 L4 GPU 與兩個上一代 Xeon 8380s CPU 的性能,視頻+AI 解碼-推理-編碼工作負載的 CPU 性能提高了 120 倍,這有點不平衡。這可能是為了直接比較單個機箱中可以容納的計算能力。盡管如此,值得注意的是,盡管四路服務器不是最適合這項工作,但仍然可以使用,而且較新的至強芯片在本次測試中可能會表現得更好一些。測試配置位于幻燈片底部的小字中,因此請務必注意這些細節。

最后,Nvidia 還提交了 Jetson Orin 機器人芯片的基準測試,顯示推理吞吐量提高了 84%,這主要是由軟件改進推動的。

重要的是要記住,在現實世界中,每個人工智能模型都作為較長系列模型的一部分運行,這些模型在人工智能管道中執行以完成特定的工作或任務。Nvidia 的上面的插圖很好地體現了這一點,在完成之前對一個查詢執行八種不同的 AI 模型 - 并且這些類型的 AI 管道擴展至 15 個網絡來滿足單個查詢并不是聞所未聞的。這是重要的背景,因為上面的面向吞吐量的基準往往側重于以高利用率運行單個 AI 模型,而不是現實世界的管道,需要更多的多功能性,多個 AI 模型串行運行才能完成給定的任務任務。

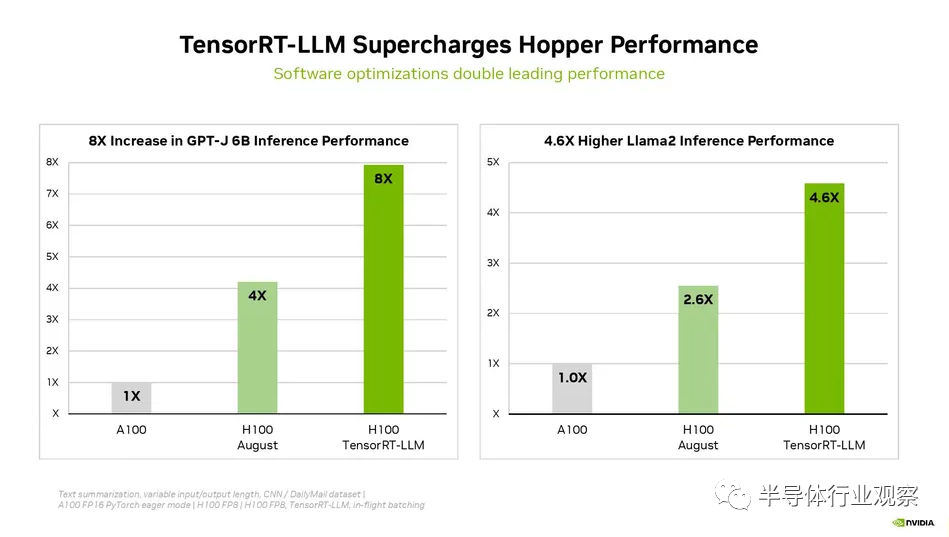

Nvidia 上周還宣布,其用于生成 AI 工作負載的 TensorRT-LLM 軟件可在推理工作負載中提供優化的性能,在 H100 GPU 上使用時總體性能提高一倍以上,且無需增加成本。Nvidia 最近提供了有關該軟件的詳細信息,并指出它還沒有為這一輪結果準備好這種推理增強軟件;MLCommons 要求 MLPerf 提交需要 30 天的準備時間,而 TensorRT-LLM 當時不可用。這意味著 Nvidia 的首輪 MLPerf 基準測試應該會在下一輪提交中看到巨大的改進。

Nvidia Grace Hopper CPU的設計詳解

正如我們在之前的報道中指出,Nvidia 的 Grace CPU 是該公司第一款專為數據中心設計的純 CPU Arm 芯片,一塊主板上有兩個芯片,總共 144 個核心,而 Grace Hopper Superchip 則在主板上結合了 Hopper GPU 和 Grace CPU。

根據Nvidia之前透露,Grace CPU采用臺積電4N工藝。臺積電將“N4”4nm工藝列入其5nm節點家族之下,將其描述為5nm節點的增強版。Nvidia 使用該節點的一種特殊變體,稱為“4N”,專門針對其 GPU 和 CPU 進行了優化。

隨著摩爾定律的衰落,這些類型的專用節點變得越來越普遍,并且隨著每個新節點的出現,縮小晶體管變得更加困難和昂貴。為了實現 Nvidia 4N 等定制工藝節點,芯片設計人員和代工廠攜手合作,使用設計技術協同優化 (DTCO) 為其特定產品調整定制功耗、性能和面積 (PPA) 特性。

Nvidia 此前曾透露,其 Grace CPU 使用現成的 Arm Neoverse 內核,但該公司仍未具體說明使用哪個具體版本。不過,Nvidia透露Grace采用Arm v9內核,支持SVE2、Neoverse N2平臺是 Arm 第一個支持 Arm v9 和 SVE2 等擴展的 IP。N2 Perseus 平臺采用 5nm 設計(請記住,N4 屬于臺積電的 5nm 系列),支持 PCIe Gen 5.0、DDR5、HBM3、CCIX 2.0 和 CXL 2.0。Perseus 設計針對每功率(瓦特)性能和每面積性能進行了優化。Arm 表示,其下一代核心 Poseidon 直到 2024 年才會上市,考慮到 Grace 的發布日期為 2023 年初,這些核心的可能性較小。

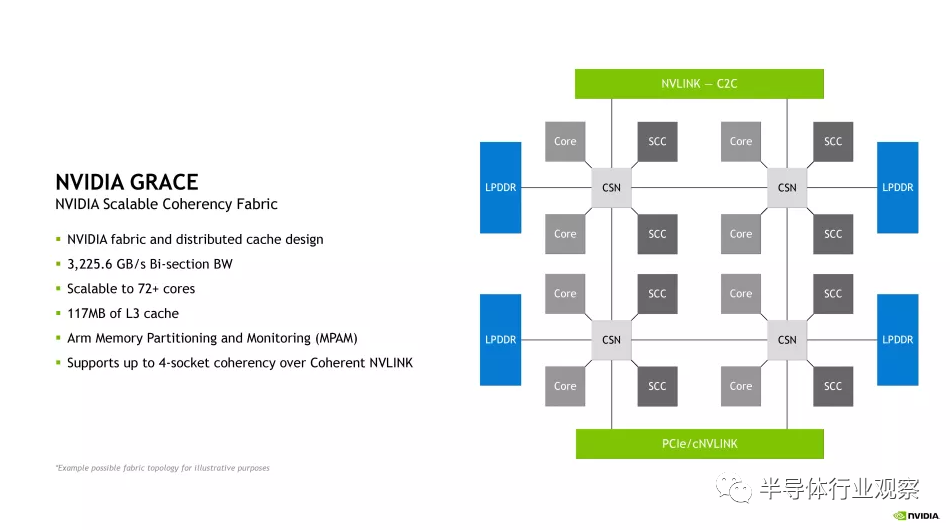

Nvidia 的新 Nvidia 可擴展一致性結構 (SCF:Nvidia Scalable Coherency Fabric ) 是一種網狀互連,看起來與與 Arm Neoverse 核心一起使用的標準CMN-700 相干網狀網絡非常相似。

Nvidia SCF 在各種 Grace 芯片單元(如 CPU 內核、內存和 I/O)之間提供 3.2 TB/s 的對分帶寬,更不用說將芯片與其他單元連接起來的 NVLink-C2C 接口了。無論是另一個 Grace CPU 還是 Hopper GPU。

該網格支持 72 個以上核心,每個 CPU 總 L3 緩存為 117MB。Nvidia 表示,上面專輯中的第一個框圖是“用于說明目的的可能拓撲”,其對齊方式與第二個圖并不完全一致。

該圖顯示了具有八個 SCF 緩存分區 (SCC:SCF Cache partitions ) 的芯片,這些分區似乎是 L3 緩存片(我們將在演示中了解更多詳細信息)以及八個 CPU 單元(這些似乎是核心集群)。SCC 和內核以兩個為一組連接到緩存交換節點 (CSN),然后 CSN 駐留在 SCF 網狀結構上,以提供 CPU 內核和內存與芯片其余部分之間的接口。SCF 還通過 Coherent NVLink 支持最多四個插槽的一致性。

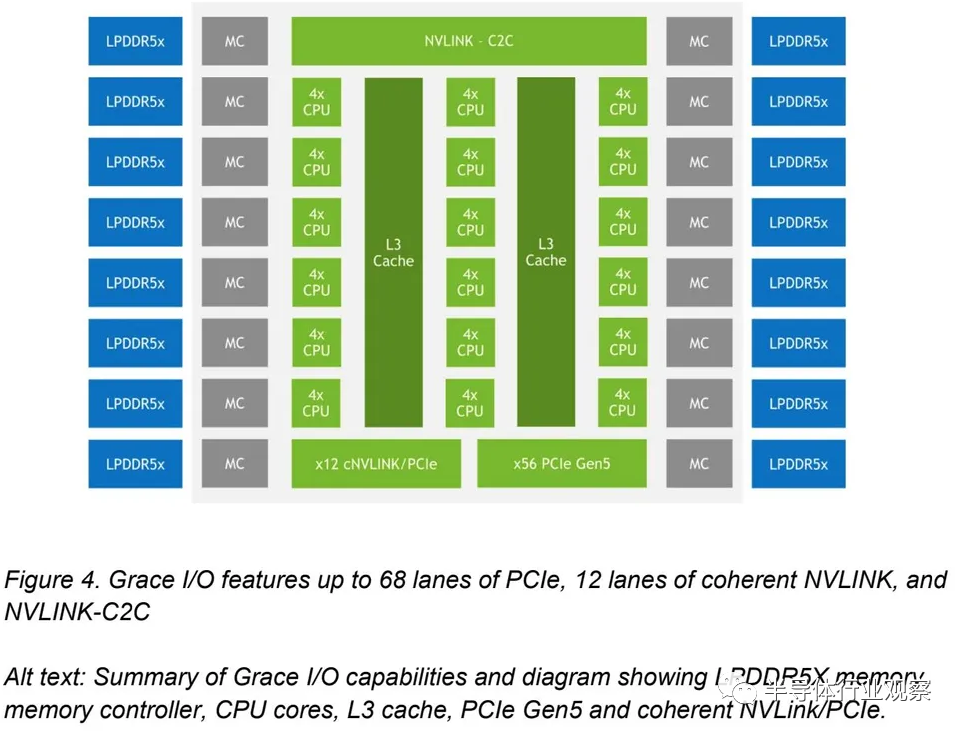

Nvidia 還分享了這張圖,顯示每個 Grace CPU 支持最多 68 個 PCIe 通道和最多 4 個 PCIe 5.0 x16 連接。每個 x16 連接支持高達 128 GB/s 的雙向吞吐量(x16 鏈路可以分為兩個 x8 鏈路)。我們還看到了 16 個雙通道 LPDDR5X 內存控制器 (MC)。

然而,此圖與第一個圖不同,它將 L3 緩存顯示為連接到四核 CPU 集群的兩個連續塊,這比之前的圖更有意義,并且芯片中總共有 72 個核心。但是,我們在第一個圖中沒有看到單獨的 SCF 分區或 CSN 節點,這造成了一些混亂。我們將在演示期間解決這個問題,并根據需要進行更新。

Nvidia 告訴我們,可擴展一致性結構 (SCF) 是其專有設計,但 Arm 允許其合作伙伴通過調整核心數量、緩存大小以及使用不同類型的內存(例如 DDR5 和 HBM)來定制 CMN-700 網格,以及選擇各種接口,例如 PCIe 5.0、CXL 和 CCIX。這意味著 Nvidia 可能會為片上結構使用高度定制的 CMN-700 實現。

GPU 喜歡內存吞吐量,因此 Nvidia 自然而然地將目光轉向提高內存吞吐量,不僅限于芯片內部,還包括 CPU 和 GPU 之間的內存吞吐量。Grace CPU 具有 16 個雙通道 LPDDR5X 內存控制器,最多可支持 32 個通道,支持高達 512 GB 的內存和高達 546 GB/s 的吞吐量。Nvidia 表示,由于容量和成本等多種因素,它選擇了 LPDDR5X 而不是 HBM2e。同時,與標準 DDR5 內存相比,LPDDR5X 的帶寬增加了 53%,每 GB 功耗降低了 1/8,使其成為更好的整體選擇。

Nvidia 還推出了擴展 GPU 內存 (EGM),它允許 NVLink 網絡上的任何 Hopper GPU 訪問網絡上任何 Grace CPU 的 LPDDR5X 內存,但保持本機 NVLink 性能。

Nvidia的目標是提供一個可以在CPU和GPU之間共享的統一內存池,從而提供更高的性能,同時簡化編程模型。Grace Hopper CPU+GPU 芯片支持具有共享頁表的統一內存,這意味著芯片可以與 CUDA 應用程序共享地址空間和頁表,并允許使用系統分配器來分配 GPU 內存。它還支持 CPU 和 GPU 之間的native atomics。

CPU 核心是計算引擎,但互連是定義計算未來的戰場。移動數據比實際計算數據消耗更多的電量,因此更快、更有效地移動數據,甚至避免數據傳輸,是一個關鍵目標。

Nvidia 的Grace CPU在一塊板上由兩個 CPU 組成,而 Grace Hopper Superchip 在同一塊板上由一個 Grace CPU 和一個 Hopper GPU 組成,旨在通過專有的 NVLink 芯片最大限度地提高單元之間的數據傳輸。芯片間 (C2C) 互連并提供內存一致性,以減少或消除數據傳輸。

Nvidia 分享了有關其 NVLink-C2C 互連的新細節。提醒一下,這是一種芯片到芯片和芯片到芯片互連,支持內存一致性,可提供高達 900 GB/s 的吞吐量(是 PCIe 5.0 x16 鏈路帶寬的 7 倍)。該接口使用 NVLink 協議,Nvidia 使用其 SERDES 和 LINK 設計技術設計了該接口,重點關注能源和面積效率。物理 C2C 接口跨標準 PCB 運行,因此不使用專門的中介層。

NVLink-C2C 還支持行業標準協議,例如 CXL 和 Arm 的 AMBA 相干集線器接口(CHI — Neoverse CMN-700 網格的關鍵)。它還支持多種類型的連接,從基于 PCB 的互連到硅中介層和晶圓級實現。

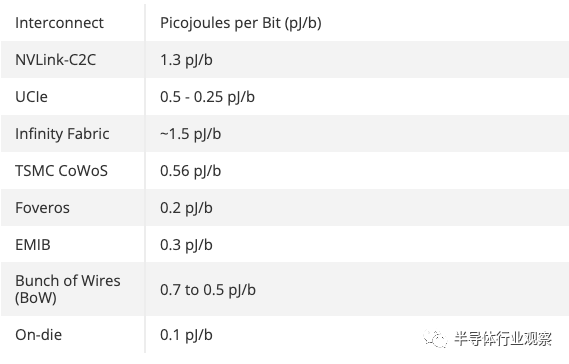

電源效率是所有數據結構的一個關鍵指標,今天 Nvidia 表示,傳輸的數據每比特 (pJ/b) 鏈路消耗 1.3 皮焦耳 (pJ/b)。這是 PCIe 5.0 接口效率的 5 倍,但它的功率是未來將上市的 UCIe 互連的兩倍多(0.5 至 0.25 pJ/b)。封裝類型各不相同,C2C 鏈路為 Nvidia 的特定用例提供了性能和效率的堅實結合,但正如您在上表中看到的,更高級的選項可提供更高水平的功效。

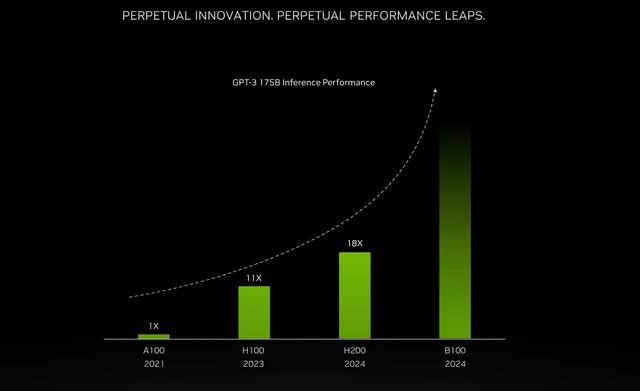

Nvidia 將H100 推理性能提高一倍的秘訣

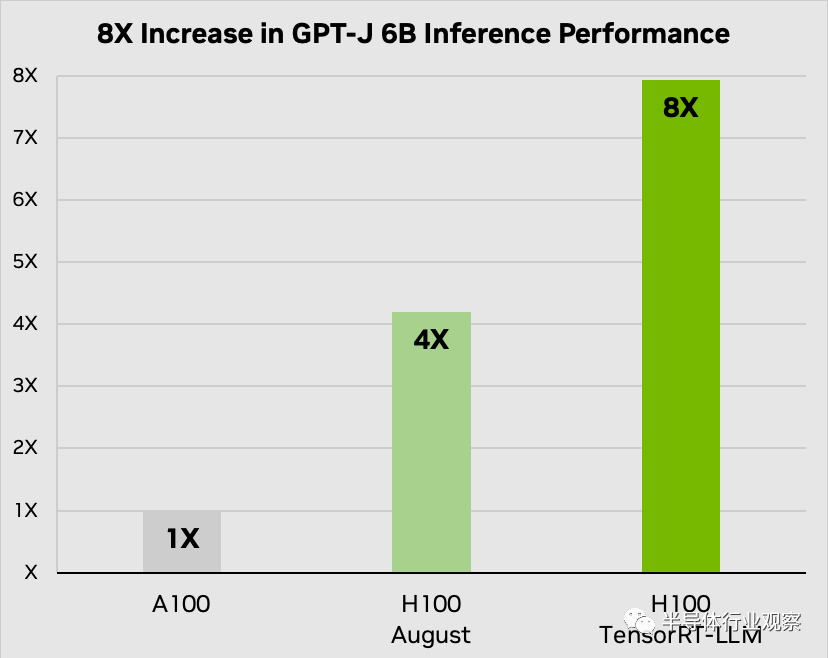

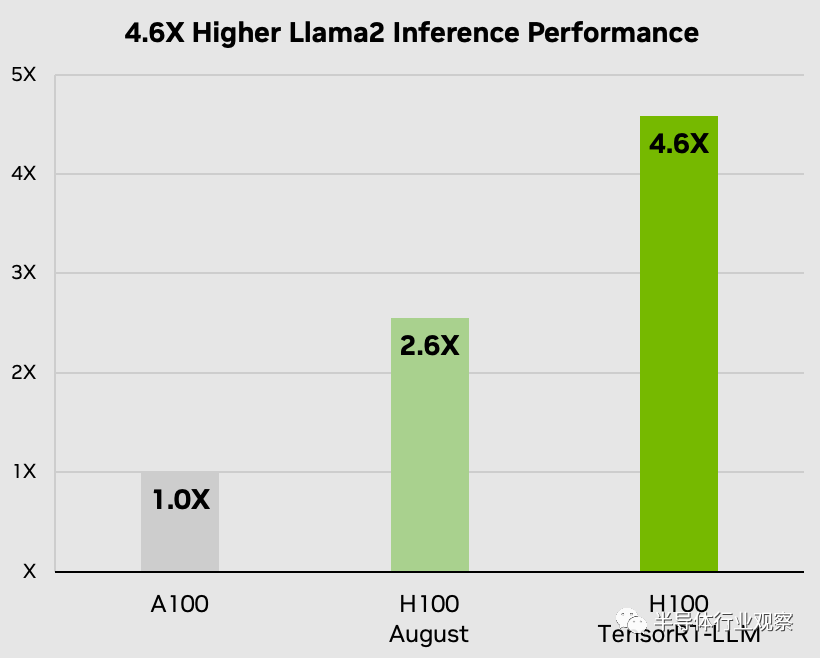

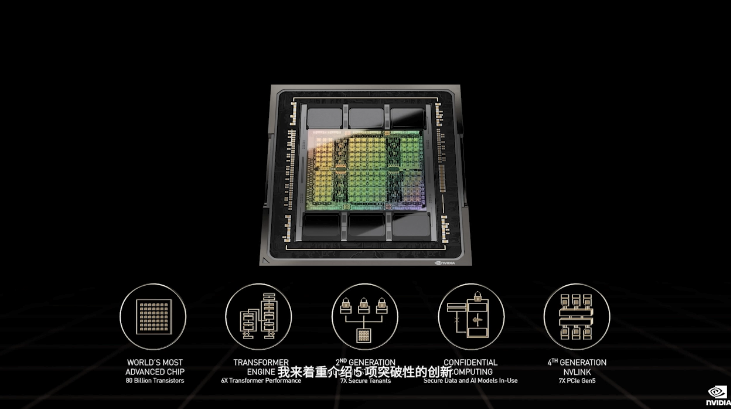

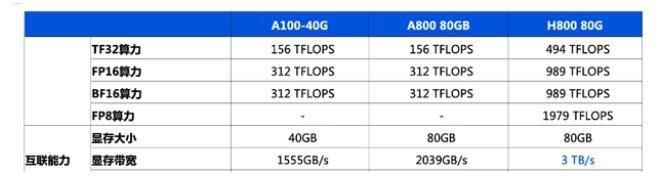

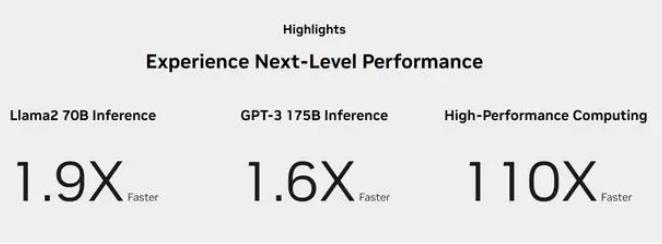

Nvidia 表示,其新的 TensorRT -LL開源軟件可以顯著提高 GPU 上大型語言模型 (LLM) 的性能。據該公司稱,Nvidia TensorRT-LL 的功能使其 H100 計算 GPU 在具有 60 億個參數的 GPT-J LLM 中的性能提高了兩倍。重要的是,該軟件可以實現這種性能改進,而無需重新訓練模型。

Nvidia 專門開發了 TensorRT-LLM,以提高 LLM 推理的性能,Nvidia 提供的性能圖形確實顯示,由于適當的軟件優化,其 H100 的速度提升了 2 倍。Nvidia TensorRT-LLM 的一個特別突出的功能是其創新的動態批處理技術。該方法解決了LLM動態且多樣化的工作負載,這些工作負載的計算需求可能存在很大差異。

動態批處理優化了這些工作負載的調度,確保 GPU 資源得到最大程度的利用。因此,H100 Tensor Core GPU 上的實際 LLM 請求吞吐量翻倍,從而實現更快、更高效的 AI 推理過程。

Nvidia 表示,其 TensorRT-LLM 將深度學習編譯器與優化的內核、預處理和后處理步驟以及多 GPU/多節點通信原語集成在一起,確保它們在 GPU 上更高效地運行。這種集成得到了模塊化 Python API 的進一步補充,它提供了一個開發人員友好的界面,可以進一步增強軟件和硬件的功能,而無需深入研究復雜的編程語言。例如,MosaicML 在 TensorRT-LLM 之上無縫添加了所需的特定功能,并將它們集成到其推理服務中。

Databricks 工程副總裁 Naveen Rao 表示:“TensorRT-LLM 易于使用,功能齊全,包括令牌流、動態批處理、分頁注意力、量化等,而且效率很高。” “它為使用 NVIDIA GPU 的LLM服務提供了最先進的性能,并使我們能夠將節省的成本回饋給我們的客戶。”

Nvidia H100 與 TensorRT-LLM 結合使用時的性能令人印象深刻。在 NVIDIA 的 Hopper 架構上,H100 GPU 與 TensorRT-LLM 配合使用時,性能是 A100 GPU 的八倍。此外,在測試 Meta 開發的 Llama 2 模型時,TensorRT-LLM 的推理性能比 A100 GPU 提高了 4.6 倍。這些數字強調了該軟件在人工智能和機器學習領域的變革潛力。

最后,H100 GPU 與 TensorRT-LLM 結合使用時支持 FP8 格式。此功能可以減少內存消耗,而不會損失模型準確性,這對于預算和/或數據中心空間有限且無法安裝足夠數量的服務器來調整其 LLM 的企業來說是有益的。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論