為了在USB 3.0中實現(xiàn)數(shù)據(jù)的8 b/10 b編解碼,把8b/10b編解碼分解成5 b/6 b編解碼和3 b/4 b編解碼,然后在FPGA上實現(xiàn)了具體的硬件電路。

2011-11-30 11:38:18 2803

2803

53小波的EZW壓縮編解碼FPGA實現(xiàn),有了解的麻煩指點下,謝謝!

2014-06-22 11:25:36

HDB3碼型變換實驗 一、實驗目的1、了解二進制單極性碼變換為HDB3碼的編碼規(guī)則,掌握它的工作原理和實現(xiàn)方法。2、通過調測電路,熟悉并掌握調測電路的一般規(guī)律與方法,學會分析電路

2009-10-11 09:00:20

和最常用的NRZ碼(Non—Return Zero,非歸零碼)相比,HDB3碼具有很多優(yōu)點,例如:消除了NRZ碼的直流成分,具有時鐘恢復和更好的抗干擾性能,這使它更適合于長距離信道傳輸。

2019-09-26 09:12:23

描述XC9572和XC95108 DIY CPLD實驗板的PCB該板需要外部 JTAG 電纜來對器件進行編程。JTAG 電纜可以是傳統(tǒng)計算機并行端口或現(xiàn)代 USB JTAG 編程器。一條并行端口

2022-08-05 07:09:52

是否可以直接替換部件號:XC9572-7PQG100C?先謝謝你以上來自于谷歌翻譯以下為原文Is there a direct replacement for part number: XC9572-7PQG100C? Thank you in advance

2019-04-30 14:56:10

最近老師讓我去找用ARM實現(xiàn)H.264編解碼的源代碼,找了很久也沒找到,而且我也是才接觸這方面的東西,對這方面也不懂,請各位大神指教,小弟定當感激不盡!

2014-05-25 21:22:23

RT用labVIEW實現(xiàn)一種RFID編解碼的仿真

2013-05-14 23:21:59

Android硬編解碼主要用MediaCodec實現(xiàn)。以下是Android官方的使用說明:我就用MediaCodec做一個demo,實現(xiàn)硬編解碼攝像的的preview數(shù)據(jù)。demo界面如圖:程序界面

2022-04-11 14:39:36

描述IDE68K 68000 插座 IDE 板,適用于 Amiga,V429 39/40 針 0.1" 接頭XC95144XL-TQ100 替代 XC9572XL,也可以使用 5 伏 XC9572 用短路代替穩(wěn)壓器。

2022-07-28 07:53:40

TI有沒有集成硬件視頻編解碼(如H.264 D1)的芯片,不是那種davinci用dsp軟件實現(xiàn)的。

如AM3517之類是否有此功能?

謝謝

2018-06-21 04:29:29

關于labview的HDB3碼型輸出的設計

2018-12-11 16:54:52

小弟最近在做2013年國賽題目紅外通信裝置,其實核心就是對音頻信號進行PCM編解碼,其中我們用到了MC14LC5480這款PCM編解碼芯片,其中有幾個疑問1.看全英文的文檔介紹說有四種工作模式,但我

2016-03-15 11:30:37

初識紅外編解碼

2021-08-16 06:35:47

請問各位大哥誰有基于XC9572實現(xiàn)HDB3編解碼的完整電路及VHDL程序,發(fā)一份給我,在此先謝謝了。郵箱251093703@qq.com

2013-05-30 15:00:30

數(shù)字通信過程中,基帶信道對傳輸信號的碼型有嚴格的限制。針對數(shù)字光纖通信傳輸信號碼型的要求,介紹了CMI碼的編解碼原理,提出了一種基于可編程邏輯器件EPM240T100C5實現(xiàn)CMI編解碼的方法,給出

2010-05-06 09:06:05

同時滿足(3)中的兩個要求;(5)V碼后面的傳號碼極性也要交替。例如:其中的±V脈沖和±B脈沖與±1脈沖波形相同,用V或B符號表示的目的是為了示意非“0”碼是由原始碼的“0”變換而來的。3.HDB3解碼

2016-04-15 21:54:08

基于FPGA的HDB3編解碼系統(tǒng),誰有這方面的資料,謝了!

2013-04-07 15:14:45

1. 介紹視頻編解碼的主要工作:編碼,即將原始的視頻信息壓縮為既定格式的數(shù)據(jù)。解碼,即將已知格式的數(shù)據(jù)還原為視頻信息。本教程將通過啟動相機捕獲預覽幀,轉換為視頻原始數(shù)據(jù)并使用HarmonyOS視頻

2021-09-17 10:56:45

在KL產品上實現(xiàn)G.726語音編解碼方案

2022-12-09 07:18:13

求助!大佬們,問一下用FPGA實現(xiàn)卷積碼編解碼的難度。

2023-10-16 23:26:26

目錄一、硬件連接(STM32F407VETx、仿真器)二、配置Debugger三、通過串口協(xié)議,實現(xiàn)對jpeg圖片編解碼后傳回電腦驗證四、結果一、硬件連接(STM32F407VETx、仿真器)1

2022-01-19 06:51:06

ADPCM算法及其編解碼器原理是什么?如何去設計ADPCM語音編解碼電路?

2021-05-06 06:37:15

有懂得兩兆誤碼儀的么?哪位大神能幫忙設計一個簡單的HDB3的電路?不求測試誤碼,能測通斷就行

2019-11-22 22:54:53

我目前使用XC9572,44針PLCC完成了99%的設計,除了它幾乎不適合。設計用途:2 x CBD16CE(16位二進制計數(shù)器)1 x M16_1E(16至1 MUX)3 x BUFE8(8位

2018-10-10 10:53:48

數(shù)字通信系統(tǒng)的某些應用可對基帶信號不載波調制而直接傳輸,其中傳輸線路對碼型的要求如下:信碼中不宜有直流分量,低頻分量應盡可能的少,碼型要便于時鐘信號提取。

2019-08-16 08:01:42

AC4830xC-C芯片的基本性能及工作原理是什么?TCM38C17芯片的基本性能及工作原理是什么?一種基于AC4830xC-C和TCM38C17的四路語音編解碼系統(tǒng)的實現(xiàn)方案

2021-06-03 06:22:07

【STM32】基帶HDB3編解碼系統(tǒng)設計一、設計背景及說明??長期以來,人類進行信息交互的基本方式不外乎語言、文字和圖像。隨著數(shù)字技術的發(fā)展,三大信息網(wǎng):電話、電視、和因特網(wǎng)在數(shù)字通信的平臺

2021-08-09 07:44:35

你好,我想這是一個新手問題。我有12塊PCB,上面有XC9572 QFP100。只有4個我可以編程,其余的一直響應失敗。 (LPT端口上的簡單電纜)使用Impact,可以編程4,我可以讀取設備ID

2020-03-13 08:51:08

求HDB3碼的labview

2017-11-13 20:50:22

如何去實現(xiàn)MPEG-4視頻編解碼的硬件設計?如何去實現(xiàn)MPEG-4視頻編解碼的軟件設計?

2021-06-04 06:12:55

在做HDB3編譯碼的程序,程序編譯沒有報錯。quartus自動生成了測試文件,但剛接觸FPGA不久激勵部分的程序不知道怎么改,求大神幫忙看下測試文件怎么改,謝謝。附HDB3編碼程序:--HDB3編碼

2016-09-13 22:30:19

端口設備編程的信息(使36個用戶i / o pins)不公開。我遇到了XC9572器件,它有34個我需要的引腳,并且具有公開的高電壓編程協(xié)議。通過少一個GMD引腳和一個較少的電源引腳實現(xiàn)2個額外

2020-03-25 08:57:04

本帖最后由 luna 于 2011-3-3 14:44 編輯

PCM編解碼系統(tǒng)中的編碼器,傳輸變換兩路音頻信號為一路帶有冗余信息的PCM信號。冗余信息包含糾正記錄或重放期間產生的隨機誤差所增加

2011-03-03 00:08:17

RS編解碼原理是什么如何實現(xiàn)RS編解碼器?

2021-04-29 06:11:40

2C64 XC2C128 XC2C256 XC2C512 XC9536 XC9572 XC95144 XC95216 XC95288Lattice:LCMXO2-256 L

2021-11-22 22:16:03

2C32 XC2C64 XC2C128 XC2C256 XC2C512 XC9536 XC9572 XC95144 XC95216 XC95288Lattice:LCMXO2

2021-11-22 22:21:12

The XC9572 is a high-performance CPLD providingadvanced in-system programming and test capabilities

2009-03-28 15:20:12 85

85 XC9572是XILINX公司生產的一款高性能可編程邏輯器件。它內含4個36V18功能塊,并具有1600個可用系統(tǒng)門。其系統(tǒng)結構如圖1所示。從結構上看,XC9

2009-03-28 15:24:23 364

364 HDB3 碼無直流分量,具有時鐘恢復和較好的抗干擾能力。本文提出使用HDB3碼用于高速長距離的數(shù)據(jù)傳輸, 并給出使用單片機AT89C51 控制E1 收發(fā)芯片DS2153Q 實現(xiàn)NRZ-HDB3 的碼制轉換,包括

2009-04-15 11:31:16 19

19 for aManchester Encoder Decoder. The reasons to use Manchester code are discussed. The codecan be compiled into either the Xilinx XC9572 or XCR

2009-05-13 13:30:39 157

157 無中繼長線傳輸會出現(xiàn)信宿端信號嚴重失真的現(xiàn)象,矯正器是長線傳輸系統(tǒng)中的重要一環(huán)。本文提出一種對長線傳輸系統(tǒng)中HDB3 編碼的失真信號進行矯正的算法。該算法采用先進先出

2009-09-08 16:08:21 9

9 在對G.726 語音編解碼標準分析的基礎上給出了基于FPGA 的DSP 設計流程,利用MATLAB/Simulink、DSP Builder 和SOPC Builder 工具設計了G.726 語音編解碼器,通過仿真實驗驗證了所設計的編解碼器模

2009-11-30 14:59:24 12

12 EDA卷積碼編解碼器實現(xiàn)技術針對某擴頻通信系統(tǒng)數(shù)據(jù)糾錯編碼的需要, 構造并分析了(2 , 1 , 6) 卷積碼編解碼器的基本工作原理, 提出了基于MAX + plus Ⅱ開發(fā)平臺的(2 , 1 ,

2009-12-05 16:17:42 0

0 HDB3碼是基帶傳輸系統(tǒng)中經(jīng)常采用的傳輸碼型。本文闡述了HDB3碼編解碼電路的基本原理,在MAX+PLUSⅡ軟件平臺上,給出了利用復雜可編程邏輯器件設計的HDB3碼編解碼電路,并進行了編譯和

2010-02-24 15:59:48 51

51 基于AMI/HDB3編解碼原理,設計了一種用CD22103集成芯片實~AMI/HDB3編解碼的硬件電路.詳細分析了編解碼的實現(xiàn)過程、單雙極性變換及位同步,最后給出實驗結果并分析了編解碼時延

2010-04-13 08:56:28 145

145 摘要:在數(shù)字通信中,選擇合適在信道中傳輸?shù)拇a型是十分重要的,HDB3碼是比較常用的信道傳輸碼型,因此HDB3碼的編譯碼就顯得非常重要.多數(shù)的數(shù)字基帶信號用單極性不歸零碼(NR

2010-05-17 09:08:49 41

41 分析了HDB3編解碼原理,提出了一種適合于在現(xiàn)場可編程門陣列FPGA上實現(xiàn)的HDB3編譯碼器的硬件實現(xiàn)方案,在FPGA上完成了布局布線和時序仿真,最后給出了仿真和實驗結果。結果表明該方

2010-07-28 17:36:41 32

32 采用多路復用流水線的思想,設計基于FPGA仿真測試的RS編解碼的改進IBM算法,使用Verilog硬件編程語言實現(xiàn),進一步提高RS編解碼器的運行速度及糾錯能力,擴大應用范圍。系統(tǒng)設計

2010-12-22 17:02:40 25

25 HDB3碼無直流分量,具有時鐘恢復和較好的抗干擾能力。本文提出使用HDB3碼用于高速長距離的數(shù)據(jù)傳輸,并給出使用單片機AT89C51控制E1收發(fā)芯片DS2153Q實現(xiàn)NRZ-HDB3的碼制轉換,包括碼轉換器的電路設計和控制軟件設計。

2006-03-11 13:25:32 2263

2263

摘要:AC4830xC-C是美國AudioCodes公司生產的語音專用芯片,它支持多種碼率的語音編解碼國際標準,同時可提供傳真和數(shù)據(jù)中繼功能。而TCM38C17則是美國TI公司的語音PCM編碼

2006-03-24 13:30:23 1206

1206

xc9572應用

介紹了HDB3編解碼的原理和方法,給出了用CPLD(Complex Programmable Logic Device)實現(xiàn)E1信號HDB3編解碼的方法,同時給出了它的實現(xiàn)原理圖,最后給出

2009-03-28 15:22:17 5615

5615

什么是音頻編解碼器?

編解碼器(編碼器/解碼器)轉換成模擬信號的數(shù)字碼流,另一個相同的編解碼器轉換為數(shù)字流回到成模擬信

2009-05-03 23:48:59 3870

3870 摘要:介紹了HDB3編解碼的原理和方法,給出了用CPLD(Complex Programmable Logic Device)實現(xiàn)E1信號HDB3編解碼的方法,同時給出了它的實現(xiàn)原理圖,最后給出了XI

2009-06-20 13:44:03 1049

1049

【HDB3的全稱 】 High Density Bipolar of order 3code,三階高密度雙極性碼。

【HDB3的編碼規(guī)則】

一、編碼規(guī)則:

1 先將消息代碼變換成AMI碼,若AMI碼

2010-07-28 17:39:59 21567

21567 摘要:為提高8B/10B編解碼的工作速度和簡化邏輯方法,提出一種基于FPGA的8B/10B編解碼系統(tǒng)設計方案。與現(xiàn)有的8B/10B編解碼方案相比,該方案是一種利用FPGA實現(xiàn)8B/lOB編解碼的模塊方

2011-05-26 11:08:20 3364

3364

本文在研究二維條碼的碼制標準的基礎上,設計并實現(xiàn)了 DataMatrix 和QR Code 兩種二維條碼的編解碼系統(tǒng),提出了針對不同二維條碼的圖像識別方法。

2011-09-20 16:01:43 0

0 結合RS碼的基本特性,講述了RS碼的編解碼過程,給出了經(jīng)過實際驗證的RS編解碼在超短波跳頻電臺開發(fā)中的軟件應用實例。

2012-02-13 10:07:26 26

26 2012-10-24 09:33:22 31

31 2015-09-21 18:26:29 79

79 G.7xx語音編解碼模塊及在AD218X上的實現(xiàn),PPT教程。

2016-04-14 17:59:41 0

0 13曼徹斯特碼編解碼的FPGA設計與實現(xiàn)-9。

2016-04-26 15:12:57 11

11 RS編解碼的FPGA實現(xiàn)-說明RS編解碼的FPGA實現(xiàn)-說明。

2016-05-04 15:59:44 21

21 四路編解碼電路原理圖都是值得參考的設計。

2016-05-11 17:33:19 27

27 一種高速卷積編解碼器的FPGA實現(xiàn)

2017-02-07 15:05:00 19

19 用單片機實現(xiàn)無線通信中數(shù)據(jù)的編解碼

2017-08-31 10:40:00 10

10 通信接口——編解碼

2017-09-04 09:39:45 9

9 )在G.703建議中規(guī)定,對于2 MHz、8 MHz、32 MHz速率的數(shù)字接口均采用HDB3(三階高密度雙極性)碼。HDB3碼具有無直流分量,低頻成分少,連零個數(shù)不超過3個等特點,便于時鐘信號的提取和恢復,適合在信道中直接傳輸。這里利用Verilog HDL語言設計用于數(shù)字通信系統(tǒng)中的HDB3編解碼器。

2018-07-16 09:32:00 4463

4463

將基于VHDL的HDB3編碼用在光纖通信系統(tǒng)中作為誤碼儀測試誤碼的HDB3轉換器,能滿足實際測試的需要。且運用基于VHDL的可編程芯片開發(fā)技術將相關的信號處理電路進行硬件描述,并用CPLD/FPGA

2018-02-08 04:38:00 12530

12530

本文闡述了基于FFMpeg的 H.264視頻 硬件編解碼在 S3C6410 處理器上的實現(xiàn)方法,為數(shù)字娛樂、視頻監(jiān)控和視頻通信系統(tǒng)開發(fā)過程中的高清視頻硬件編解碼的實現(xiàn)提供參考。

2018-04-03 11:28:00 18638

18638

L9320是LANWAVE公司推出的一款自適應音頻脈沖編碼(ADPCM)編解碼器。該器 件除具有正常的ADPCM編碼解碼模式外,還有PCM編解碼模式、電源測試模式以及編解碼器測試模式。文中主要

2019-12-20 17:27:09 24

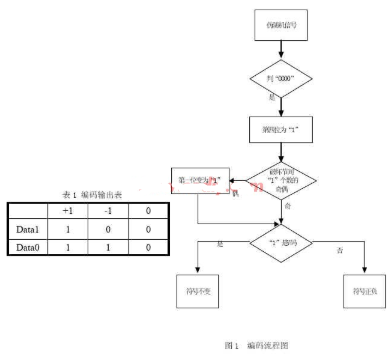

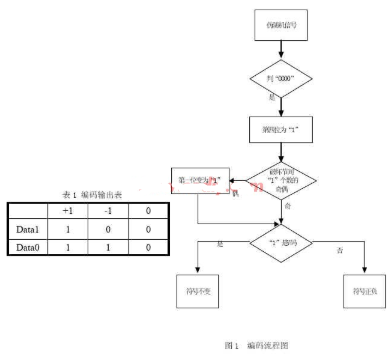

24 由于VHDL不能處理負電平,只能面向“1”、“0”兩種狀態(tài),所以要對它的輸出進行編碼,如表1所示。編碼的實現(xiàn)是根據(jù)HDB3編碼原理把二進制碼編碼成兩路單極性的碼字輸出,之后經(jīng)過單雙變換模塊形成

2020-07-28 18:22:14 2181

2181

簡單介紹了語音編解碼技術的應用背景,根據(jù)目前工程應用需求,提出了設計思路詳細描述了采用DSP芯片實現(xiàn)語音編解碼技術,開發(fā)過程中突破了多DSP共用總線和 FLASH動態(tài)加載關鍵技術,包括HPI總線共用

2021-04-11 11:39:38 17

17 NANDFLASH快速BCH編解碼算法及便件實現(xiàn)(嵌入式開發(fā)自學網(wǎng))-NANDFLASH快速BCH編解碼算法及便件實現(xiàn)? ? ? ??

2021-07-30 14:14:40 5

5 電子發(fā)燒友網(wǎng)站提供《XC9572和XC95108 DIY CPLD實驗板的PCB.zip》資料免費下載

2022-07-22 11:33:05 6

6 此次需求提供的十分明確,給出了編碼規(guī)則及示例,明確了編解碼端口要求;仿真模塊根據(jù)設計進行適配。

2023-05-15 10:41:01 999

999

電子發(fā)燒友網(wǎng)站提供《基于VHDL語言的HDB3碼編解碼器設計.doc》資料免費下載

2023-10-13 09:22:20 0

0 2023-11-01 09:05:33 0

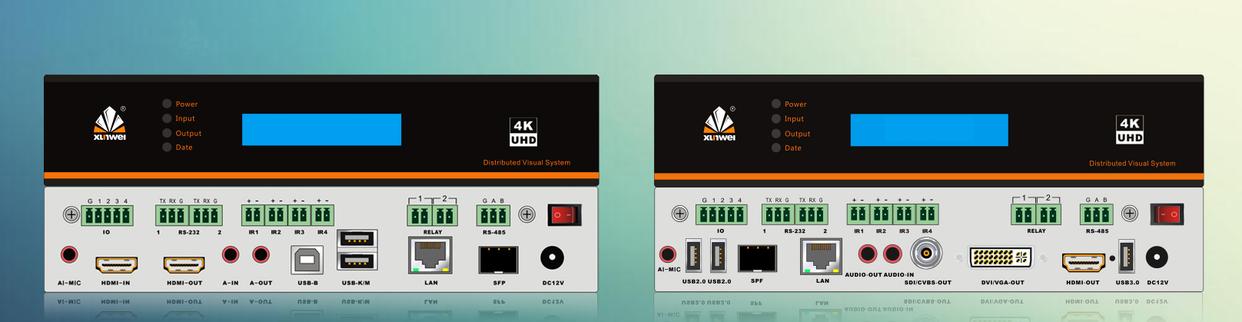

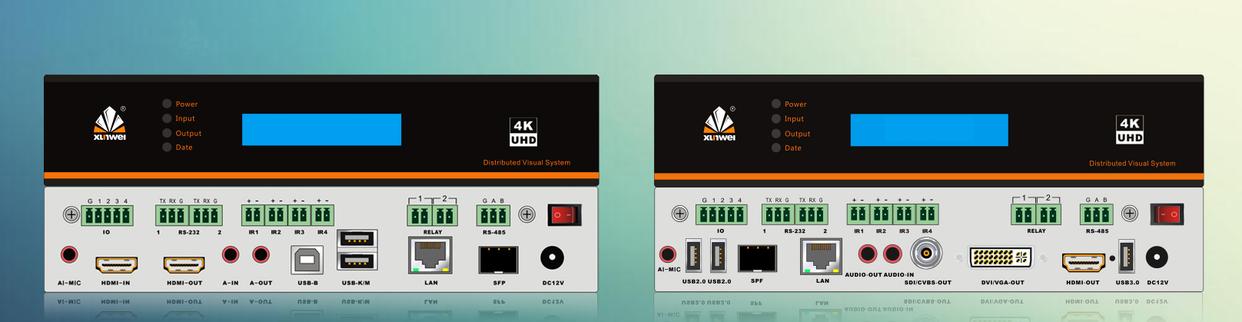

0 一體機還支持多平臺和多終端訪問,允許用戶通過PC、手機、平板等設備隨時隨地訪問和處理視頻內容。 編解碼一體機具有許多優(yōu)勢。首先,它能夠實現(xiàn)高效、實時的視頻處理,滿足各種應用場景的需求。其次,編解碼一體機采用先進的

2024-01-31 14:19:36 168

168

。 編解碼一體機采用了先進的音頻編解碼算法,能夠實現(xiàn)高質量的音頻壓縮和解壓縮。與傳統(tǒng)音頻處理設備相比,編解碼一體機具有更高的處理速度和更低的延遲,能夠滿足實時音頻傳輸?shù)男枨蟆4送猓?b class="flag-6" style="color: red">編解碼一體機還支持多種音頻格式

2024-01-31 14:46:16 134

134

編解碼一體機相對于傳統(tǒng)的編解碼設備具有多個優(yōu)勢。以下是編解碼一體機的幾個主要優(yōu)勢: 高效實時的視頻處理能力:編解碼一體機采用先進的編解碼算法和云計算技術,能夠實現(xiàn)高效、實時的視頻處理,滿足各種應用場

2024-01-31 14:56:04 291

291

電子發(fā)燒友App

電子發(fā)燒友App

評論