非定長碼高速實時拼接專用集成電路的研制

在數(shù)字圖像、視頻、語音等數(shù)據(jù)壓縮應(yīng)用中,經(jīng)常使用熵編碼,例如Huffman編碼、RICE編碼、算術(shù)編碼等。而這些二進制的編碼數(shù)據(jù)在表示中僅有若干位(即碼字長度)有效數(shù)字(碼字),這就要求去除冗余字位,把碼字按其長度依次連接,形成緊湊的定長字,經(jīng)緩存后按恒定碼速率輸出。

1 碼字拼接功能描述

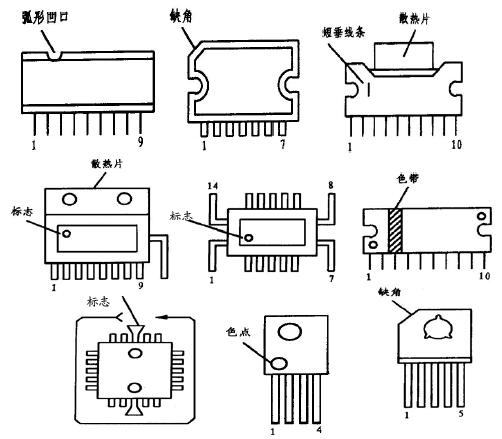

圖1為數(shù)字圖像壓縮流程示意圖。數(shù)據(jù)經(jīng)壓縮與熵編碼后,碼字長度不定,最短的碼字只有1位,最長的碼字需用16位表示,這些碼字包含在位寬為16的輸出數(shù)據(jù)中,如圖2所示。

M[15:0]為熵編碼輸出數(shù)據(jù),M[15:n]中存放碼字,其中n等于15、14、13....2、1、0。由于每個輸出數(shù)據(jù)中僅有碼字長度個有效字位,這就要求去除熵編碼輸出數(shù)據(jù)中的冗余字位M[n-1:0],把這些有效的不定長的碼字M[15:n]拼接湊整,形成定長字。如兩個碼字A和B長度分別為10和6,用熵編碼輸出數(shù)據(jù)M1[15:6]和M2[15:10]表示,這兩個碼字的拼接結(jié)果為Q[15:0],則Q[15:6]存儲M1[15:6],Q[5:0]存儲M2[15:10],即兩個碼字A、B拼接湊整為一個定長字Q[15:0],如圖3所示。

碼字拼接器就是為完成這一功能而設(shè)計的,它去除了原數(shù)據(jù)中的冗余信息,從而減少數(shù)據(jù)量,節(jié)省存儲空間、降低對傳輸信道的帶寬要求。在實際應(yīng)用中,壓縮與熵編碼功能單元(如圖1所示)在每個時鐘周期輸出一個熵編碼數(shù)據(jù),為保證實時性,要求碼字拼接器能于每個時鐘周期內(nèi)完成一次拼接操作,并且每湊足16位,輸出定長字。以上功能的VerilogHDL行為描述如下(該描述不可綜合):

module Connector (clock,code,codelength,dataout);//碼字拼接器模塊

input clock; //時鐘

input [15:0] code; //碼字

input [4:0] codelength; //碼長

output [15:0] dataout; //定長字

reg [4:0] counter;

reg [31:0] tempdata;

initial //初始化

begin

counter = 0;

end

always @(posedge clock) //clock 上升沿

begin

tempdata[31-counter]:(31-counter-15)]

=code[15:0];//緩存碼字

counter=counter+codelength;//累計碼長

if(counter>=16)//如果累計碼長大于等于16

begin

dataout[15:0]=tempdata[31:16];

//輸出一個定長字

tempdata[31:16]=tempdata[15:0];

//低16位移動到高16位

counter=counter-16; //累計碼長減16

end;

end;

endmodeule

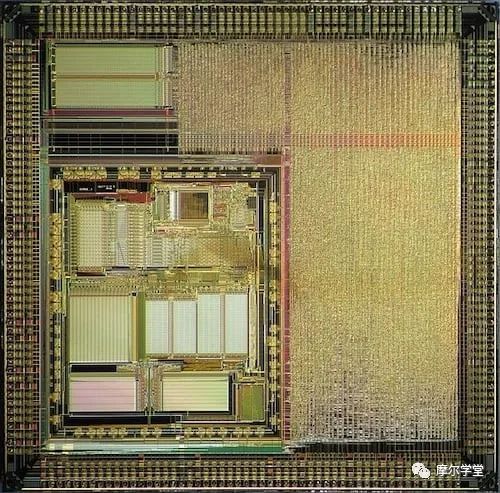

2 VLSI體系結(jié)構(gòu)

上述功能映射到VLSI結(jié)構(gòu),如圖4所示。該碼字拼接器采用并行陣列式結(jié)構(gòu),以流水線方式工作,能夠連接不斷地在每一個時鐘周期內(nèi)完成1到16之間的任意碼長的碼字的拼接湊整,每湊足16位輸出定長字。

??? 圖4中陣列A與陣列B中D觸發(fā)器與十六選一多路選擇器對的結(jié)構(gòu)如圖5所示。??? 多路選擇器模塊由16個二選一的多路選擇器構(gòu)成。當(dāng)累加器中的碼長和大于等于16時,該多路選擇器輸出陣列A或B中的定長字。??? 由此可見,對5位累加器的輸出進行解釋的累加和譯碼器,是整個電路的控制核心。它有5位輸入,160位輸出,其中32位輸出L0~L31,160位輸出,其中32位輸出L0~L31,控制D觸發(fā)器的鎖存;其它128位Sel0[0:3] ~Sel31[0:3]控制32個十六選一多路選擇器。其功能的實現(xiàn)方法如下:當(dāng)累加器為C時,說明陣列A與B的前C位D[31:31-C+1]已是有效碼字,當(dāng)連接下個碼字時,這些位的鎖存信號為無效態(tài),其它位允許鎖存;此時第C+1個十六選一多路選擇器輸出當(dāng)前碼字最高位,存儲在第C+1個D觸發(fā)器中,第C+2個十六選一多路選擇器輸出碼字次高位,存儲在第C+2個D觸發(fā)器中,余下以此類推,全部碼字存儲在在16個D觸發(fā)器內(nèi)。當(dāng)累加器大于等于16時(即最高位由0到1跳變),說明陣列A內(nèi)已經(jīng)拼接湊整了一個16位定長字,此時多路選擇器輸出該值。當(dāng)累加器再次小于16時(即最高位由A到0跳變。注釋:累加器只有5位,當(dāng)C加碼長大于31時,C的實際值將小于16),此時表明陣列B內(nèi)已經(jīng)拼接湊整一個16位定長字,多路選擇器輸出該值。

圖4和圖5中,位寬為5的累加器模塊是五位累加器,對碼長求和,其輸出由累加和譯碼器譯碼,生成D觸發(fā)器與十六選一多路選擇器的鎖存信號Ln和選擇信號Seln[0:3]。當(dāng)累加結(jié)果大于等于16時,多路選擇輸出陣列A或B中的定長字。

陣列A和B各由16對圖5所示的D觸發(fā)器與十六選一多路選擇器對構(gòu)成,D觸發(fā)器暫存碼字某一特定位。累加和譯碼器模塊對累加器的輸出進行譯碼,其輸出接到陣列A和B中32個十六選一多路選擇器的選擇信號端、D觸發(fā)器的鎖存信號端以及多路選擇器的選擇信號端。

?

該VLSI結(jié)構(gòu)工作原理為:時鐘發(fā)生有效跳變,累加器讀入碼長,并與原有數(shù)據(jù)累加。若累加器第五位由“0”跳變?yōu)椤?”,則多路選擇器將在下個周期輸出陣列A的定長字;由“1”跳變?yōu)椤?”,則輸出陣列B的定長字;若沒有跳變;不產(chǎn)生輸出,陣列A、B讀入碼字。累加器中原有數(shù)據(jù)由累加和譯碼器譯碼,產(chǎn)生陣列A、B中相應(yīng)D觸發(fā)器的鎖存信號Ln和十六選一多路選擇器的選擇信號Seln[0:3],這兩個信號把碼字的全部16位存入D觸發(fā)器,為下一個周期作好數(shù)據(jù)準(zhǔn)備。

?

第0個十六選一多路選擇器選擇信號Sel0[3:0]的VHDL描述如下[1]:

case(C)

Sel0 <="1111" when "00000",

"1110" when "00001",

"1101" when "00010",

"1100" when "00011",

"1011" when "00100",

"1010" when "00101",

"1001" when "00110",

"1000" when "00111",

"0111" when "01000",

"0110" when "01001",

"0101" when "01010",

"0100" when "01011",

"0011" when "01100",

"0010" when "01101",

"0001" when "01110",

"0000" when "01111",

"----" when others;

第0個D觸發(fā)器的鎖存信號L0的VHDL描述:

whit C select

L0 <='1' when "00000" |"00001"|"00010"|"00011"

|"00100"|"00101"|"00110"|"00111"|"01000"|"01001"|"01010"

|"01011"|"01100"|"01101"|"01110"|"01111",

'0' when others;

其它1到31的十六進一多路選擇器與D觸發(fā)器對的控制信號的描述與以上類似,在此不一一列出。

3 基于FPGA的物理實現(xiàn)

選用ACTEL公司的eX256TQ100-STD FPGA[2]器件實現(xiàn)上述的VLSI結(jié)構(gòu),研制成非定長碼高速實時拼接專用集成電路[3],設(shè)計結(jié)果如表1。

表1 FPGA實現(xiàn)結(jié)果

?

| 資??? 源 | 總數(shù)(個) | 使用(個) | 占用率(%) |

|

時序單元 組合單元 系統(tǒng)門數(shù) I/O引腳 全局時鐘 硬線時鐘 |

256 512 12,000 81 2 1 |

78 505 9108 42 1 1 |

30.47 98.63 75.91 51.85 50 100 |

?

使用ModelSim仿真器,對非定長碼高速實時拼接專用集成電路進行帶延時的后仿真,仿真驗證結(jié)果如表2。

表2 非定長碼高速實時拼接專用集成電路驗證結(jié)果

?

| 工作環(huán)境 | 電壓2.3V溫度70℃ | 電壓2.5V溫度20℃ | 電壓2.7V溫度0℃ |

| 芯片速度 | 71MHz | 80MHz | 86MHz |

| 功?? 耗 | 110mW | 120mW | 128mW |

?

本文提出的VLSI結(jié)構(gòu),適合圖像壓縮、視頻編碼等應(yīng)用中非定長碼的高速實時拼接,其結(jié)構(gòu)復(fù)雜度低,并行處理能力器。以ACTEL公司eX256 TQ100-STD FPGA實現(xiàn)該VLSI結(jié)構(gòu)的專用集成電路,性能穩(wěn)定可靠、工作頻率高、功耗低、具有良好的工程應(yīng)用前景。

電子發(fā)燒友App

電子發(fā)燒友App

評論