1、 應(yīng)用背景

基于ARM+FPGA的高速同步數(shù)據(jù)采集方案,解決了數(shù)據(jù)采集的同步性問題,與以往

2010-07-22 16:36:17 1326

1326 高通道密度數(shù)據(jù)采集系統(tǒng)用于醫(yī)療成像、工業(yè)過程控制、自動測試設(shè)備和40G/100G光通信系統(tǒng)可將眾多傳感器的信號多路復(fù)用至少量ADC,隨后依序轉(zhuǎn)換每一通道。 ##多路復(fù)用數(shù)據(jù)采集信號鏈##多路復(fù)用數(shù)據(jù)采集系統(tǒng)布局考慮因素

2014-09-16 18:31:24 5378

5378

高速實時頻譜儀是對實時采集的數(shù)據(jù)進行頻譜分析,要達到這樣的目的,對數(shù)據(jù)采集系統(tǒng)的采樣精度、采樣率和存儲量等指標(biāo)提出了更高的要求。而在高速數(shù)據(jù)采集系統(tǒng)中,ADC在很大程度上決定了系統(tǒng)的整體性能,而它們的性能又受到時鐘質(zhì)量的影響。

2019-09-02 06:44:39

該文檔為基于FPGA的多路模擬數(shù)據(jù)采集接口設(shè)計講解文檔,介紹一種基于 8,RQ 的多路模擬數(shù)據(jù)采集接口的設(shè)計方案。該方案使用Max1281 作為模數(shù)轉(zhuǎn)換芯片,在 APA150 FPGA 中設(shè)計和實現(xiàn)了相關(guān)的接口控制、配置和數(shù)據(jù)存儲模塊;給出了系統(tǒng)設(shè)計框圖、FPGA開發(fā)要點和仿真波形。

2018-09-21 14:37:00

多路數(shù)據(jù)采集系統(tǒng):1,8通道的外部信號經(jīng)過放大或衰減后進行采集2,將預(yù)處理后的數(shù)據(jù)通過USB2.0全速接口傳送到上位機3,上位機利用LABVIEW對獲取的數(shù)據(jù)進行儲存和顯示跪求大神幫幫忙!!!我想

2017-04-25 13:55:53

問題是這樣的,1,USB-6341是否支持兩路同步輸出?是不是所有數(shù)據(jù)采集卡的輸出其實都沒有多路開關(guān),所以都可以同步?另外,數(shù)采卡的輸出口缺省是低電平嗎?2,有一個困惑,按照LabVIEW數(shù)據(jù)流思想

2019-10-27 10:20:24

高速數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)MAX7000系列CPLD及其開發(fā)平臺介紹CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

2021-04-08 06:11:56

[qq]3156086065[/qq]高速數(shù)據(jù)采集卡QT1125在飛行質(zhì)譜中的應(yīng)用簡介質(zhì)譜是帶電原子、分子、或分子碎片按質(zhì)荷比(或質(zhì)量)的大小順序排列的圖譜。質(zhì)譜分析法主要是通過對被測樣品離子的質(zhì)荷

2016-03-02 16:06:15

的高速數(shù)據(jù)采集卡,單塊板卡可實現(xiàn)2通道、14bit、1GS/s的快速、高精度脈沖數(shù)據(jù)采集,整個系統(tǒng)可實現(xiàn)多板卡、更多通道的同步數(shù)據(jù)采集工作。經(jīng)過檢測,用戶信號脈寬在20ns左右,利用以上解決方案,實現(xiàn)

2016-03-28 15:11:59

在許多科學(xué)研究和工業(yè)控制中,常常需要對高速變化的信號進行采集與分析,并且在很多領(lǐng)域?qū)?b class="flag-6" style="color: red">數(shù)據(jù)采集系統(tǒng)的精度要求還非常高。因此,設(shè)計一個好的高速高精度采集系統(tǒng)尤為重要。傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)中,A/D的控制

2019-11-07 06:27:39

引言 在日常的測試測量中,經(jīng)常使用數(shù)據(jù)采集卡采集數(shù)據(jù)。但是很多數(shù)據(jù)采集卡往往通過PCI總線完成數(shù)據(jù)的傳輸,它有諸多弊端,例如操作不便,受限于計算機插槽數(shù)量和中斷資源,現(xiàn)場信號對計算機安全有威脅

2014-12-16 11:32:57

申請理由:本開發(fā)板為ARM系類,能移植Linux系統(tǒng),可以實現(xiàn)快速高效的系統(tǒng),并且能實現(xiàn)數(shù)據(jù)云共享。對于高速數(shù)據(jù)采集系統(tǒng),開發(fā)板的資源可以適用,并且非常實用。項目描述:高速數(shù)據(jù)采集系統(tǒng)原理:通過高速

2015-07-17 14:43:58

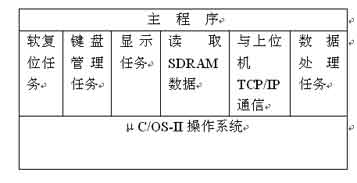

的網(wǎng)絡(luò)數(shù)據(jù)傳輸。3、 系統(tǒng)結(jié)構(gòu)高速同步數(shù)據(jù)采集系統(tǒng)主要包括以下幾個部分:ARM控制器、存儲電路、FPGA邏輯控制電路、A/D轉(zhuǎn)換電路、FIFO緩存、電源電路、接口電路等。系統(tǒng)具備多通道數(shù)據(jù)采集接口

2010-08-31 09:14:55

接口,它使電路工作在更加平穩(wěn)、簡潔而易丁控制,同時也提高了ARM的工作效率。為了提高通信速度,這里采用通用申行總線(USB)技術(shù)米與PC進行通信。ARM是用來控制主處理器的數(shù)據(jù)采集,數(shù)據(jù)的計算和數(shù)據(jù)傳輸。結(jié)果證明,整個系統(tǒng)能高效運作。該系統(tǒng)可應(yīng)用于高速數(shù)據(jù)采集及多路模擬信號的工作環(huán)境下。

2023-09-26 07:41:28

目前,在數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計方案中,有采用通用單片機和USB相結(jié)合的方案,也有采用DSP和USB相結(jié)合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數(shù)據(jù)采集系統(tǒng)對速度要求;后者雖然可以實現(xiàn)

2019-09-05 07:22:57

引言

在日常的測試測量中,經(jīng)常使用數(shù)據(jù)采集卡采集數(shù)據(jù)。但是很多數(shù)據(jù)采集卡往往通過PCI總線完成數(shù)據(jù)的傳輸,它有諸多弊端,例如操作不便,受限于計算機插槽數(shù)量和中斷資源,現(xiàn)場信號對計算機安全有威脅

2018-12-26 07:00:05

基于LabVIEW的單片機多路數(shù)據(jù)采集系統(tǒng)的設(shè)計

2012-09-04 12:47:43

引言 在日常的測試測量中,經(jīng)常使用數(shù)據(jù)采集卡采集數(shù)據(jù)。但是很多數(shù)據(jù)采集卡往往通過PCI總線完成數(shù)據(jù)的傳輸,它有諸多弊端,例如操作不便,受限于計算機插槽數(shù)量和中斷資源,現(xiàn)場信號對計算機安全有威脅

2019-05-07 09:40:04

的核心,它包括A/D轉(zhuǎn)換器、微控制器、USB通信接口等。在高速數(shù)據(jù)采集系統(tǒng)中?由于現(xiàn)場輸入信號是高頻模擬信號,因而信號的變化范圍都比較大?如果采用單一的增益放大?那么放大以后的信號幅值有可能超過A/D

2009-04-11 17:20:15

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

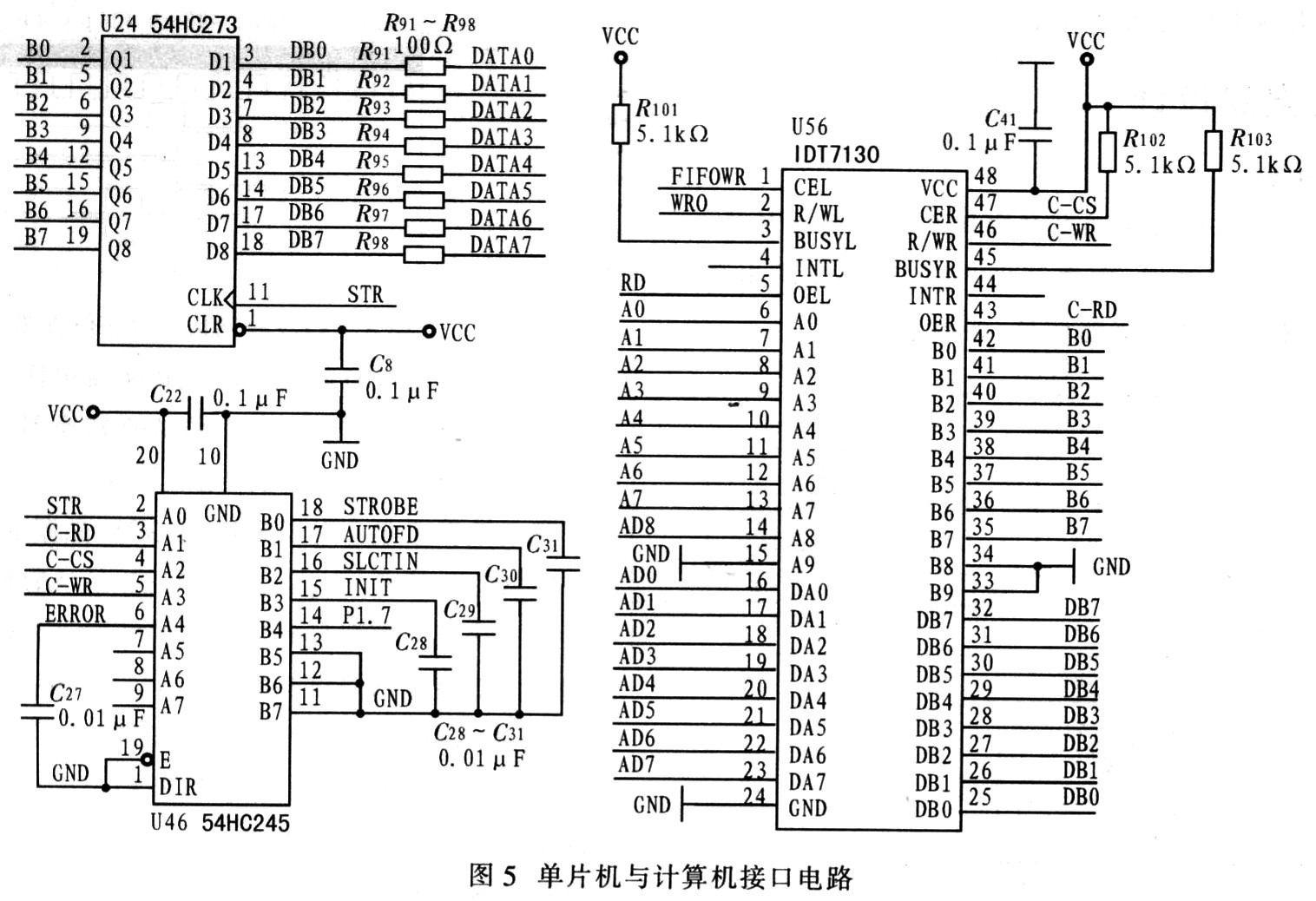

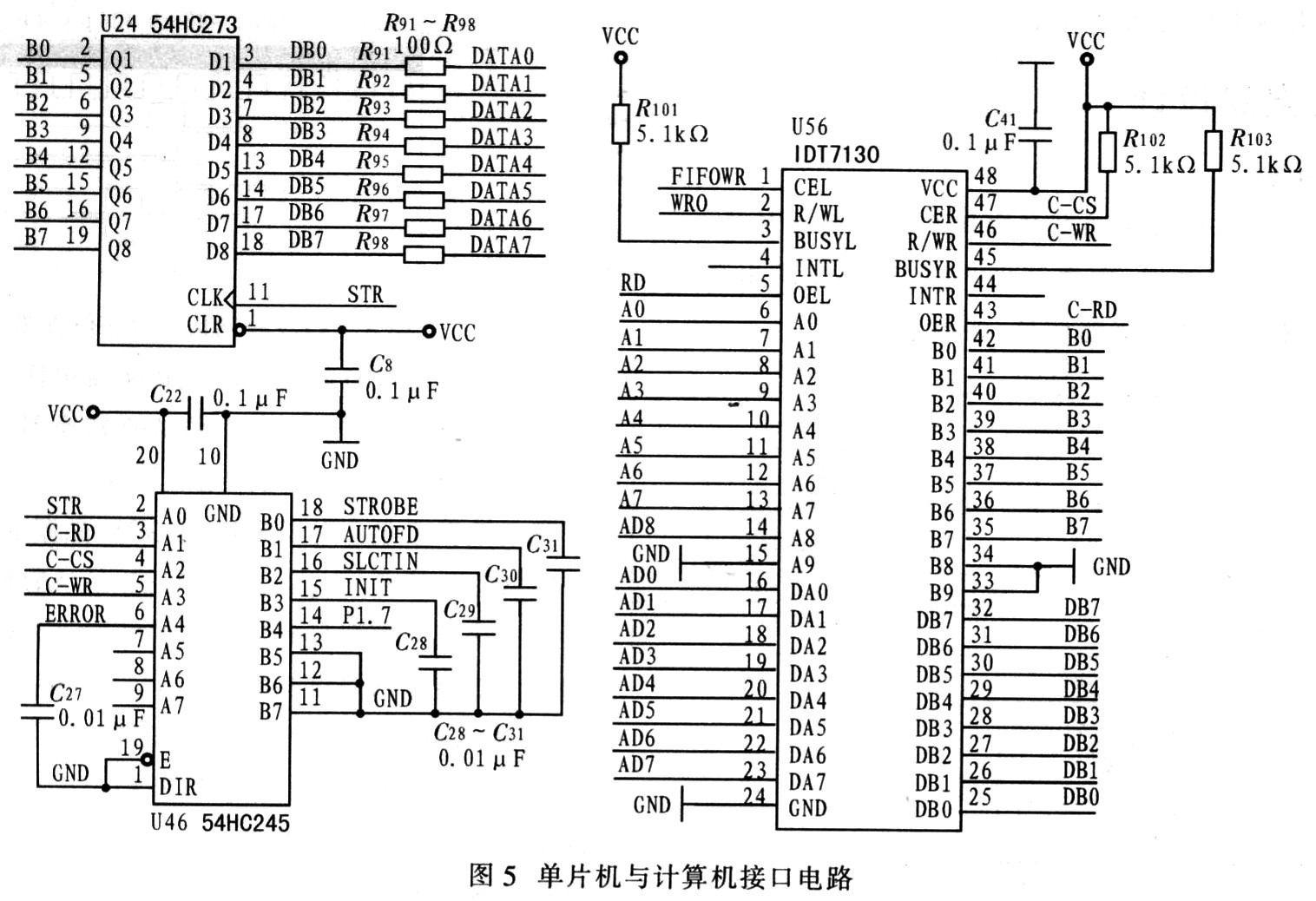

首先介紹了多路數(shù)據(jù)采集系統(tǒng)的總體設(shè)計、FIFO芯片IDT7202。然后分別分析了FIFO與CPLD、AD接口的設(shè)計方法。由16位模數(shù)轉(zhuǎn)換芯片AD976完成模擬量至位數(shù)字量的轉(zhuǎn)換,由ATERA公司

2020-12-31 07:52:43

設(shè)計的基于CPLD與單片機的高速數(shù)據(jù)采集系統(tǒng)在QUARTUS II軟件中進行了仿真并達到了預(yù)期的控制邏輯。

2021-04-13 06:07:06

數(shù)據(jù)采集在現(xiàn)代工業(yè)生產(chǎn)及科學(xué)研究中的重要地位日益突出,對實時高速數(shù)據(jù)采集的要求也不斷提高。在信號測量、圖像處理、音頻信號處理等一些高速、高精度的測量中,都要求進行高速、高精度的數(shù)據(jù)采集。這就對數(shù)據(jù)采集

2019-07-31 07:25:28

- 安裝在高速 ADC(包括高速運算放大器、FIFO 和 SRAM)的周圍。ADC 的數(shù)據(jù)輸出流被寫入 FIFO,存儲在 SRAM 塊中,并在 FPGA 的數(shù)據(jù)采集邏輯的控制下通過寄存器直接發(fā)送至外界

2012-12-12 11:48:15

本系統(tǒng)以AD7892SQ和CPLD(復(fù)雜可編程邏輯器件)為核心設(shè)計了一個多路信號采集電路,包括模擬多路復(fù)用、集成放大、A/D轉(zhuǎn)換,CPLD控制等。采用硬件描述語言Verilog HDL編程,通過采用CPLD使數(shù)據(jù)采集的實時性得到提高。

2021-05-08 07:51:14

本文給出了基于FPGA高速數(shù)據(jù)采集系統(tǒng)中的輸入輸出接口的實現(xiàn),介紹了高速傳輸系統(tǒng)中RocketIO設(shè)計以及LVDS接口、LVPECL接口電路結(jié)構(gòu)及連接方式,并在我們設(shè)計的高速數(shù)傳系統(tǒng)中得到應(yīng)用。

2021-04-29 06:04:42

怎么實現(xiàn)基于USB2.0的高速同步數(shù)據(jù)采集系統(tǒng)的設(shè)計?

2021-05-21 06:47:15

高速數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)MAX7000系列CPLD及其開發(fā)平臺介紹CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

2021-04-30 06:43:12

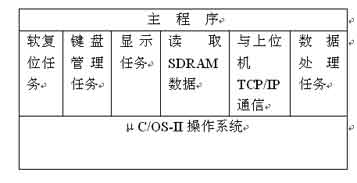

高速數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計高速數(shù)據(jù)采集系統(tǒng)的軟件設(shè)計

2021-06-03 06:04:08

怎么設(shè)計一種高速數(shù)據(jù)采集系統(tǒng)?數(shù)據(jù)采集系統(tǒng)的組成及原理是什么?如何實現(xiàn)高速A/D轉(zhuǎn)換器與DSP的接口設(shè)計?

2021-04-12 06:10:22

基于AVR和CPLD的高速數(shù)據(jù)采集系統(tǒng)該怎樣去設(shè)計?

2021-04-29 06:59:21

高速數(shù)據(jù)采集卡系統(tǒng)的硬件怎樣去設(shè)計?高速數(shù)據(jù)采集卡系統(tǒng)的軟件怎樣去設(shè)計?

2021-04-28 06:16:28

采用PCI總線流水式高速數(shù)據(jù)采集系統(tǒng)設(shè)計摘要:目前基于PCI總線的高速數(shù)據(jù)采集系統(tǒng),大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設(shè)計,其通用性、靈活性差,不能

2009-10-30 15:09:49

采用VHDL 語言設(shè)計,用CPLD 控制模/ 數(shù)轉(zhuǎn)換電路, 完成多路模擬輸入的高速同步數(shù)/ 模轉(zhuǎn)換,具有容錯和自檢能力。CPLD 與處理器之間采用并行接口,具有很好的移植性、可靠性。

2009-04-16 10:44:25 7

7 采用VHDL 語言設(shè)計,用CPLD 控制模/ 數(shù)轉(zhuǎn)換電路, 完成多路模擬輸入的高速同步數(shù)/ 模轉(zhuǎn)換,具有容錯和自檢能力。CPLD 與處理器之間采用并行接口,具有很好的移植性、可靠性。

2009-05-15 13:10:35 18

18 本文對高速數(shù)據(jù)采集系統(tǒng)的設(shè)計進行了討論,介紹利用高速線性放大器、高速A/D 轉(zhuǎn)換芯片、ISP 器件制作的DMA 接口,設(shè)計以單片機為核心的高速數(shù)據(jù)采集系統(tǒng)的方法。關(guān)鍵詞: I

2009-07-15 11:16:00 22

22 設(shè)計了基于工控機和高速模入板卡的數(shù)據(jù)采集系統(tǒng),介紹了Windows 多任務(wù)多線程環(huán)境下,高速同步采集數(shù)據(jù)、存儲與處理數(shù)據(jù)的軟件設(shè)計方法。根據(jù)系統(tǒng)的特點, 采用半滿中斷方式

2009-08-13 10:35:03 15

15 設(shè)計了以CPLD 為核心處理芯片的多路數(shù)據(jù)采集系統(tǒng),按照正確的時序直接控制AD676和雙端口RAM的工作, 所有這些功能都采用VHDL語言進行描述。關(guān)鍵詞:CPLD, AD676, VHDL語言, 雙端口R

2009-09-01 10:26:41 25

25 本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達高度表高速大容量數(shù)據(jù)采集存儲系統(tǒng),分析了系統(tǒng)組成和設(shè)計思想,著重對CPLD 實現(xiàn)的功能做了介紹并給出了代表信號

2009-09-18 11:09:30 11

11 本文介紹了一種基于FPGA 的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計方案,描述了系統(tǒng)的主要組成及FPGA 的實現(xiàn)方法。在硬件上FPGA 采用ACEX1K100 器件,用于實現(xiàn)A/D 轉(zhuǎn)換器的控制電路、多路

2009-12-19 16:02:33 50

50 本文針對新型匝間耐壓測試儀中需要高速采集數(shù)據(jù)的問題提出了一種結(jié)合CPLD 與單片機的高速數(shù)據(jù)采集系統(tǒng)設(shè)計方案。CPLD 產(chǎn)生A/D 芯片的控制時序以及SRAM 的讀寫控制時序,單片機輸

2009-12-23 14:59:57 88

88 基于CPLD 的雷達高度表高速大容量數(shù)據(jù)采集存儲系統(tǒng)設(shè)計作者:李貴新 袁嗣杰 轉(zhuǎn)貼自:微計算機信息摘 要:本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達高

2010-01-27 14:18:26 22

22 本文對激光掃描車身坐標(biāo)測量系統(tǒng)的數(shù)據(jù)采集部分進行了深入研究,設(shè)計了基于“AVR+FIFO+CPLD”的數(shù)據(jù)采集及處理模塊;解決了當(dāng)多路信號有數(shù)據(jù)同時傳輸時,如何將數(shù)據(jù)完整地寫入F

2010-11-22 14:51:10 24

24 設(shè)計一種基于FPGA的多通道同步數(shù)據(jù)采集存儲系統(tǒng),分為多通道同步數(shù)據(jù)采集模塊和數(shù)據(jù)存儲模塊。系統(tǒng)設(shè)計采用多通道數(shù)據(jù)的同步實時采集以及壞塊檢測技術(shù)。多通道同步數(shù)據(jù)采集

2010-12-27 15:31:33 70

70 摘要:介紹了一種基于USB2.0接口的同步高速數(shù)據(jù)采集的設(shè)計方案及其軟硬件的設(shè)計方法,對Cypress的USB2.0控制芯片CY7C68013和同步數(shù)據(jù)采集芯片AD7862的特性作了簡要

2006-03-24 12:58:37 633

633

換體DMA高速數(shù)據(jù)采集電路的CPLD實現(xiàn)

介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實現(xiàn)。用CPLD設(shè)計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 666

666

分布式數(shù)據(jù)采集系統(tǒng)中的時鐘同步

在高速數(shù)據(jù)傳輸?shù)姆植际?b class="flag-6" style="color: red">數(shù)據(jù)采集系統(tǒng)中,各個組成單元間的時鐘同步是保證系統(tǒng)正常工作的關(guān)鍵。由于系統(tǒng)工作于局

2009-03-29 15:10:53 1982

1982

數(shù)據(jù)采集系統(tǒng)是通過采樣電路將輸入的模擬信號轉(zhuǎn)換成離散信號,并送入CPU、MCU或DSP進行處理。現(xiàn)在流行的基于PCI總線設(shè)計的采集卡是數(shù)據(jù)采集系統(tǒng)的主流,其優(yōu)點是可以利用PCI

2009-04-19 10:52:31 817

817

多路跟蹤濾波同步數(shù)據(jù)采集系統(tǒng)的研究

介紹了采用高速硬件鎖相環(huán)技術(shù),對多路相關(guān)聯(lián)信號同時、同步整周期均勻采樣和抗混疊跟蹤濾波的實現(xiàn)方

2009-05-04 19:37:28 1071

1071

設(shè)計了以CPLD為核心處理芯片的多路數(shù)據(jù)采集系統(tǒng),整個數(shù)據(jù)采集系統(tǒng)可實現(xiàn)最大采集頻率為800kHz,通道數(shù)為48路的模擬信號的采集。系統(tǒng)中采用了TI公司最新推出的高速低功耗A/D

2009-05-05 20:04:02 1666

1666

介紹了一種基于CPLD(復(fù)雜可編程邏輯器件)和FIFO(先入先出存儲器)的多通道高速A/D數(shù)據(jù)采集系統(tǒng)的設(shè)計方法,并給出了這種數(shù)據(jù)采集方法的硬件原理電路和主要的軟件設(shè)計思路

2009-05-05 20:50:09 1651

1651

摘要: 采用VHDL語言和圖形輸入設(shè)計方法,給出了用CPLD在遠程多路數(shù)據(jù)采集系統(tǒng)中實現(xiàn)地址譯碼、串口擴展、模塊測試、模數(shù)轉(zhuǎn)換以及高位數(shù)據(jù)處理等功能的具體方

2009-06-20 14:52:11 525

525

摘要:介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實現(xiàn)。用CPLD設(shè)計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積大、電路復(fù)雜、不能實現(xiàn)在線

2009-06-20 15:12:07 878

878

高速數(shù)據(jù)采集系統(tǒng)中精確時標(biāo)的CPLD實現(xiàn)方法

本文介紹一種利用復(fù)雜可編程邏輯器件給高速數(shù)據(jù)采集系統(tǒng)中的采集數(shù)據(jù)貼上精確時間標(biāo)簽的方法,并

2009-07-20 12:42:23 609

609 高速USB數(shù)據(jù)采集系統(tǒng)的設(shè)計

在圖像處理、瞬態(tài)信號測量等一些高速、高精度的應(yīng)用中,需要進行高速數(shù)據(jù)采集。USB 2.0接口以其高速率等優(yōu)點漸有取

2009-09-26 18:05:46 677

677

基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計與實現(xiàn)

介紹一種基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng),并詳細闡述了系統(tǒng)的結(jié)構(gòu)和軟硬件的實

2009-10-15 23:46:59 616

616

基于單片機和CPLD實時數(shù)據(jù)采集顯示系統(tǒng)設(shè)計

1 引言 數(shù)據(jù)采集是分析模擬信號量數(shù)據(jù)的有效方法。而實時顯示數(shù)據(jù)是自動化檢測系統(tǒng)的現(xiàn)實需求。在測

2009-12-22 17:31:02 1739

1739

基于CPLD/FPGA高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

0 引 言 傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)一般采用單片機,系統(tǒng)大多通過PCI總線完成數(shù)據(jù)的傳輸。其缺點是數(shù)學(xué)運算能力差;

2010-01-27 09:35:01 508

508

基于LABVIEW的USB接口多路高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

引言

在日常的測試測量中,經(jīng)常使用數(shù)據(jù)采集卡采集數(shù)據(jù)。但是很多數(shù)據(jù)采集卡往往通過PCI總線完成數(shù)據(jù)

2010-03-01 09:08:29 2415

2415 針對目前低電壓等級的繼電保護以及測控裝置對數(shù)據(jù)采集的高精度、低成本的要求,提出一種多路同步數(shù)據(jù)采集系統(tǒng)的設(shè)計方案。該方案采用MPC8313為主控制器,CS5451A為模數(shù)轉(zhuǎn)換器,通過對CS5451A Master模式串口輸出時序以及FIFO讀寫時序的研究,在CPU和CS5451A

2011-03-07 15:22:35 66

66 本系統(tǒng)以AD7892SQ和CPLD(復(fù)雜可編程邏輯器件)為核心設(shè)計了一個多路信號采集電路,包括模擬多路復(fù)用、集成放大、A/D轉(zhuǎn)換,CPLD控制等。采用硬件描述語言Verilog HDL編程,通過采用CPLD使數(shù)

2011-08-23 10:08:38 1447

1447

CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用! 介紹了高速數(shù)據(jù)采集系統(tǒng)的整體框架分析了其中的通用部分CPLD系列產(chǎn)品的特點及其開發(fā)軟件.CPLD根據(jù)高速數(shù)據(jù)采集系統(tǒng)的需要VHDL語言的形式,介紹了由

2011-12-17 00:12:00 26

26 針對航天測試系統(tǒng)中提出的多通道數(shù)據(jù)采集要求,采用PXI采集卡,設(shè)計了多路溫度、液位、電壓等信號的采集系統(tǒng)。使用VC++2008編寫了采集控制程序,可以實時顯示和處理多路測試數(shù)據(jù)

2012-03-20 10:51:28 51

51 本文結(jié)合實際應(yīng)用需要,設(shè)計了基于復(fù)雜可編程邏輯器件(CPLD)的線陣CCD數(shù)據(jù)采集系統(tǒng)。著重介紹了數(shù)據(jù)采集的特點及該系統(tǒng)軟、硬件設(shè)計和最后的性能評價。

2012-05-14 09:53:41 1133

1133

本文設(shè)計了一種基于CPLD(復(fù)雜可編程邏輯器件)+FX2(單片機CY7C68013)的便攜式高速數(shù)據(jù)采集系統(tǒng),采用了數(shù)據(jù)流驅(qū)動多模塊并行技術(shù)和USB2.0接口。實踐證明,該方案結(jié)構(gòu)簡單,成本低廉

2012-05-25 09:53:19 1472

1472

一種基于ISA總線的高速同步數(shù)據(jù)采集擴展卡,討論了經(jīng)合理的邏輯控制以協(xié)調(diào)高速A/D轉(zhuǎn)換與快速存儲操作的總線接口技術(shù),以及用極少的PC機I/O口地址資源實現(xiàn)數(shù)據(jù)的快速交換的方法

2012-06-06 09:53:31 1368

1368 恒頤基于ARM+FPGA的高速同步數(shù)據(jù)采集方案,解決了數(shù)據(jù)采集的同步性問題,與以往的數(shù)據(jù)采集方案相比,具有高精度、高速率、多參數(shù)同步測量、實時處理、網(wǎng)絡(luò)傳輸不受區(qū)域限制等特點

2012-11-27 10:51:24 1198

1198 基于CPLD的多路音頻采集系統(tǒng),有需要的下來看看。

2016-01-21 11:07:07 28

28 高速大容量數(shù)據(jù)采集系統(tǒng)設(shè)計與實現(xiàn),下來看看

2016-05-10 11:24:33 14

14 高速數(shù)據(jù)采集系統(tǒng)中的FPGA的設(shè)計,下來看看

2016-05-10 11:24:33 15

15 于FPGA的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計。

2016-05-10 13:45:28 41

41 基于FPGA的高速數(shù)據(jù)采集硬件系統(tǒng)設(shè)計.

2016-05-10 17:06:40 43

43 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)接口設(shè)計.

2016-05-10 17:06:40 27

27 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計,下來看看

2016-05-10 17:06:40 19

19 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)設(shè)計,用ad芯片和sdram構(gòu)成高速數(shù)據(jù)采集系統(tǒng)。

2016-05-17 09:49:51 35

35 六通道高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

2017-01-17 19:54:24 11

11 基于PXI架構(gòu)的高速數(shù)據(jù)采集系統(tǒng)設(shè)計_黃宇

2017-02-07 15:17:36 6

6 單片機高速數(shù)據(jù)采集系統(tǒng)的設(shè)計_張俊梅

2017-03-19 11:28:16 2

2 基于ARM_Linux的高速同步數(shù)據(jù)采集系統(tǒng)設(shè)計_李齊禮

2017-03-19 11:31:31 1

1 基于CPLD高速數(shù)據(jù)采集系統(tǒng)設(shè)計_鮮果

2017-03-19 11:45:23 3

3 基于ARMCortex_M3的多路數(shù)據(jù)采集系統(tǒng)的設(shè)計

2017-09-28 09:27:25 6

6 STM32F103x的USB多路數(shù)據(jù)采集系統(tǒng)設(shè)計

2017-09-28 15:15:18 8

8 SPI總線的多路數(shù)據(jù)采集系統(tǒng)的設(shè)計

2017-10-16 09:27:26 22

22 DSP多路同步數(shù)據(jù)采集板設(shè)計

2017-10-20 10:50:01 12

12 介紹了一種基于FPGA的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計方案,描述了系統(tǒng)的主要組成及FPGA的實現(xiàn)方法,并用v∞L語言設(shè)計的狀態(tài)杌在Qmr嚙Ⅱ開發(fā)軟件中進行仿真。該系統(tǒng)在通用數(shù)據(jù)采集系統(tǒng)的基礎(chǔ)上,增加數(shù)據(jù)

2018-10-12 16:15:09 13

13 結(jié)合數(shù)據(jù)采集系統(tǒng)在航天遙感中的應(yīng)用“介紹了一種基于FPGA 的多路數(shù)據(jù)采集系統(tǒng)”給出了硬件原理框圖“并對系統(tǒng)進行了分解”而后討論了影響系統(tǒng)性能的因素實際應(yīng)用證明“采用該方法設(shè)計的系統(tǒng)能有效地完成多路同步高速數(shù)據(jù)采集任務(wù)

2018-10-16 16:18:45 18

18 2018年8月,西安慕雷電子發(fā)布了全球頂級高速數(shù)據(jù)采集記錄存儲系統(tǒng),采樣率高達4GSPS,分辨率12bit,模擬帶寬2GHZ,記錄存儲帶寬高達6GB/S!西安慕雷電子供應(yīng)全球頂級高速數(shù)據(jù)采集卡及超寬

2018-11-13 21:21:34 486

486 為了提高數(shù)據(jù)采集卡的速度,同時降低成本,設(shè)計一種并行數(shù)據(jù)采集系統(tǒng),要求并行采集速度大于10 Mb/s。整個系統(tǒng)由AVR與CPLD控制實現(xiàn),通過MAXl308完成模數(shù)轉(zhuǎn)換,并設(shè)計搭建了其外圍電路。采用

2020-07-20 17:17:02 11

11 本文詳細介紹了一種基于 PCI 總線的高速數(shù)據(jù)采集系統(tǒng)的原理、組成和功能以及在 Windows 2000 環(huán)境下進行數(shù)據(jù)采集和存儲的方法。該系統(tǒng)用于某型號衛(wèi)星下行的高速數(shù)據(jù)采集。系統(tǒng)設(shè)計與技術(shù)的通用性可應(yīng)用于其它類似的高速數(shù)據(jù)采集與處理系統(tǒng)中。

2021-04-14 14:29:30 13

13

電子發(fā)燒友App

電子發(fā)燒友App

評論