在繼電保護測試裝置中, 既有復雜的算法, 又涉及多種檢測與控制方案。用DSP實現算法和多方案的配置,用CPLD進行實時檢測和控制,是一種較好的獨立運行模式。一般CPLD的配置依靠專

2011-10-17 15:22:26 961

961

ACEX 1K系列器件是Altera公司推出的新型CPLD產品。該器件基于SRAM,結合查找表(LUT)和嵌入式陣列塊(EAB)提供了高密度結構,可提供10 000到100 000可用門,每個嵌入式

2020-07-22 17:36:05 2391

2391

100歐姆 1K,10K三檔量程怎么自動換擋的電路圖

2011-08-31 12:27:35

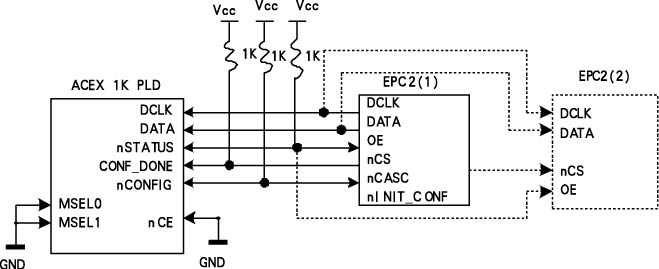

ACEX 1K系列器件實現加載的方法有哪幾種?EPC2器件連接及工作原理是什么?

2021-04-15 06:38:25

ACEX1K - Programmable Logic Device Family - Altera Corporation

2022-11-04 17:22:44

、MAX7000 系列、Mercury、FELX10KE、APEX20KE、APEX20KC、ACEX1K、APEX II和 Stratix 等。 其開發工具 MAX+PLUS II 是較成功

2019-03-04 14:10:13

用vhdl實現cpld配置fpga,配置成功后在usermode下設置一個重新配置信號,當信號有效時對fpga進行重新配置;fpga配置程序放在flash內;現在遇到的問題是,上電cpld能夠正常配置fpga并且進入usermode ,但是加上重新配置語句過后就不能成功配置fpga,求高人指點~

2013-01-17 22:35:39

ADS930 IN和互補輸入端為什么并聯1K電阻

2018-08-19 18:31:29

我看到手冊上有寫到支持1K*16bit二次燒錄的功能,我現在的代碼不到1K,想知道怎么配置二次燒錄。

2021-12-11 19:28:25

或ACEX1K系列等。盡管FPGA和CPLD都是可編程ASIC器件,有很多共同特點,但由于CPLD和FPGA結構上的差異,具有各自的特點:

2019-07-01 07:36:55

的,FPGA分段式布線結構決定了不可預測時間延遲。 3、集成度的不同 CPLD:500 ~ 50000門; FPGA:1K ~ 10M 門 4、應用范圍的不同 CPLD邏輯能力強而寄存器少

2020-07-16 10:46:21

我有一個非常簡單的問題,已經讓我困惑了很久,

誰能回復我?

MIFARE Class EV1 1K 也叫S50 嗎?

MIFARE Class EV1 4K 也叫 S70 嗎?

如果不是

2023-06-05 11:55:18

提供方式 CD-ROM 免費從Altera網站的下載中心下載,或從Quartus II 軟件Starter Suite CD-ROM中獲取 許可 永久 150天 器件支持 全部 ACEX? 1K

2012-08-15 12:30:03

我現在想用TLV2541進行AD采樣,我們要求采樣頻率為1K,我現在不知道怎么樣才能使采樣為準確的1K。用單片機的SPI接口怎樣才能實現?謝謝

2019-05-21 12:01:06

一、基本說明:我的芯片UC2625用于控制無刷直流電機,它的OV-COAST腳由一塊型號為EP1K100的ACEX 1K系列可編程邏輯器件控制。二、問題說明:上電后UC2625的高位、低位都無輸出,且其OV-COAST腳一直為高電平(4伏左右)。想請教一下我的OV-COAST腳的輸入信號是否正確?

2015-09-17 11:20:04

變了。如果flash里燒寫的boot代碼都00,,emif總線讀了大約1K字節數據才不變了。請問 dsp上電時,通過EDMA搬移flash內的1K數據到內部RAM,這個過程有可能被打斷嗎?dsp是在搬移完1K代碼后才開始運行代碼,還是邊搬移邊運行?

2020-05-26 09:17:49

本文將為小伙伴們介紹紫光盤古系列1K2K(MES1/2KG)開發板,盤古1K2K開發板是一款高性能入門級FPGA開發板!盤古1K2K開發板以紫光Compact系列PGC1

2023-04-18 16:00:01

同創PGC1KG-LPG100 / PGC2KG-LPG100開發套件|盤古1K/2K開發套件

4篇大差不差,主要介紹了硬件參數等細節,但不提及使用方法。

[文章] # 【揭秘】紫光盤古系列:盤古

2023-11-21 16:51:07

一款1K方波發生器電路相關資料推薦

2021-05-25 07:28:28

在做就是外部中斷adc檢測在這個條件下,用keil跑裸機,每秒中斷速度可以到達1w次一秒而在rtt中最多一秒鐘只能1k次上下,是外部io中斷,io中斷都是按照原始hal庫寫法求回答

2022-08-12 10:58:11

這塊pcb硬件的emc實驗1k不到,在不改變原理圖的情況下,大家能不能給點建設性的布線意見?

2010-10-14 10:22:35

ACEX 1K具有什么特點DDS電路工作原理是什么如何利用FPGA設計DDS電路?

2021-04-30 06:49:37

介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進行直接數字頻率合成的VHDL源程序。

2021-04-30 06:29:00

本文介紹一個用微控制器在系統配置Lattice MACH4000系列CPLD器件的方案。

2021-04-30 06:43:20

本文介紹了通過處理機用CPLD和Flash實現FPGA配置文件下載更新的方法。

2021-04-28 06:11:19

大家下午好,我計劃使用主fpga板的IO引腳配置目標cpld板,即菊花鏈。我使用主fpga板的IO引腳連接cpld的JTAG頭。如何編程master fpga的IO引腳來配置目標cpld?請發送與此相關的任何文件....謝謝問候Vimala

2020-03-24 06:43:09

對1K的方波信號濾除50Hz工頻干擾和高頻信號可能嗎

2023-10-08 14:38:14

本人想知道,對于運放的輸出端接一個1K電阻,對輸出是否有影響。如圖所示,OP07輸出端接R1,那么A點和B點的電壓會是一樣的嗎?還是B點的電壓實際只有A點的1/2呢?另外,如果是一樣的話,麻煩告知理由,并提示R1阻值的選取方法,本人不勝感激。

2015-08-05 13:23:55

嗨,我是Xilinx的新手,我正在為一個學術項目的編程設備工作。我正在尋找一種使用USB和JTAG配置Spartan3e系列的簡便方法。是否有可能使用像PC(iMpact) - > USB-

2019-06-21 12:38:15

2江西省計算機一級考試試題 (10頁) 本資源提供全文預覽,點擊全文預覽即可全文預覽,如果喜歡文檔就下載吧,查找使用更方便哦!9.9 積分江西省計算機一級考試試題一、選擇題1. 微機中1K字節表示

2021-09-15 09:29:42

CPLD是altera的7256,20塊電路板有兩塊始終無法下載程序,下載器應該是好的,量了CPLD的外圍,供電3.28V正常。板下載插針和CPLD之間是四路JTAG信號,TCK,TDO,TMS,TDI。四引腳對地都不短路,四路串的是1K的電阻。

2017-07-13 11:48:55

盤古1K/2K 開發套件是基于紫光同創 FPGA 開發平臺的開發套件,以紫光同創 Compa系列PGC1KG-LPG100 / PGC2KG-LPG100 器件為核心,預留豐富的擴展 IO

2023-09-22 15:03:53

盤古1K/2K 開發套件是基于紫光同創 FPGA 開發平臺的開發套件,以紫光同創 Compa系列PGC1KG-LPG100 / PGC2KG-LPG100 器件為核心,預留豐富的擴展 IO 及數碼管

2023-08-02 14:20:11

盤古1K/2K 開發套件是基于紫光同創 FPGA 開發平臺的開發套件,以紫光同創 Compa系列PGC1KG-LPG100 / PGC2KG-LPG100 器件為核心,預留豐富的擴展 IO 及數碼管

2023-08-22 16:26:46

最近才進入此論壇 玩耍,后來發現這里的資料真心的很有幫助,激動的花了好多幣去下載 pdf文檔,后來發現下載的時候都是現實有好幾M大小,但結果是下載后的大小只有1K,準確的說是720B ,求各位幫忙指點下 。。。

2014-08-06 15:03:01

Altera FLEX/ACEX芯片結構是如何構成的?Intel XScale PXA270處理器的系統存儲器接口怎樣去設計?Linux下的ACEX1K50設備驅動是如何實現的?

2021-04-30 06:44:14

各位大神,請問1k的三角波信號經過截止頻率為10k的低通濾波器,出來的波形有影響嗎?方波呢?

2017-04-25 15:57:58

關于ACEX1K的I/O腳驅動能力. ALTERA 計算功耗的datasheet 中:對ACEX1K器件, PDCOUT (power of steady-state outputs)的計算就是根據IOH, IOL來計算的, 能否告訴我ACEX1K芯片的IOH, IOL分別是多少?

2019-08-07 00:00:34

不懂cpld,看了看別人說的,像cpld可以擴展io,做74系列時序什么的,做高速ad控制,電機控制可是現在有幾個問題1.代替74系列的成本會不會是個問題?2.比如做高速ad的話,用ic加單片機

2019-02-22 00:55:38

使用ADA4895-1ARJZ時,負載約1k歐,反向放大,系統電源±6V,正負電均串聯51歐(150歐)后給運放供電。經常發現器件損壞,而且是運放電源被拉至±1.2~±2V左右,而正常工作時運放電源約±5.4V。請問容易壞的原因是什么,改進方法除了單獨用±5V還有嗎?

2018-07-30 09:34:31

目前使用AD9834,希望得到一個幅值在0.1V,頻率1K或者10K的正弦波,芯片DAC 只有10bits的分辨率,波形看上去臺階很明顯,希望推薦調整方案,或者更高輸出分辨率芯片

2019-02-15 06:22:38

ELF系列是CPLD還是FPGA?

2023-08-11 06:05:42

我使用STK-SIM900A開發板,通過GPRS方式由開發板至PC客戶端發送1K字節數據,發送AT+CIPSEND--1k字節數據--結束符(0x1a),通過測量,當發送完結束符0x1a到pc客戶端

2019-05-10 05:16:55

手冊上看到STM32F030 的FLASH 擦寫次數只有1K,真的只有1K么?051系列的手冊上是10K,

2018-11-20 08:35:54

abm庫里面的softlim,它的上下限設置如果不是常數,而是隨電壓變化的量,應該怎么設置呢?比如我的電壓從0到1v變化,而上下限都是關于電壓的函數,上下限應該怎么設置呢?還有就是softlim上面顯示的1k是什么意思呢?

2018-06-05 16:43:32

單片機stca15系列和cpld的epm240系列怎么通信連接啊?

2023-10-27 08:25:22

如何通過添加一個簡單的RC電路至FPGA或CPLD 的LVDS輸入來實現模數轉換器?請問怎么實現低頻率(DC至1K Hz)和高頻率(高達50K Hz)ADC?

2021-04-15 06:29:55

XC9500系列CPLD器件是什么?XC9500系列CPLD器件遙控編程的實現方法有哪些?如何實現CPLD遙控編程?

2021-04-27 07:15:42

在論壇下載到SRIO的官方例程,移植到開發板后,使DSP與FPGA通訊,DSP向FPGA發送1K數據成功,更改傳輸數據的大小為1024*1024后編譯成功,但是還是傳輸的1K數據,查看地址以及配置

2018-07-23 10:49:17

AD的專家們,旋變產生的Sin,SinLo 和Cos,CosLo怎么濾波,勵磁信號為1K,解碼芯片為AD2S83,濾波電路怎么搭!給個濾波電路吧!

2018-10-30 09:22:55

本人新手做鎖相環的,最近在做一個小步進的本振,因為體積原因,不能用DDS來做,只能用一個單環輸出,輸出要求是:參考信號10M,輸出300-305M的信號,功率無所謂,步進1K,主要是相噪問題,要求

2018-11-23 09:33:08

后面1k地址,有亂碼。這是什么原因呢,不調用GAPRole_PeripheralInit( ) ,打印出來就不會有亂碼。GAPRole_PeripheralInit( ) 這個函數是庫的,無法跟蹤。麻煩看看,謝謝

2022-08-11 07:55:45

自己DIY了一個功放想 用手機做信號源輸入,把手機用公對公音頻信號線,插到功放上手機卻不識別網上講得把輸入左右聲道并聯1k到4.7k的電阻這樣可以嗎? 對功放會不會有影響?

2018-06-23 23:59:58

電路無疑是一種很好的解決方法。ACEX 1K器件是Altera公司著眼于通信、音頻處理及類似場合的應用而推出的芯片系列,ACEX1K器件正逐步取代FLEX l0K系列成為首選的中規模器件產品。它具有

2019-06-18 06:05:34

負反饋系列文章開始于經典的方框圖,其中放大器和反饋網絡都被認為是單向的。采用自下而上的方法,我們來探討反饋網絡通常是雙向的。現在是時候來討論最常見的情形了,其實放大器也是雙向的。為此,我們來看圖1

2019-01-26 15:53:23

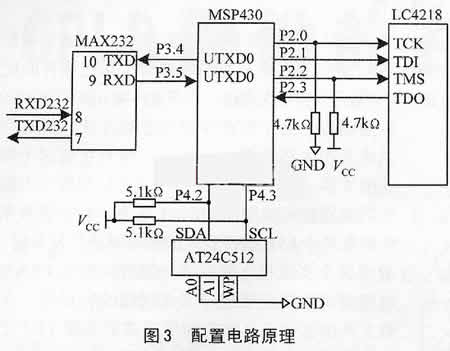

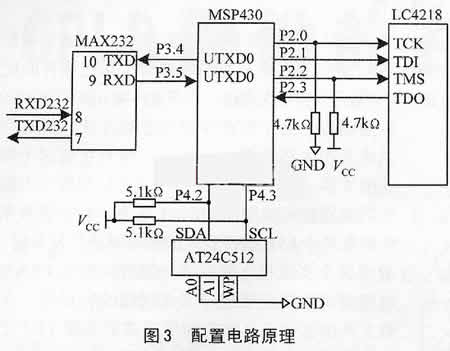

結合繼電保護測試裝置的研制體會,介紹基于DSP 的CPLD 多方案現場可編程配置方法,給出硬件的配置連接、CPLD 配置數據的獲取與存儲方法和CPLD 在DSP 控制下的被動串行配置過程。設

2009-04-15 08:50:55 29

29 結合繼電保護測試裝置的研制體會,介紹基于DSP 的CPLD 多方案現場可編程配置方法,給出硬件的配置連接、CPLD 配置數據的獲取與存儲方法和CPLD 在DSP 控制下的被動串行配置過程。設

2009-05-18 14:33:24 16

16 基于單片機的CPLD/FPGA被動串行下載配置的實現:介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行模式的下載配置,闡述了其原理及軟硬件設計。 &nb

2009-10-29 21:57:22 19

19 特征基于SRAM的LUT設備的配置設備提供以下特性:■配置Altera ACEX? 1K、APEX? 20K(包括APEX 20K、APEX 20KC和APEX 20KE)、APEX II

2023-03-07 18:54:42

HT48E MCU系列1K位EEPROM

本文以HT48E06 為例子,但程序可適用于HOLTEK HT48E06、HT48E10、HT48E30 等,含有1K 位EEPROM Data Memory 的MCU。

2010-03-27 09:05:01 26

26 當利用CPLD/FPGA開發系統完成數字電路或系統的開發設計并仿真校驗通過之后,就需要將獲得的CPLD/FPGA編程配置數據下載到CPLD/FPGA芯片中,以便最后獲得所設計的硬件數字電路或系

2010-06-01 10:14:46 23

23 MDT10P55B1S,MICROCHIP/微芯,1K個字和狀態RA的72個字節 MCUMDT10P55B1S,MICROCHIP/微芯,1K個字和狀態RA的72個字

2023-10-17 16:35:09

摘要:本文討論了Cyclone系列器件的不同配置方法,提出一種單片機結合FLASH存儲器的被動串行配置方案。關鍵詞:FPGA;FLASH;PS;Cyclone

2010-08-13 12:04:09 64

64 探討電梯控制技術的發展歷史和技術現狀,仔細研究CPLD器件的工作原理,開發流程以及VHDL語言的編程方法;采用單片CPLD器件,在MAX+plusⅡ軟件環境下,運用VHDL語言設計一個16樓層單

2010-12-27 15:27:35 56

56 用單片機配置CPLD器件

ALTERA公司的可編程序邏輯器件APEX20K、FLEX10K和FLEX6000雖應用廣泛,但由于其內部采用SRAM存儲配置數據,每次系統上電時,必須用配置芯片對其進行配置

2009-03-28 16:18:06 1071

1071

以下是引用片段: 摘要: 介紹一種利用微控制器動態配置CPLD器件的方法。將配置文件存放在存儲器中,配置文件中的控制代碼驅動在微處理器中運行的配置引擎;將配置文件中的配置信息通過JTAG口移入

2009-06-20 10:44:21 3034

3034

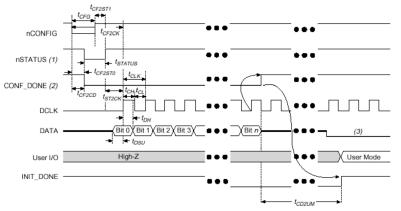

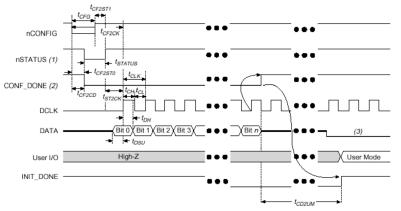

一、 配置方式

ALTERA CPLD器件的配置方式主要分為兩大類:主動配置方式和被動方式。主動配置方式由CPLD器件引導配置操作過程,它控制著外部存儲器和

2009-06-20 10:58:14 1928

1928 摘要: 介紹了DDFS的原理和Altera公司的FPGA器件ACEX 1K的主要特點,給出了用ACEX 1K系列器件EP1K10TC144-1實現數字頻率合成器的工作原理、設計思路、電路結構和仿真結

2009-06-20 14:02:25 844

844

本文介紹了通過處理機用CPLD和Flash實現FPGA配置文件下載更新的方法。與傳統的JTAG或PROM串行下載配置方法相比,此方法具有更新配置文件靈活方便、易于操作、適用于大容量FPGA下載的特點

2018-10-25 05:51:00 8194

8194

下載的PLD稱之為FPGA。把Flash、EEPROM框架或乘積項框架的PLD稱為CPLD。 Altera把自己的PLD產品MAX系列/FLEX/ACEX/APEX系列稱為CPLD。由于FLEX

2017-06-19 09:59:13 3996

3996 本文檔詳細介紹的是FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明主要內容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下載配置,三、FLEX/ACEX系列FPGA的下載配置,四、ALTERA的編程文件

2019-02-28 09:56:18 17

17 Stratix?系列、Cyclone?系列、Apex?II、Apex 20K(包括Apex 20KE和Apex 20KC)、Mercury?、Acex?1K、Flex?10K(包括Flex 10KE

2019-04-19 08:00:00 10

10 FPGA CPLD可編程邏輯器件的在系統配置方法(深圳市村田電源技術有限公司)-FPGA CPLD可編程邏輯器件的在系統配置方法? ? ? ? ? ? ? ? ? ?

2021-09-18 10:51:20 13

13 電子發燒友網站提供《Compact系列CPLD配置(configuration)用戶指南.pdf》資料免費下載

2022-09-26 10:08:17 2

2 電子發燒友網站提供《Compact系列CPLD可配置邏輯模塊(CLM)用戶指南.pdf》資料免費下載

2022-09-26 10:06:25 2

2 CPLD的MAX系列器件庫max-13.0.1.232

2022-12-21 17:26:11 4

4

電子發燒友App

電子發燒友App

評論