本文首先介紹了各種分頻器的實(shí)現(xiàn)原理,并在FPGA開(kāi)發(fā)平臺(tái)上通過(guò)VHDL文本輸入和原理圖輸入相結(jié)合的方式,編程給出了仿真結(jié)果。最后通過(guò)對(duì)各種分頻的分析,利用層次化設(shè)計(jì)思想,綜合設(shè)計(jì)出了一種基于FPGA的通用數(shù)控分頻器,通過(guò)對(duì)可控端口的調(diào)節(jié)就能夠?qū)崿F(xiàn)不同倍數(shù)及占空比的分頻器。

2015-05-07 09:43:16 4685

4685

時(shí)鐘使能電路是同步設(shè)計(jì)的重要基本電路,在很多設(shè)計(jì)中,雖然內(nèi)部不同模塊的處理速度不同,但是由于這些時(shí)鐘是同源的,可以將它們轉(zhuǎn)化為單一的時(shí)鐘電路處理。在FPGA的設(shè)計(jì)中,分頻時(shí)鐘和源時(shí)鐘的skew不容易

2020-11-10 13:53:41 4795

4795

通過(guò)上一篇文章“時(shí)鐘管理技術(shù)”,我們了解Xilinx 7系列FPGA主要有全局時(shí)鐘、區(qū)域時(shí)鐘、時(shí)鐘管理塊(CMT)。 通過(guò)以上時(shí)鐘資源的結(jié)合,Xilinx 7系列FPGA可實(shí)現(xiàn)高性能和可靠的時(shí)鐘分配

2023-08-31 10:44:31 1032

1032

生成時(shí)鐘包括自動(dòng)生成時(shí)鐘(又稱為自動(dòng)衍生時(shí)鐘)和用戶生成時(shí)鐘。自動(dòng)生成時(shí)鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時(shí)鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 400

400

說(shuō)說(shuō)專用時(shí)鐘引腳,它的出現(xiàn)具體原因可以說(shuō)是FPGA自身的實(shí)現(xiàn)結(jié)構(gòu)引起的,FPGA實(shí)現(xiàn)時(shí),具體的時(shí)鐘大概有外部供給FPGA的工作時(shí)鐘,由DCM或者PLL產(chǎn)生的時(shí)鐘,和FPGA輸入輸出數(shù)據(jù)的隨路時(shí)鐘;再說(shuō)

2019-07-09 08:00:00

初學(xué)FPGA,聽(tīng)說(shuō)分頻貌似挺重要,是必備的基礎(chǔ)技能。小白的我今天就從奇偶分頻開(kāi)始我的FPGA學(xué)習(xí)成長(zhǎng)之路偶數(shù)分頻很簡(jiǎn)單的哈,打字蠻累的,直接上代碼/*************6分頻

2016-03-30 11:35:51

`基于FPGA+的任意小數(shù)分頻器的設(shè)計(jì)基于FPGA的多種分頻設(shè)計(jì)與實(shí)現(xiàn)基于FPGA的小數(shù)分頻器的實(shí)用Verilog 實(shí)現(xiàn)基于FPGA 的通用分頻用Verilog+HDL實(shí)現(xiàn)基于FPGA的通用分頻

2012-02-03 15:02:31

學(xué)習(xí)高手的FPGA編程程序,發(fā)現(xiàn)他寫(xiě)的程序怎么這么冗余呢?懷著疑問(wèn),直到第二次閱讀另一高手的FPGA程序,才開(kāi)始懷疑是自己錯(cuò)了,原來(lái)使用時(shí)鐘使能而不直接使用分頻時(shí)鐘是原因的。查閱相關(guān)資料整理了一下

2018-08-08 11:13:26

誰(shuí)幫忙設(shè)計(jì)一下模數(shù)轉(zhuǎn)換芯片ADC0809以及串行通信部分均需要有相應(yīng)的時(shí)鐘驅(qū)動(dòng)。而此次選擇的Altera CycloneⅡ系列FPGA中的EP2C5T144C8的系統(tǒng)時(shí)鐘為20MHz,因此根據(jù)需要

2014-05-09 11:53:23

FPGA時(shí)鐘問(wèn)題 2010-06-11 15:55:39分類: 嵌入式1.FPGA的全局時(shí)鐘是什么?FPGA的全局時(shí)鐘應(yīng)該是從晶振分出來(lái)的,最原始的頻率。其他需要的各種頻率都是在這個(gè)基礎(chǔ)上利用PLL或者其他分頻手段得到的。

2021-07-29 09:25:57

的

時(shí)鐘都是差分

時(shí)鐘,這個(gè)時(shí)候如果所用的不是差分

時(shí)鐘就需要注意 P端與 N端一般不能同時(shí)

分配給不同的

時(shí)鐘信號(hào)。如下圖所示XILINX系列的

FPGA中成對(duì)的

時(shí)鐘如果是同時(shí)采用那么就不能同時(shí)到達(dá)相同的區(qū)域,因?yàn)?/div>

2017-03-25 18:46:25

`fpga應(yīng)用篇(三):你可能用了假分頻 分頻對(duì)于fpga的重要性不言而喻,對(duì)于大多數(shù)通信方式來(lái)說(shuō),一個(gè)穩(wěn)定且準(zhǔn)確的分頻程序?qū)τ谕ㄐ诺姆€(wěn)定很重要。為什么你的UART總是不穩(wěn)定,很有可能你用了一個(gè)假

2017-04-07 21:03:07

時(shí)鐘分頻電路精講

2013-07-11 09:37:52

如何配置模塊的時(shí)鐘分頻?

2024-02-05 06:01:59

在查閱CPLD設(shè)計(jì)的相關(guān)資料的時(shí)候,看到有文章說(shuō)過(guò)當(dāng)時(shí)鐘晶振超過(guò)20M的時(shí)候,最好采用流水線操作現(xiàn)在我用的EPM240T100C5才用的是50M的晶振那么我可不可以將時(shí)鐘先分頻,然后將分頻后的時(shí)鐘

2013-04-25 09:39:35

在FPGA的設(shè)計(jì)中一直都擔(dān)任著很重要的角色,而說(shuō)到分頻,我相信很多人都已經(jīng)想到了利用計(jì)數(shù)器計(jì)數(shù)來(lái)得到想要的時(shí)鐘頻率,但問(wèn)題是僅僅利用計(jì)數(shù)器來(lái)分頻,只可以實(shí)現(xiàn)偶數(shù)分頻,而如果需要三分頻、五分頻、七分頻

2019-12-11 10:15:33

(DCM)適用于實(shí)現(xiàn)延遲鎖相環(huán)(DLL)、數(shù)字頻率綜合器、數(shù)字移相器或數(shù)字頻譜擴(kuò)展器。 DCM還是鏡像、發(fā)送或再緩沖時(shí)鐘信號(hào)的理想選擇。另一種時(shí)鐘資源相位匹配時(shí)鐘分頻器(PMCD)可用于實(shí)現(xiàn)相位匹配分配

2020-04-25 07:00:00

各位FPGA的高手們,小弟再做一個(gè)FPGA二分頻信號(hào)時(shí),有一個(gè)很困惑的問(wèn)題,一直搞不明白,具體要求如下硬件連接,編程要求圖中電源電壓VCC=3.3V,R1 = 1×(1±10%)KΩ,R2 = 1

2015-03-13 13:35:12

在芯片的研發(fā)環(huán)節(jié),FPGA 驗(yàn)證是其中的重要的組成部分,如何有效的利用 FPGA 的資源,管腳分配也是必須考慮的一個(gè)重要問(wèn)題。一般較好的方法是在綜合過(guò)程中通過(guò)時(shí)序的一些約束讓對(duì)應(yīng)的工具自動(dòng)分配,但是

2015-01-06 17:38:22

本帖最后由 weihu_lu 于 2014-6-19 16:25 編輯

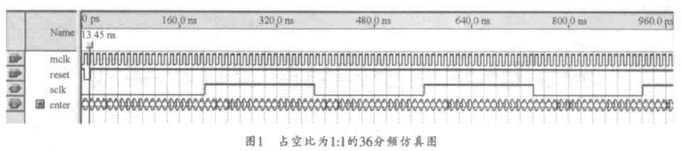

作者:盧威虎1、前言 分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本單元之一。盡管目前在大部分設(shè)計(jì)中還廣泛使用集成鎖相環(huán)(如

2014-06-19 16:15:28

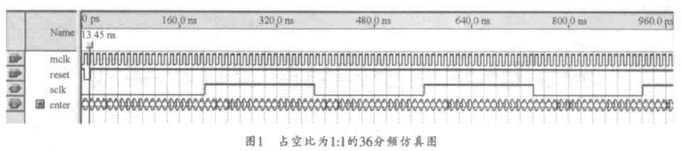

【摘要】:介紹了基于FPGA的任意分頻系數(shù)的分頻器的設(shè)計(jì),該分頻器能實(shí)現(xiàn)分頻系數(shù)和占空比均可以調(diào)節(jié)的3類分頻:整數(shù)分頻、小數(shù)分頻和分?jǐn)?shù)分頻。所有分頻均通過(guò)VHDL語(yǔ)言進(jìn)行了編譯并且給出了仿真圖。本

2010-04-26 16:09:01

中從電子設(shè)計(jì)的外圍器件逐漸演變?yōu)閿?shù)字系統(tǒng)的核心。伴隨著半導(dǎo)體工藝技術(shù)的進(jìn)步,FPGA器件的設(shè)計(jì)技術(shù)取得了飛躍發(fā)展及突破。分頻器通常用來(lái)對(duì)某個(gè)給定的時(shí)鐘頻率進(jìn)行分頻,以得到所需的時(shí)鐘頻率。在設(shè)計(jì)數(shù)

2019-10-08 10:08:10

你好,我是西安大略大學(xué)的研究生。我目前正在使用Virtex5 XUPV5 -LX110T FPGA開(kāi)發(fā)板。我使用DCM在VHDL中編寫(xiě)了一個(gè)簡(jiǎn)單的時(shí)鐘分頻器,我使用IMPACT對(duì)代碼進(jìn)行了編程。我

2020-06-12 14:23:23

同步數(shù)字系統(tǒng)中的時(shí)鐘信號(hào)(如遠(yuǎn)程通信中使用的)為系統(tǒng)中的數(shù)據(jù)傳送定義了時(shí)間基準(zhǔn)。一個(gè)時(shí)鐘分配網(wǎng)絡(luò)由多個(gè)時(shí)鐘信號(hào)組成,由一個(gè)點(diǎn)將所有信號(hào)分配給需要時(shí)鐘信號(hào)的所有組件。因?yàn)?b class="flag-6" style="color: red">時(shí)鐘信號(hào)執(zhí)行關(guān)鍵的系統(tǒng)功能,很顯然應(yīng)給予更多的關(guān)注,不僅在時(shí)鐘的特性(即偏移和抖動(dòng))方面,還有那些組成時(shí)鐘分配網(wǎng)絡(luò)的組件。

2019-10-16 07:11:33

截取的RTC內(nèi)部框圖,從圖中我們可以看到,RTCCLK經(jīng)過(guò)20位分頻器RTC_DIV分頻后得到日歷的1Hz時(shí)鐘,所以我們只需要配置RTC_DIV就行了,分頻公式為RTC_CLK/(RTC_DIV+1

2021-08-29 21:36:46

定時(shí)器時(shí)鐘分頻因子和預(yù)分頻系數(shù)區(qū)別1、定時(shí)器時(shí)鐘分頻因子ClockDivision是決定數(shù)字濾波器采樣頻率的參數(shù)。之后在使用輸入捕獲濾波器時(shí)這些參數(shù)會(huì)被用到,可以根據(jù)硬件情況配置濾波。2、預(yù)分頻系數(shù)

2021-08-09 07:37:47

RTC時(shí)鐘要求提供1HZ的時(shí)鐘,HSE配置為RTC時(shí)鐘源, 主要配置系統(tǒng)時(shí)鐘, 使能HSE。然后設(shè)置好HSE分頻、RTC_PRER分頻寄存器的值。計(jì)算如下:??STM32F7xx的可編程預(yù)分配

2022-05-13 15:19:08

是否有評(píng)估板的外部(FPGA外部)時(shí)鐘分頻器而不是使用DCM或PLL?問(wèn)候,半

2020-03-16 09:11:44

用FPGA控制AD采集,AD的時(shí)鐘信號(hào)由FPGA的IO口產(chǎn)生。在接入AD時(shí)鐘端前,FPGA輸出時(shí)鐘信號(hào)(分頻產(chǎn)生)的IO口電壓值正常跳變,但是一接入AD的時(shí)鐘端,電壓就一直被拉低了,之后我在

2013-02-01 20:00:19

請(qǐng)給位共同討論DSP2812中死區(qū)控制單元的時(shí)鐘分頻是指對(duì)CPU時(shí)鐘還是高速外設(shè)時(shí)鐘分頻?看到論壇里說(shuō)的很亂,大家討論一個(gè)正確的結(jié)果。

2018-08-19 06:31:35

AD9266數(shù)據(jù)手冊(cè)中未明確提及adc的SPI接口控制及其內(nèi)部寄存器部分使用的時(shí)鐘是什么來(lái)源,是spi接口上的sclk還是參考輸入時(shí)鐘經(jīng)過(guò)分頻后產(chǎn)生的?發(fā)現(xiàn)如果用FPGA先通過(guò)spi接口對(duì)adc進(jìn)行

2019-01-21 16:06:39

我們一般使用FPGA都需要有外部時(shí)鐘信號(hào)輸入,在經(jīng)過(guò)分頻倍頻等操作實(shí)現(xiàn)特定的功能,我想問(wèn)問(wèn),能不能用FPGA自己產(chǎn)生時(shí)鐘信號(hào),不需要外部輸入時(shí)鐘信號(hào)???求解答!

2019-05-24 04:05:29

一種FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案:摘 要:本文闡述了用于FPGA 的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探

2009-08-08 09:07:22 25

25 在復(fù)雜數(shù)字邏輯電路設(shè)計(jì)中,經(jīng)常會(huì)用到多個(gè)不同的時(shí)鐘信號(hào)。介紹一種通用的分頻器,可實(shí)現(xiàn)2~256 之間的任意奇數(shù)、偶數(shù)、半整數(shù)分頻。首先簡(jiǎn)要介紹了FPGA 器件的特點(diǎn)和應(yīng)用范

2009-11-01 14:39:19 78

78 DLL在FPGA時(shí)鐘設(shè)計(jì)中的應(yīng)用:在ISE集成開(kāi)發(fā)環(huán)境中,用硬件描述語(yǔ)言對(duì)FPGA 的內(nèi)部資源DLL等直接例化,實(shí)現(xiàn)其消除時(shí)鐘的相位偏差、倍頻和分頻的功能。時(shí)鐘電路是FPGA開(kāi)發(fā)板設(shè)計(jì)中的

2009-11-01 15:10:30 33

33 基于FPGA 的等占空比任意整數(shù)分頻器的設(shè)計(jì)

給出了一種基于FPGA 的等占空比任意整數(shù)分頻電路的設(shè)計(jì)方法。首先簡(jiǎn)要介紹了FPGA 器件的特點(diǎn)和應(yīng)用范圍, 接著討論了一

2010-02-22 14:22:32 39

39 本文闡述了用于FPGA的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探討了FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案。

2010-08-06 16:08:45 12

12

供數(shù)字時(shí)鐘使用的+5000分頻器電路

2009-01-13 20:07:47 1089

1089

摘 要: 本文通過(guò)在QuartursⅡ開(kāi)發(fā)平臺(tái)下,一種能夠?qū)崿F(xiàn)等占空比、非等占空比整數(shù)分頻及半整數(shù)分頻的通用分頻器的FPGA設(shè)計(jì)與實(shí)現(xiàn),介紹了利用VHDL硬件描

2009-06-20 12:43:07 562

562

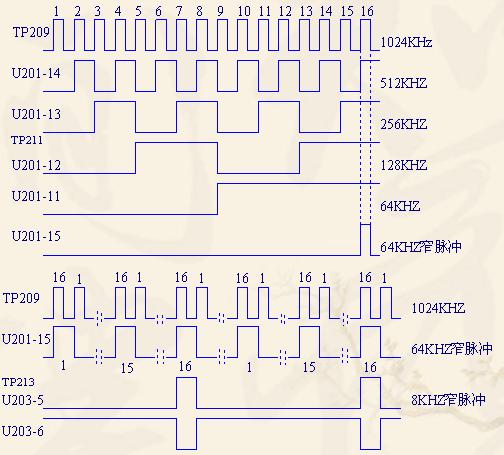

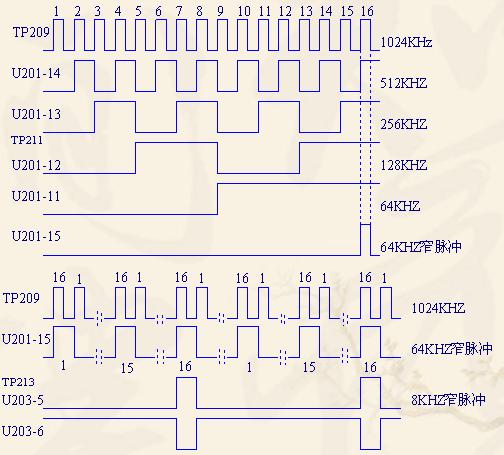

時(shí)鐘分頻及定時(shí)變換電路

2009-10-11 10:35:51 2033

2033

基于CPLD/FPGA的多功能分頻器的設(shè)計(jì)與實(shí)現(xiàn)

引言

分頻器在CPLD/FPGA設(shè)計(jì)中使用頻率比較高,盡管目前大部分設(shè)計(jì)中采用芯片廠家集成的鎖相環(huán)資源 ,但是對(duì)于要求

2009-11-23 10:39:48 1139

1139

本文將探討FPGA時(shí)鐘分配控制方面的挑戰(zhàn),協(xié)助開(kāi)發(fā)團(tuán)隊(duì)改變他們的設(shè)計(jì)方法,并針對(duì)正在考慮如何通過(guò)縮小其時(shí)鐘分配網(wǎng)絡(luò)的規(guī)模來(lái)?yè)碛懈嗟?b class="flag-6" style="color: red">FPGA I/O,或提高時(shí)鐘網(wǎng)絡(luò)性能的設(shè)計(jì)者們

2011-03-30 17:16:32 938

938

在FPGA設(shè)計(jì)中,為了成功地操作,可靠的時(shí)鐘是非常關(guān)鍵的。設(shè)計(jì)不良的時(shí)鐘在極限的溫度、電壓下將導(dǎo)致錯(cuò)誤的行為。在設(shè)計(jì)PLD/FPGA時(shí)通常采用如下四種類型時(shí)鐘:全局時(shí)鐘、門(mén)控時(shí)鐘

2011-09-21 18:38:58 3472

3472

本文給出了分頻技術(shù)通用模型。并結(jié)合最新的一些分頻技術(shù),提出了一種基于FPGA全新的分頻系統(tǒng)的設(shè)計(jì)方法,簡(jiǎn)單的介紹了設(shè)計(jì)的思路、原理及其算法,并對(duì)該方案的性能進(jìn)行了分析,

2011-11-08 18:03:32 137

137 提出了一種基于FPGA的小數(shù)分頻實(shí)現(xiàn)方法,介紹了現(xiàn)有分頻方法的局限性,提出一種新的基于兩級(jí)計(jì)數(shù)器的分頻實(shí)現(xiàn)方法,給出了該設(shè)計(jì)方法的設(shè)計(jì)原理以及實(shí)現(xiàn)框圖

2011-11-09 09:36:22 121

121 給出了一種基于FPGA的分頻電路的設(shè)計(jì)方法.根據(jù)FPGA器件的特點(diǎn)和應(yīng)用范圍,提出了基于Verilog的分頻方法.該方法時(shí)于在FPGA硬件平臺(tái)上設(shè)計(jì)常用的任意偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻

2011-11-09 09:49:33 355

355 介紹了一種基于FPGA的雙模前置小數(shù)分頻器的分頻原理及電路設(shè)計(jì),并用VHDL編程實(shí)現(xiàn)分頻器的仿真.

2011-11-29 16:43:06 48

48 現(xiàn)今的FPGA設(shè)計(jì)大多采用時(shí)序邏輯,需要時(shí)鐘網(wǎng)絡(luò)才能工作,通常情況下,時(shí)鐘通過(guò)外部晶體振蕩器產(chǎn)生。雖然大多數(shù)情況下使用外部晶振是最好的選擇。然而,石英晶振對(duì)溫度漂移敏感

2012-11-19 17:07:02 10474

10474

時(shí)鐘是SOC或塊級(jí)設(shè)計(jì)最重要的組成部分之一,本文闡述了目前SOC中各種可配置時(shí)鐘分頻器邏輯的實(shí)施方案,強(qiáng)調(diào)了各自的問(wèn)題、優(yōu)勢(shì)及局限性。

2013-01-09 10:12:48 2890

2890

用 Verilog實(shí)現(xiàn)基于FPGA 的通用分頻器的設(shè)計(jì)時(shí)鐘分頻包括奇數(shù)和偶數(shù)分頻

2016-07-14 11:32:47 45

45 設(shè)計(jì)過(guò)FPGA的原理圖,看FPGA的手冊(cè),說(shuō)管腳的分配問(wèn)題,如時(shí)鐘管腳要用GC類管腳,而且單端時(shí)鐘輸入時(shí)要用P類型的管腳,不能用N類型管腳等等。

2017-02-11 03:48:34 10684

10684

分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖相環(huán)資源,如賽靈思(Xilinx)的DLL.來(lái)進(jìn)行時(shí)鐘的分頻,倍頻以及相移。

2017-02-11 12:33:40 10916

10916 分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖相環(huán)資源,如賽靈思(Xilinx)的DLL.來(lái)進(jìn)行時(shí)鐘的分頻,倍頻以及相移。

2017-02-11 13:36:36 12409

12409

單片機(jī)都是有時(shí)鐘振蕩器的。還有定時(shí)器,看門(mén)狗,程序計(jì)數(shù)器等等。如果看門(mén)狗或者定時(shí)器所要求的脈沖速度比較時(shí)鐘脈沖慢,那么,就要利用分頻器進(jìn)行分頻,以得到你所要求的脈沖速率。分頻因子就是在定時(shí)器時(shí)鐘進(jìn)入

2017-11-15 10:07:22 18147

18147

STM32中有一個(gè)全速功能的USB模塊,其串行接口引擎需要一個(gè)頻率為48MHz的時(shí)鐘源。該時(shí)鐘源只能從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當(dāng)需要使用USB模塊時(shí),PLL必須使能,并且時(shí)鐘頻率配置為48MHz或72MHz。

2017-11-30 09:14:18 6833

6833

設(shè)計(jì)背景: 分頻在 fpga的設(shè)計(jì)中一直都擔(dān)任著很重要的角色,而說(shuō)到分頻,我相信很多人都已經(jīng)想到了利用計(jì)算器來(lái)計(jì)算達(dá)到想要的時(shí)鐘頻率,但問(wèn)題是僅僅利用計(jì)數(shù)器來(lái)分頻,只可以實(shí)現(xiàn)偶數(shù)分頻,而如果我需要

2018-06-13 11:21:48 12390

12390

分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本單元之一。盡管目前在大部分設(shè)計(jì)中還廣泛使用集成鎖相環(huán)(如altera的PLL,Xilinx的DLL)來(lái)進(jìn)行時(shí)鐘的分頻、倍頻以及相移設(shè)計(jì),但是,對(duì)于時(shí)鐘要求

2019-08-07 08:00:00 9033

9033

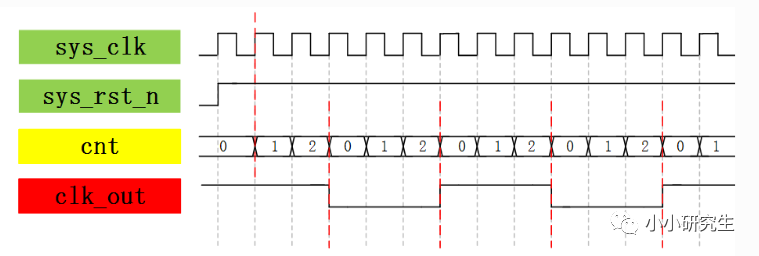

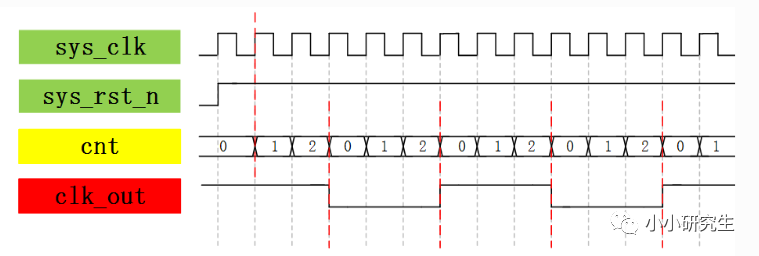

偶數(shù)倍分頻器的實(shí)現(xiàn)非常簡(jiǎn)單,只需要一個(gè)計(jì)數(shù)器進(jìn)行計(jì)數(shù)就能實(shí)現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時(shí)鐘觸發(fā)計(jì)數(shù)器進(jìn)行計(jì)數(shù),當(dāng)計(jì)數(shù)器從0計(jì)數(shù)到N/2-1時(shí),將輸出時(shí)鐘進(jìn)行翻轉(zhuǎn),并給計(jì)數(shù)器一個(gè)復(fù)位信號(hào),以使下一個(gè)時(shí)鐘開(kāi)始從零計(jì)數(shù)。

2019-02-01 01:49:00 1029

1029

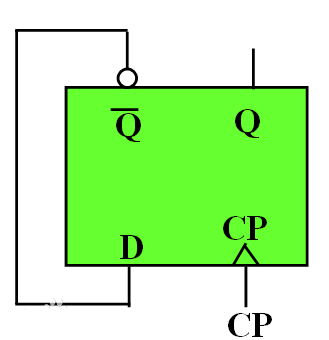

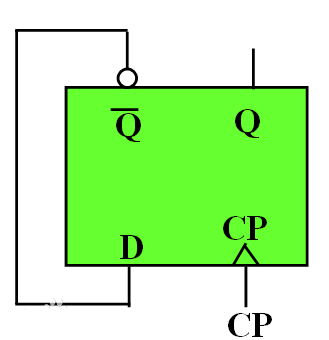

分頻就是用同一個(gè)時(shí)鐘信號(hào)通過(guò)一定的電路結(jié)構(gòu)轉(zhuǎn)變成不同頻率的時(shí)鐘信號(hào)。而二分頻就是通過(guò)有分頻作用的電路結(jié)構(gòu),在時(shí)鐘每觸發(fā)2個(gè)周期時(shí),電路輸出1個(gè)周期信號(hào)。

2019-10-08 09:05:00 22247

22247

分頻點(diǎn)是分頻器分配給每個(gè)揚(yáng)聲器單元所承擔(dān)的頻響范圍的標(biāo)記,是根據(jù)揚(yáng)聲器單元的音頻表現(xiàn)能力(單元振膜有效直徑?jīng)Q定的邊界頻率)而定的;那么,三分頻最佳分頻點(diǎn)是多少?

2019-10-09 09:56:38 50735

50735 通常情況下,時(shí)鐘的分頻在FPGA設(shè)計(jì)中占有重要的地位,在此就簡(jiǎn)單列出分頻電路設(shè)計(jì)的思考思路。

2020-07-10 17:18:03 2192

2192 。 不要隨意將內(nèi)部信號(hào)作為時(shí)鐘,如門(mén)控時(shí)鐘和分頻時(shí)鐘,而要使用CLKDLL或者DCM產(chǎn)生的時(shí)鐘,或者可以通過(guò)建立時(shí)鐘使能或者DCM產(chǎn)生不同的時(shí)鐘信號(hào)。 FPGA盡量采取同步設(shè)計(jì),也就是所有時(shí)鐘都是同一個(gè)源頭,如果使用兩個(gè)沒(méi)有相位關(guān)系的異步時(shí)鐘,必須

2020-12-11 10:26:44 1482

1482 電子發(fā)燒友網(wǎng)站提供《NB7V33MMNGEVB 時(shí)鐘分頻器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2020-12-31 05:06:41 5

5 電子發(fā)燒友網(wǎng)站提供《NB7L32MMNEVB 時(shí)鐘分頻器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2020-12-31 05:21:59 2

2 電子發(fā)燒友網(wǎng)站提供《SY89876L 時(shí)鐘分頻器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2020-12-31 05:22:31 10

10 電子發(fā)燒友網(wǎng)站提供《SY89873L 時(shí)鐘分頻器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2020-12-31 05:23:10 5

5 電子發(fā)燒友網(wǎng)站提供《NB6L239MNEVB/D 時(shí)鐘分頻器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2020-12-31 05:23:51 13

13 電子發(fā)燒友網(wǎng)站提供《SY89872U 時(shí)鐘分頻器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2020-12-31 05:24:21 1

1 電子發(fā)燒友網(wǎng)站提供《SY89871U 時(shí)鐘分頻器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2020-12-31 05:25:53 6

6 電子發(fā)燒友網(wǎng)站提供《SY89875U 時(shí)鐘分頻器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2020-12-31 05:27:06 4

4 時(shí)鐘分配器是將輸入時(shí)鐘脈沖經(jīng)過(guò)一定的分頻后分別送到各路輸出的邏輯電路。

2021-03-02 17:34:58 8497

8497 程序?qū)崿F(xiàn)對(duì)輸入時(shí)鐘信號(hào)的7分頻介紹。

2021-03-17 14:59:23 11

11 尋找合適的基準(zhǔn)時(shí)鐘分配

2021-03-20 17:11:48 7

7 AD9510:1.2 GHz時(shí)鐘分配IC,PLL內(nèi)核,分頻器,延遲調(diào)整,8路輸出

2021-03-21 15:32:58 11

11 也被設(shè)計(jì)成支持非常高頻率的信號(hào)。了解全局時(shí)鐘的信號(hào)路徑可以擴(kuò)展對(duì)各種全局時(shí)鐘資源的理解。全局時(shí)鐘資源和網(wǎng)絡(luò)由以下路徑和組件組成: 時(shí)鐘樹(shù)和網(wǎng)絡(luò):GCLK 時(shí)鐘區(qū)域 全局時(shí)鐘緩沖器 1. 時(shí)鐘樹(shù)和網(wǎng)絡(luò):GCLK 7系列FPGA時(shí)鐘樹(shù)設(shè)計(jì)用于低偏差和低功

2021-03-22 10:09:58 11527

11527

AD9512:1.2 GHz時(shí)鐘分配IC,1.6 GHz輸入,分頻器,延遲調(diào)整,五輸出數(shù)據(jù)表

2021-03-22 19:53:41 13

13 AD9515:1.6 GHz時(shí)鐘分配IC、分頻器、延遲調(diào)整、雙輸出數(shù)據(jù)表

2021-04-13 14:38:52 9

9 超低抖動(dòng)時(shí)鐘的產(chǎn)生與分配

2021-04-18 14:13:51 8

8 一種基于FPGA的分頻器的實(shí)現(xiàn)說(shuō)明。

2021-05-25 16:57:08 16

16 AD9515 1.6 GHz時(shí)鐘分配IC,分頻器,延遲調(diào)整,雙輸出數(shù)據(jù)表

2021-06-16 17:13:16 12

12 本章的主要內(nèi)容: 分析時(shí)鐘驅(qū)動(dòng)器、時(shí)鐘信號(hào)的特殊布線 改進(jìn)時(shí)鐘信號(hào)分配的特殊電路

2022-09-20 14:55:40 0

0 如何優(yōu)化 PCIe 應(yīng)用中的時(shí)鐘分配

2022-11-07 08:07:15 0

0 控制板級(jí)時(shí)鐘分配期間出現(xiàn)的 EMI

2022-11-07 08:07:32 0

0 偶數(shù)倍分頻器的實(shí)現(xiàn)非常簡(jiǎn)單,只需要一個(gè)計(jì)數(shù)器進(jìn)行計(jì)數(shù)就能實(shí)現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時(shí)鐘觸發(fā)計(jì)數(shù)器進(jìn)行計(jì)數(shù),當(dāng)計(jì)數(shù)器從0計(jì)數(shù)到N/2-1時(shí),將輸出時(shí)鐘進(jìn)行翻轉(zhuǎn),并給計(jì)數(shù)器一個(gè)復(fù)位信號(hào),以使下一個(gè)時(shí)鐘開(kāi)始從零計(jì)數(shù)。

2022-11-21 09:41:24 751

751 ,但 FPGA 由于器件本身和工具的限制,分頻時(shí)鐘和源時(shí)鐘的Skew不容易控制(使用鎖相環(huán)分頻是個(gè)例外),難以保證分頻時(shí)鐘和源時(shí)鐘同相,因此推薦的方法是使用時(shí)鐘使能,通過(guò)使用時(shí)鐘使能可以避免時(shí)鐘“滿天飛”的情況,進(jìn)而避免了不必要的亞穩(wěn)態(tài)發(fā)

2023-01-05 14:00:07 949

949 FPGA分頻器是一種常用于數(shù)字信號(hào)處理、通信系統(tǒng)、雷達(dá)系統(tǒng)等領(lǐng)域的電路,其作用是將信號(hào)分成多個(gè)頻段。

2023-05-22 14:29:44 1032

1032

板載晶振提供的時(shí)鐘信號(hào)頻率是固定的,不一定滿足需求,因此需要對(duì)基準(zhǔn)時(shí)鐘進(jìn)行分頻。要得到更慢的時(shí)鐘頻率可以 分頻 ,要得到更快的時(shí)鐘頻率可以 倍頻 。我們有兩種方式可以改變頻率,一種是 鎖相環(huán) (PLL,后面章節(jié)會(huì)講解),另一種是用 Verilog代碼描述。

2023-06-23 16:52:00 1149

1149

基于FPGA的高頻時(shí)鐘的分頻和分頻設(shè)計(jì)

2023-08-16 11:42:47 0

0 為什么單片機(jī)內(nèi)置時(shí)鐘源不經(jīng)過(guò)pll也可以分頻?? 單片機(jī)內(nèi)置時(shí)鐘源不經(jīng)過(guò)PLL也可以實(shí)現(xiàn)分頻,原因在于單片機(jī)內(nèi)置時(shí)鐘源自帶分頻器,可以通過(guò)軟件設(shè)置分頻系數(shù)來(lái)控制內(nèi)部時(shí)鐘頻率。 在單片機(jī)內(nèi)部,通常會(huì)

2023-09-02 15:12:45 597

597 時(shí)鐘分頻電路通過(guò)將輸入的高頻時(shí)鐘信號(hào)分頻,生成較低頻率的時(shí)鐘信號(hào)。它通常基于計(jì)數(shù)器和邏輯門(mén)實(shí)現(xiàn),用于將高頻時(shí)鐘信號(hào)分解成系統(tǒng)所需的各種頻率。

2023-09-14 14:53:57 4894

4894 第11章時(shí)鐘分配

2022-12-30 09:21:58 2

2 分頻器設(shè)計(jì) 一:分頻器概念 板載時(shí)鐘往往 是 有限個(gè)( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在設(shè)計(jì)中需要其他時(shí)鐘時(shí),板載時(shí)鐘不滿足時(shí),需要對(duì)板載時(shí)鐘進(jìn)行分頻 / 倍頻,目的

2023-11-03 15:55:02 471

471

其實(shí)這個(gè)分頻時(shí)鐘切換很簡(jiǎn)單,根本不需要額外的切換電路。一個(gè)共用的計(jì)數(shù)器,加一點(diǎn)控制邏輯,就可以了,而且可以實(shí)現(xiàn)2到16任意整數(shù)分頻率之間的無(wú)縫切換。

2023-12-14 15:28:56 257

257

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論