摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線(xiàn)接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。

關(guān)鍵詞:CPLD ISA總線(xiàn) 并行通信

CPLD(Complex Programmable Logic Device)是一種復(fù)雜的用戶(hù)可編程邏輯器件,由于采用連續(xù)連接結(jié)構(gòu)。這種結(jié)構(gòu)易于預(yù)測(cè)延時(shí),從而電路仿真更加準(zhǔn)確。CPLD是標(biāo)準(zhǔn)的大規(guī)模集成電路產(chǎn)品,可用于各種數(shù)字邏輯系統(tǒng)的設(shè)計(jì)。近年來(lái),由于采用先進(jìn)的集成工藝和大批量生產(chǎn),CPLD器件成本不斷下降,集成密度、速度和性能大幅度提高,一個(gè)芯片就可以實(shí)現(xiàn)一個(gè)復(fù)雜的數(shù)字電路系統(tǒng);再加上使用方便的開(kāi)發(fā)工具,使用CPLD器件可以極大地縮短產(chǎn)品開(kāi)發(fā)周期,給設(shè)計(jì)、修改帶來(lái)很大方便[1]。本文以ALTERA公司的MAX7000系列為例,實(shí)現(xiàn)MCS51單片機(jī)與PC104 ISA總線(xiàn)的并行通信。采用這種通信方式,數(shù)據(jù)傳輸準(zhǔn)確、高速,在12 MHz晶振的MCS51單片機(jī)控制的數(shù)據(jù)采集系統(tǒng)中,可以滿(mǎn)足與PC104 ISA總線(xiàn)接口實(shí)時(shí)通信的要求,通信速率達(dá)200 Kbps。

1 系統(tǒng)總體設(shè)計(jì)方案

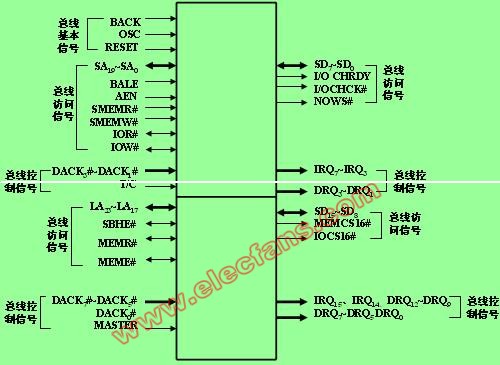

本系統(tǒng)用CLPD實(shí)現(xiàn)單片機(jī)與PC104 ISA總線(xiàn)接口的并行通信。由于PC104主要完成其它方面的數(shù)據(jù)采集工作,只是在空閑時(shí)才能接收單片機(jī)送來(lái)的數(shù)據(jù),所以要求雙方通信的實(shí)時(shí)性很強(qiáng),但數(shù)據(jù)量不是很大。因此,在系統(tǒng)設(shè)計(jì)中單片機(jī)中斷方式接收數(shù)據(jù),PC104采用查詢(xún)方式接收數(shù)據(jù)。系統(tǒng)設(shè)計(jì)方案如圖1所示。

在圖1單片機(jī)部分,D[0..7]是數(shù)據(jù)總線(xiàn),A[0..15]是地址總線(xiàn),RD和WR分別是讀寫(xiě)信號(hào)線(xiàn),INT0是單片機(jī)的外部中斷。當(dāng)單片機(jī)的外部中斷信號(hào)有效時(shí),單片機(jī)接收數(shù)據(jù)。

在CPLD部分,由一片MAX7000系列中的EPM7128LSC84來(lái)實(shí)現(xiàn),用來(lái)完成MCS51與PC104ISA總線(xiàn)接口之間的數(shù)據(jù)傳輸、狀態(tài)查詢(xún)及延時(shí)等待。

在PC104 ISA部分,只用到ISA的8位數(shù)據(jù)總線(xiàn)D[0..7],A[0..9]是PC104的地址總線(xiàn);IOW和IOR是對(duì)指定設(shè)備的讀寫(xiě)信號(hào);AEN是允許DMA控制地址總線(xiàn)、數(shù)據(jù)總線(xiàn)及讀寫(xiě)命令線(xiàn)進(jìn)行DMA傳輸,及對(duì)存儲(chǔ)器和I/O設(shè)備的讀寫(xiě);IOCHRDY是I/O就緒信號(hào),I/O通道就緒為高,此時(shí)處理機(jī)產(chǎn)生的存儲(chǔ)器讀寫(xiě)周期為4個(gè)時(shí)鐘周期,產(chǎn)生的I/O讀寫(xiě)周期和DMA字節(jié)傳輸均需5個(gè)時(shí)鐘周期,MCS51通過(guò)置此信號(hào)為低電平來(lái)使CPU插入等待周期,從而延長(zhǎng)I/O周期;SYSCLK是系統(tǒng)時(shí)鐘信號(hào),是為了與外部設(shè)備保持同步;RESETDR是上電復(fù)位或系統(tǒng)初始化邏輯,是系統(tǒng)總清信號(hào)。

2 基于MAX+plus II的硬件實(shí)現(xiàn)

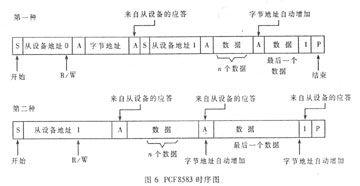

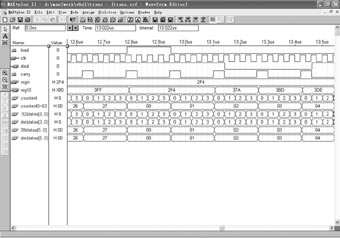

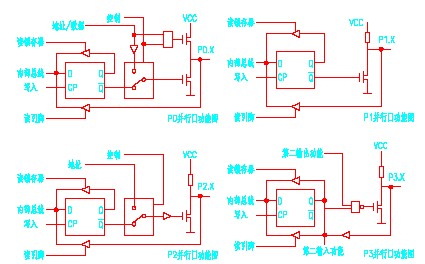

本系統(tǒng)是用ALTERA公司的CPLD開(kāi)發(fā)工具M(jìn)AX+plusII。它支持多種輸入方式,給設(shè)計(jì)開(kāi)發(fā)提供了極大的方便。系統(tǒng)的主體部分仍是用原理圖輸入方式。由于庫(kù)中提供了現(xiàn)在的芯片,所以使用很方便。原理圖輸入部分如圖2和圖3所示。圖2主要完成單片機(jī)與ISA接口通信中的數(shù)據(jù)傳輸和握手判斷。

?

D[0..7] 單片機(jī)的8位雙向數(shù)據(jù)總線(xiàn);

PCD[0..7] ISA接口的8位雙向數(shù)據(jù)總線(xiàn);

PCRD ISA接口的讀有效信號(hào);

PCWR ISA接口的寫(xiě)有效信號(hào);

判斷單片機(jī)已寫(xiě)數(shù)據(jù)或讀走數(shù)據(jù);

PCSTATE 單片機(jī)用此查詢(xún)ISA接口已取走數(shù)據(jù);

MSCRD 單片機(jī)的讀有效信號(hào);

MCSWR 單片機(jī)的寫(xiě)有效信號(hào);

INT0 單片機(jī)的外部中斷信號(hào);

當(dāng)MCUWR信號(hào)有效后,單片機(jī)把數(shù)據(jù)鎖存于74LS374(1)中,此時(shí),PCSTATE變?yōu)楦唠娖健C104用STATE信號(hào)選通74LS244來(lái)判斷數(shù)據(jù)位PCD0是否為高電平,如果為高,說(shuō)明單片機(jī)送來(lái)了數(shù)據(jù),那么使PCRD有效,從數(shù)據(jù)存器74LS374(1)中取走數(shù)據(jù)。此時(shí),PCSTATE變?yōu)榈碗娖剑瑔纹瑱C(jī)通過(guò)判斷此信號(hào)為低電平來(lái)判定PC104已取走了數(shù)據(jù),可以發(fā)下一個(gè)數(shù)據(jù)。

當(dāng)PCWR信號(hào)有效后,PC104把數(shù)據(jù)鎖存于74LS374(2)中,此時(shí),INT0變?yōu)榈碗婇c,單片機(jī)產(chǎn)生外部中斷,使MCSRD信號(hào)有效,從數(shù)據(jù)鎖存器74LS374(2)中取走裝飾,INT0變?yōu)楦唠娖健C104用STATE信號(hào)選通74LS244判斷數(shù)據(jù)位PCD1是否為高電平,如果為高電平,說(shuō)明單片機(jī)取走了數(shù)據(jù),可以發(fā)送下一個(gè)數(shù)據(jù)。 PC104與單片機(jī)進(jìn)行通信,最關(guān)鍵的就是速度匹配問(wèn)題。由于PC104的速度快,而單片機(jī)的速度較慢,所以,要在PC104的IOCHRDY處插入等待周期,如圖3所示。

IOCHRDY 用來(lái)使ISA接口等待5個(gè)時(shí)鐘周期;

DLY_D 延時(shí)輸入信號(hào);

DLY_CK 延時(shí)等待時(shí)鐘信號(hào);

DLY_CLR 等待清除信號(hào),為開(kāi)始下一次送數(shù)周期作準(zhǔn)備;

DELAY 延時(shí)5個(gè)時(shí)鐘周期后的輸出信號(hào),作為DLY_CLR信號(hào)的輸入;

SYSCLK ISA接口的系統(tǒng)時(shí)鐘信號(hào)。

在MCS51與PC104進(jìn)行通信的過(guò)程中,DLY_D信號(hào)一直有效(高電平)。在信號(hào)SYSCLK的作用下,每5個(gè)時(shí)鐘周期DELAY信號(hào)有效一次,即為高電平。此時(shí)DLY_CLR信號(hào)有效(低電平),IOCHRDY信號(hào)變?yōu)楦唠娖剑琍C104可以讀寫(xiě)數(shù)據(jù)。

地址譯碼部分采用文本輸入方式,用ALTERA公司的硬件設(shè)計(jì)開(kāi)發(fā)語(yǔ)言AHDL(Altera Hardware Description Language)。AHDL是一種模塊化的高級(jí)語(yǔ)言,完全集成于MAX+plusII系統(tǒng)中,特別適合于描述復(fù)雜的組合邏輯、狀態(tài)機(jī)和真值表,地址譯碼部分用文本輸入方式,這充分體現(xiàn)了文本輸入方式的優(yōu)點(diǎn)。文本輸入內(nèi)容如下:

(

PCA[9..0] : INPUT;

AEN,IOR,IOW : INPUT;

RESETDR,DELAY : INPUT;

A[15..14] :INPUT;

RD,WR : INPUT;

DLY_D : OUTPUT;

DLY_CK : OUTPUT;

DLY_CLR : OUTPUT;

STATE : OUTPUT;

PCRD : OUTPUT;

PCWR : OUTPUT;

MCURD : OUTPUT;

MCUWR : OUTPUT;

)

BEGIN

!DLY_CLR=RESETDR#DELAY;

DLY_D=!AEN & (PCA[9..1]= =H"110");

DLY_CK=!AEN & (PCA[9..1]= =H"110")&(!IOR # ! IOW);

!PCWR=!AEN&(PCA[9..0]= =H"220")& !IOW;

!PCRD=!AEN&(PCA[9..0]= =H"220")& !IOR;

!STATE=!AEN&(PCA[9..0]= =H"221")&!IOR;

!MCSRD=([15..14]= =H"1")& !RD;

!MCSWR=(A[15..14]= =H"2"& !WR;

END;

說(shuō)明:PCA[9..0]是PC104的地址信號(hào),A[15..14]是單片機(jī)的地址信號(hào),PC104用到端口地址220H和221H。

3 通信軟件設(shè)計(jì)

PC104是基于ISA總線(xiàn)的,在系統(tǒng)軟件設(shè)計(jì)中要防止地址沖突。PC104中使用A0~A9地址位來(lái)表示I/O端口地址,即可有1024個(gè)口地址:前512個(gè)供系統(tǒng)板使用,后512個(gè)供擴(kuò)充槽使用。當(dāng)A9=0時(shí)表示為系統(tǒng)板上的口地址;A9=1時(shí),表示擴(kuò)充插槽接口卡上的口地址[2]。因此,采用保留的口地址220H和221H,保證不會(huì)發(fā)生地址沖突。

本程序中PC104采用查詢(xún)方式接收數(shù)據(jù),單片機(jī)用中斷方式接收數(shù)據(jù)。

#define pcreadwrite 0x220 /*PC104讀寫(xiě)數(shù)據(jù)口地址*/

#define pcrdstate 0x221 /*PC104查詢(xún)狀態(tài)口地址*/

PC104寫(xiě)數(shù)據(jù)函數(shù):

Void pcwrite(int port,unsigned char ch)

{ outportb(pcreadwrite,ch);

while ((inportb(pcrdstate)&0x02)!=0x02); /*等待單片機(jī)讀走數(shù)據(jù)*/

{ }

}

單片機(jī)讀子程序:

MCUWR:MOV DPTR,#4000H

MOVX A,@DPTR

RETI

PC104讀數(shù)據(jù)函數(shù):

Unsigned char pcread(int port)

{ while((inportb(pcrdstate)&0x01)!=0x01);/*等待單片機(jī)寫(xiě)數(shù)據(jù)*/

{}

return inportb(pcreadwrite);

}

單片機(jī)寫(xiě)子程序:

MCUWR:MOV DPTR,#8000H

MOVX @DPTR,A

;等待PC104讀走數(shù)據(jù)

RET

4 結(jié)論

用CPLD實(shí)現(xiàn)單片機(jī)與ISA總線(xiàn)接口的并行通信,電路結(jié)構(gòu)簡(jiǎn)單、體積小,1片CPLD芯片足夠,并且控制方便,實(shí)時(shí)性強(qiáng),通信效率高。本設(shè)計(jì)方法已成功地應(yīng)用于作者開(kāi)發(fā)的各種數(shù)據(jù)采集系統(tǒng)中,用作單片機(jī)與PC104之間的并行數(shù)據(jù)通信,效果非常理想。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論