摘要: HDLC(高級數據鏈路控制)的一般實現方法為采用ASIC器件和軟件編程等。應用ASIC器件時設計簡單,但靈活性較差;軟件編程方法靈活,但占用處理器資源多,執行速度慢,實時性不易預測。FPGA器件采用硬件處理技術,可以反復編程,能夠兼顧速度和靈活性,并能多路并行處理,實時性能能夠預測和仿真。在中小批量通信產品的設計中,FPGA是取代ASIC實現HDLC功能的一種合適選擇。 采用Altera公司的FPGA芯片,在MAX+plus II軟件平臺上實現了多路HDLC電路的設計,并已在某通信產品樣機中應用成功。

關鍵詞: 數據通信; HDLC; CRC校驗; FPGA; MAX+plus II

1 引言

HDLC(High-level Data Link Control Procedures, 高級數據鏈路控制規程)廣泛應用于數據通信領域,是確保數據信息可靠互通的重要技術。實施HDLC的一般方法通常是采用ASIC(Application Specific Integrated Circuit,特定用途集成電路) 器件和軟件編程等。

HDLC的ASIC芯片有Motorola公司的MC92460、ST公司的MK5025、Zarlink公司的MT8952B等。這些集成電路使用簡易,功能針對性強,性能可靠,適合應用于特定用途的大批量產品中。但由于HDLC標準的文本較多,ASIC芯片出于專用性的目的難以通用于不同版本,缺乏應用靈活性。例如CCITT、ANSI、ISO/IEC等都有各種版本的HDLC標準,有的芯片公司還有自己的標準,對HDLC的CRC(Cyclical Redundancy Check,循環冗余碼校驗)序列生成多項式等有不同的規定。況且,專用于HDLC的ASIC芯片其片內數據存儲器容量有限,通常只有不多字節的FIFO(先進先出存儲器)可用。對于某些應用來說,當需要擴大數據緩存的容量時,只能對ASIC芯片再外接存儲器或其它電路,ASIC的簡單易用性就被抵銷掉了。 HDLC的軟件編程方法功能靈活,通過修改程序就可以適用于不同的HDLC應用。但程序運行占用處理器資源多,執行速度慢,對信號的時延和同步性不易預測。對于多路信號的HDLC應用,處理器的資源占用率與處理路數成正比,所以軟件HDLC一般只能用于個別路數的低速信號處理。

FPGA(Field Programmable Gate Array, 現場可編程門陣列)采用硬件技術處理信號,又可以通過軟件反復編程使用,能夠兼顧速度和靈活性,并能并行處理多路信號,實時性能能夠預測和仿真。FPGA芯片雖成本略微高于ASIC芯片,但具有貨源暢通、可多次編程使用等優點。目前FPGA單片所含的邏輯門和片上存儲器的容量越做越大,百萬門級的可編程邏輯芯片已成為尋常產品。在中小批量通信產品的設計生產中,用FPGA實現HDLC功能是一種值得采用的方法。正是有鑒于此,Innocor、Xilinx等公司推出了能在FPGA中實現HDLC功能的IP Core(Intellectual Property Core,知識產權核),但這些IP Core需要付費購買許可(License)才能使用,且在應用中受到各種限制。

本文從HDLC的基本定義出發,通過對FPGA設計輸入的模塊化描述,介紹一種能夠在可編程邏輯芯片中實現HDLC功能的方法。

?

2 HDLC的幀結構和CRC校驗

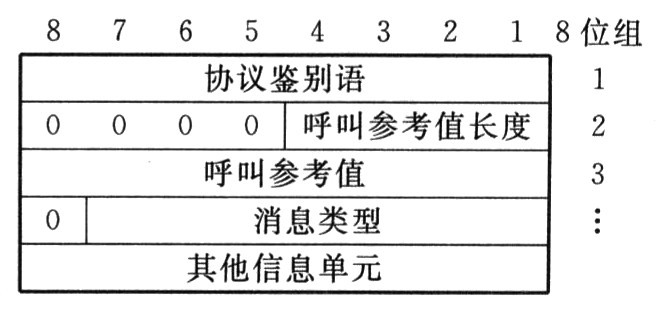

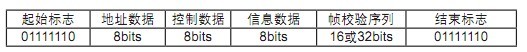

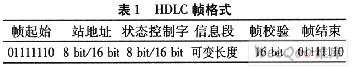

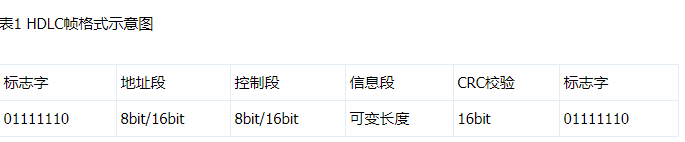

HDLC規程主要由幀結構、規程要素、規程類別三個部分組成[1]。為了使FPGA的設計能夠實現HDLC的基本功能并能按照各項標準的規定靈活采用不同的CRC校驗算法,首先回顧一下HDLC基本的幀結構形式。

HDLC是面向比特的鏈路控制規程,其鏈路監控功能通過一定的比特組合所表示的命令和響應來實現,這些監控比特和信息比特一起以幀的形式傳送。

以下是ISO/IEC 3309標準規定的HDLC的基本幀結構。

|

起始標志 |

地址數據 |

控制數據 |

信息數據 |

幀校驗序列 |

結束標志 |

|

01111110 |

8bits |

8bits |

8bits |

16或32bits |

01111110 |

其它的HDLC標準也有類似的幀結構。每幀的起始和結束以"7E"(01111110)做標志,兩個"7E"之間為數據段(含地址數據、控制數據、信息數據)和幀校驗序列。幀校驗采用CRC算法,對除了插入的"零"以外的所有數據進行校驗。為了避免將數據中的"7E"誤為標志,在發送端和接收端要相應地對數據流和幀校驗序列進行"插零"及"刪零"操作。

各種HDLC間的區別之一是幀校驗序列的CRC算法不同,這種不同表現在幾個方面:

a. 幀校驗序列的位數不同,如16位和32位等。

b. CRC生成多項式不同,如對于16位的CRC,CCITT V.41標準的多項式是x16 + x12 + x5 + 1,ANSI CRC-16標準的多項式是x16 + x15 + x2 + 1等。

c. CRC序列的初始化條件不同,如可以初始化為全"0"、全"1"等。

d. CRC計算結果的處理方式不同,如可以直接把CRC結果發送,或對CRC結果取反后再發送等。

e. 對接收到的數據做CRC校驗時,合格判據不同。因為有了上述的不同處理,自然會得到不同的結果,由此造成合格判據不同。例如有的標準以校驗結果"1D0F"判為無錯誤[2]。而有的ASIC芯片以校驗結果"F0B8"判為無錯誤[3]。

顯然,對于這些應用,可編程邏輯芯片正可以發揮自己的特長。

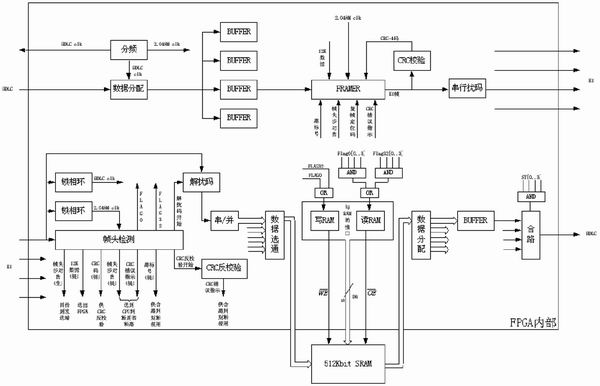

3 用FPGA實現HDLC功能的原理框圖

對FPGA器件進行功能設計一般采用的是"Top to Down"("從頂到底")的方法,亦即根據要求的功能先設計出頂層的原理框圖,該圖通常由若干個功能模塊組成。再把各個模塊細化為子模塊,對較復雜的設計還可把各子模塊分成一層層的下級子模塊,各層的功能可以用硬件描述語言或電路圖來實現。

圖2即為一個典型的單路雙向HDLC電路的頂層電原理圖設計實例。

從圖中可以看出,該電路由接口模塊interface、HDLC數據發送模塊transmitter和HDLC

數據接收模塊receiver三部分組成。當需要多路HDLC收發器時,可將若干個transmitter模塊和receiver模塊組合使用。以下分別對這幾個模塊做簡要說明。

圖2

3.1 接口模塊interface

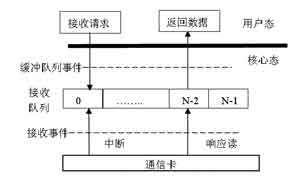

interface模塊的主要功能是:向FPGA提供時鐘;通過數據、地址總線和讀寫信號向FPGA讀寫并行數據;產生和處理中斷信號。

在本例中,時鐘是24.576MHz。時鐘的頻率越高,就可以處理更高速的數據信號,但相應的芯片功耗和價格要高一些。時鐘頻率還和HDLC的數據收發速率有關,一般選時鐘頻率正好是HDLC數據速率的整數倍,以便簡化HDLC 收發器定時電路的設計。

數據總線的寬度取決于所使用的外部CPU類型。由于目前較多使用的是16位的單片處理器,因此這里采用16位的數據總線cpu_data[15..0]。當然也可以根據需要采用8位或32位的數據總線。

地址總線的寬度主要取決于HDLC所需要的數據緩存區的大小。例如,設計16路雙向HDLC收發器,每個收發器要緩存256字節的數據,在使用16位數據總線時可求得地址總線的寬度至少應有12位。由于外部CPU要對FPGA實施一些控制功能,FPGA中還要考慮留出一定的地址來安排命令寄存器和狀態寄存器,所以實際所需的地址總線還要再寬一些。如果HDLC的路數很多,緩存器又定得很大,FPGA內部的地址寬度會超過外部CPU可提供的地址寬度,這時可以向FPGA的特定寄存器寫入數據鎖存后作為內部地址來擴展地址總線。

對于外部CPU來說,FPGA可以看成是一個普通芯片,通過片選CS/、讀寫信號RD/和WR/,就可以選中FPGA并對其進行讀寫操作。

當FPGA需要向CPU傳遞信息時,中斷信號輸出端interrupt/ 變為低電平,CPU響應后可到FPGA中的狀態寄存器去讀取詳細的中斷信息并做出相應的處理。

3.2 HDLC數據發送模塊transmitter

transmitter模塊的主要功能是:對本路HDLC數據發送時鐘tx_clk整形后產生內部發送時鐘inter_tx_clk, 產生鎖相于inter_tx_clk的FPGA工作時鐘tx_op_clk;鎖存外部CPU寫入的發送數據并按指定時序啟動發送;在發送數據段前加上"7E"起始標志;對發送數據逐位做CRC計算并將計算結果附在發送數據之后;對包括CRC計算值在內的數據進行"插零"操作并附上"7E"結束標志把結果輸出。

transmitter模塊由發送定時子模塊tx_timer、發送數據子模塊tx_data、標志發生器子模塊7e_generator、發送CRC計算子模塊tx_crc、數據插零子模塊zero_insert等組成,見圖3。

HDLC的數據發送時鐘tx_clk由外部電路提供(在必要時也可把這些外部電路綜合進同一片FPGA),工作時鐘op_clk的頻率比數據發送時鐘高出幾倍并鎖相于數據發送時鐘,能以高于比特發送的速度執行對數據的操作。

圖3

待發送數據是由外部CPU通過interface模塊寫入指定地址的緩沖存儲器的。在HDLC中,可以選用的緩沖存儲器類型有FIFO(先進先出)存儲器、DPRAM(雙端口RAM)存儲器、移位寄存器等。在本設計中,發送數據的存儲使用的是數據鎖存移位寄存器。使用這種寄存器的優點是:寫入的待發送數據經鎖存后,可在任何時候(包括正在發送時)對數據的任何部分讀出檢查,并且數據可直接串行移位做CRC計算,簡化FPGA設計。這種寄存器由數據鎖存器和串行移位寄存器兩部分組成,占用芯片資源較多,但對于有大量片上存儲器可用的FPGA 芯片來說,這點是不成問題的。

"7E"標志加在發送數據段的前后,其時序由tx_timer確定。在發送啟動時,先發"7E"再發數據。

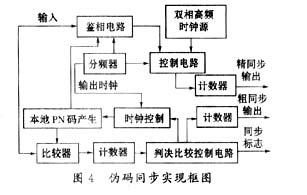

發送CRC計算子模塊tx_crc由16個帶賦能端e的D觸發器組成,其電路圖見圖4,可用來按照x16 + x12 + x5 + 1的生成多項式進行16位CRC計算。該電路的原理可參看數據通信教科書,此處不再贅述,僅說明幾點:

a. 如果要改變CRC的位數,只要改變D觸發器的數量。

b. 如果要改變CRC生成多項式,僅需將多項式中非零系數項對應的D觸發器的輸出與d1信號"異或"后送至下一個D觸發器的輸入。

c. 通過給D觸發器的PRN端或CLRN端置"0",就可改變CRC計算的初始值。

這個例子可說明用FPGA設計的CRC電路具有極大的靈活性。

圖4

發送的數據經CRC計算并將計算結果附在數據后面,再經"插零"后附上"7E"標志就可輸出。"插零"操作由子模塊zero_insert完成。子模塊tx_data監視著每一個串行移出的數據,當發現數據流中出現五?quot;1"時,就輸出控制信號1f_detect/ 暫停數據移位,此時子模塊zero_insert向數據流插入一個"0"比特。

子模塊tx_data中存儲著待發送數據的比特長度值,并隨時和已發送數據的比特長度值比較。當出現兩者相等的情況時,判定為數據發送完畢,子模塊tx_crc停止CRC計算并把計算結果輸出。再經過16個數據時鐘后,子模塊7e_generator發出"7E"作為結束標志,同時向接口模塊interface發出tx_data_empty信號表示數據發送結束。

3.3 HDLC數據接收模塊receiver

receiver模塊的主要功能是:產生與本路HDLC接收數據時鐘同步的FPGA工作時鐘;在接收的數據流中檢測有無"7E"標志;當檢測到數據流中有"1F"信號時,對數據進行"刪零"操作;對經"刪零"后的數據進行CRC校驗;把接收到的數據進行串/并轉換并存入雙端口RAM;當接收到結束標志后,檢查CRC校驗值是否正確,向interface模塊發出rx_data_ready信號。

receiver模塊由接收定時子模塊rx_timer、接收數據子模塊rx_data、標志檢測子模塊7e_detector、數據刪零子模塊zero_delete、接收CRC校驗子模塊 rx_crc等組成,見圖5。

對比receiver模塊和transmitter模塊,雖然兩者一些子模塊的功能是相逆的,但其原理是類似的,因此不再重復說明。

在receiver模塊中采用了雙端口RAM來作為HDLC接收數據緩存器,因此FPGA內部向雙端口RAM寫入數據和FPGA外部向雙端口RAM讀出數據可以分別通過兩個端口獨立的數據地址總線同時進行。

圖5

限于篇幅,以上所述僅為設計HDLC電路的大致框架,許多細節已被省略了。

4 應用實例

根據上述設計方法,已成功地在可編程邏輯芯片上實現了多路HDLC的設計。

設計輸入在Altera公司的MAX+plus II[4] 10.0版本的軟件平臺上進行。首先考慮擬設計的電路有多少路HDLC收發器、需要多少內部存儲器、工作速率多少、對外部處理器的接口有何要求等。根據這些考慮,以電路圖和AHDL語言結合的方法進行設計輸入。對于時序電路,主要采用電路圖輸入的方法;對于地址譯碼等功能電路,采用AHDL語言描述;對于存儲器、鎖存器及移位寄存器等,盡量采用MAX+plus II中LPM(參數化模塊庫)提供的模塊來實現。全部設計輸入完成后,對設計進行編譯、仿真。在波形仿真器內給定輸入信號,檢查輸出的波形是否符合設計預期。反復多次進行修改,確認無誤后可將設計結果下載到FPGA芯片。

FPGA芯片選用的是Altera公司的ACEX 1K系列[5]。該系列是Altera公司面向通信和消費類數字產品推出的低功耗、高密度的高性能FPGA集成電路,具有可與ASIC相比擬的價位。ACEX 1K系列器件內部采用基于LUT的架構,最大邏輯門數為10萬門;可提供的片內存儲器最大為49152比特;最小時延僅數納秒,實際電路總時延在數十納秒左右;能夠滿足一般HDLC的要求。ACEX 1K系列FPGA器件工作電壓為2.5伏,I/O接口電壓可選為2.5伏或3.3伏,配置芯片可選Altera公司的EPC1型。

設計出的具有多路HDLC功能的FPGA芯片已應用于船舶AIS(Automatic Identification System,自動識別系統)樣機的無線數據通信鏈路中,成功實現了雙向數據通信。

5 結束語

FPGA提供了一種取代ASIC芯片的選擇,以上所述僅是用FPGA實現HDLC功能的一個簡單介紹。在通信產品的設計中,如果原已使用了可編程邏輯芯片來實現某些功能的話,只要改用更大容量的FPGA芯片,就可以將類似于HDLC這樣的功能都集成進去。如使用Altera 公司的Quartus II軟件來進行同類設計,則功能更強大,更能支持"Top to Down"的設計方法,并且支持Cyclone等大規模FPGA芯片。此外,Xilinx公司新推出90納米工藝的Spartan-3系列低成本FPGA芯片,也可作為取代ASIC的一種選擇。顯然,FPGA在通信技術中的應用十分值得重視,并正受到越來越多的關注。(2003.11)

參考文獻

1 張德民. 數據通信,P.194. 北京:科學技術文獻出版社,1997.8

2 ISO/IEC 3309: Information technology-Telecommunications and information exchange between systems-High-level data link control (HDLC) procedures-Frame structure, P.4. Switzerland: International Electrotechnical Commission, Jun 2002

3 Zarlink Semiconductor. MT8952B HDLC Protocol Controller, P.3-64. March 1997

4 Altera Corporation. MAX+plus II, Version 10.0, Sep 2000

5 Altera Corporation. ACEX 1K Programmable Logic Family Data Sheet, Altera Digital Library,Version 3,2001

電子發燒友App

電子發燒友App

評論