- 所有數(shù)字邏輯的基本結(jié)構(gòu)

- 16-QAM調(diào)制器

- 編碼和碼元映射

- 平方根升余弦濾波器

- 設(shè)計(jì)技巧

- 5 MHz載波

- 分布式計(jì)算(DA)技術(shù)

- 濾波器的實(shí)現(xiàn)

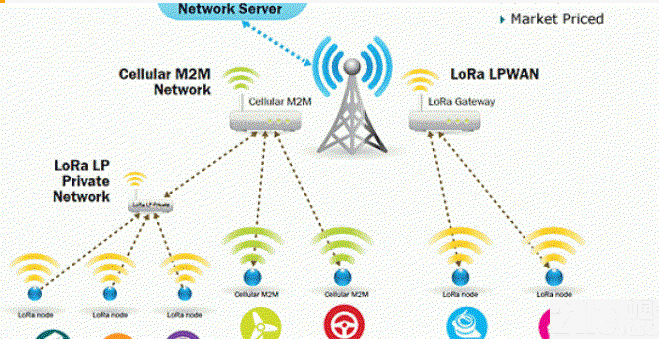

用現(xiàn)場(chǎng)可編程門陣列(FPGA)設(shè)計(jì)軟件無線電和調(diào)制解調(diào)器可與DSP芯片媲美。雖然FPGA可輕而易舉地實(shí)現(xiàn)卷積編碼器等復(fù)雜邏輯功能,但在實(shí)現(xiàn)大量復(fù)雜計(jì)算方面卻有很大的缺陷。即使用最快的FPGA來實(shí)現(xiàn)矩陣乘法器,其成本和性能也抵不上一個(gè)僅值5美元的DSP芯片。在用CAD工具設(shè)計(jì)時(shí)DSP仍是首選芯片,但是隨著分布式計(jì)算(DA)技術(shù)的應(yīng)用,F(xiàn)PGA再次受到設(shè)計(jì)師的喜愛。

FPGA的特性之一是結(jié)構(gòu)靈活。事實(shí)上無線和調(diào)制解調(diào)數(shù)據(jù)通道的功能模塊很容易映射到獨(dú)立和并行的硬件節(jié)點(diǎn)上。采用一個(gè)只能分時(shí)運(yùn)行的數(shù)字信號(hào)處理器時(shí),調(diào)度多個(gè)時(shí)間要求緊迫的任務(wù)需要非常復(fù)雜的編程,而采用FPGA就避免了這一問題。

我們將在設(shè)計(jì)16-QAM射頻發(fā)射數(shù)據(jù)泵的同時(shí)介紹FPGA特性,并詳細(xì)描述如何方便地把數(shù)據(jù)通道功能模塊轉(zhuǎn)換為Xilinx 4000系列FPGA的邏輯電路,從而準(zhǔn)確地估計(jì)所需邏輯電路的數(shù)量。雖然滿足相同系統(tǒng)需求及使用同一類型FPGA的16-QAM數(shù)據(jù)泵的設(shè)計(jì)曾在公開文獻(xiàn)中發(fā)表過,但報(bào)道中的邏輯電路數(shù)量似乎比實(shí)際需要多得多。為了急于投放市場(chǎng),產(chǎn)品很可能不用CAD工具進(jìn)行設(shè)計(jì)。完全依賴CAD工具也未必總能得出最優(yōu)的方案,還要付出大量辛勤的汗水、經(jīng)驗(yàn)和創(chuàng)造性工作。

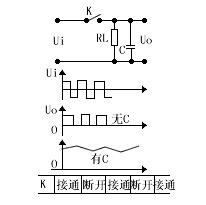

所有數(shù)字邏輯的基本結(jié)構(gòu)

只要有足夠的與非門及或非門等通用邏輯門即可構(gòu)建任何數(shù)字邏輯。FPGA具有充足的邏輯門。Xilinx 4000系列的邏輯門采用真值表的形式,或者采用更為通用的16 字 x 1比特查找表(LUT)的形式,它可實(shí)現(xiàn)四個(gè)輸入變量(查找表的地址線)的任意布爾函數(shù)功能。由于產(chǎn)生的函數(shù)功能通常相當(dāng)于多個(gè)與非門的組合,所以LUT被視為基本的邏輯單元。Xilinx 4000系列可配置邏輯模塊(CLB)包括兩個(gè)16字的LUT,可組合產(chǎn)生五輸入變量的任意布爾函數(shù)。此外LUT還可設(shè)置成兩個(gè)16 x 1 RAM或一個(gè)32 x 1 RAM。

CLB成二維方陣排列,CLB及它們之間的互連可以分別配置。最小的XC4002包含一個(gè)8 x 8的CLB矩陣,最大的XC4085XL則包含一個(gè)48 x 48的CLB矩陣。每個(gè)LUT連接一個(gè)高達(dá)100 MHz的觸發(fā)器。

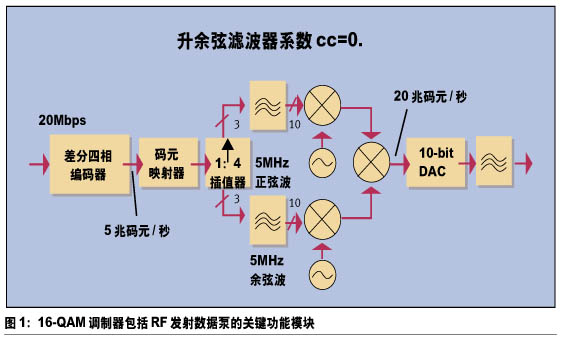

16-QAM調(diào)制器

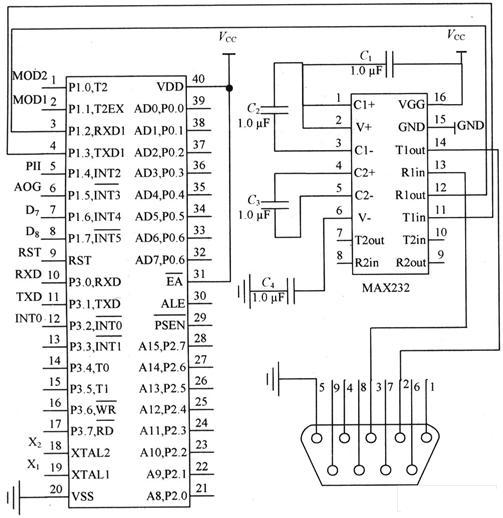

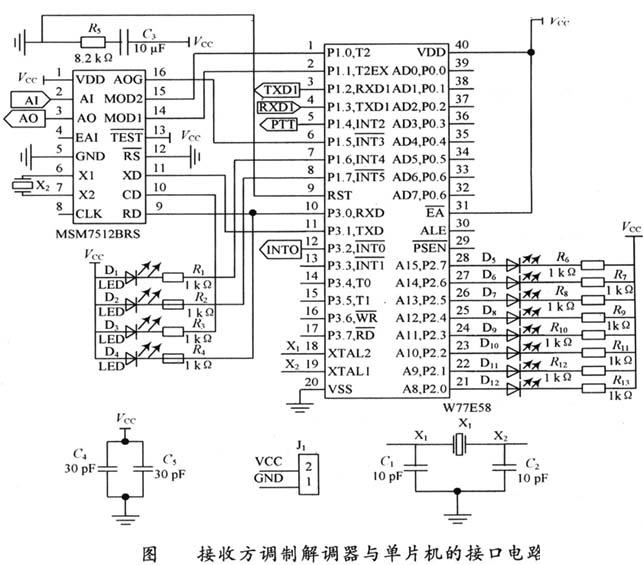

16-QAM調(diào)制器包括RF發(fā)射數(shù)據(jù)泵的關(guān)鍵功能模塊(見圖1)。20-Mbps串行數(shù)據(jù)分為4比特碼元組(symbol)后,以每秒5兆碼元的速率并行送至一個(gè)差分編碼器和碼元映射器(symbol mapper)。該映射器產(chǎn)生3比特的正交分量對(duì)。然后這些分量對(duì)由一對(duì)平方根升余弦濾波器進(jìn)行脈沖整形,經(jīng)過插值達(dá)到每秒20兆碼元,再由5MHz載波進(jìn)行調(diào)制,將各輸出相加后進(jìn)行數(shù)模轉(zhuǎn)換。設(shè)計(jì)的關(guān)鍵是采用一對(duì)插值脈沖整形濾波器。

為了有效地實(shí)現(xiàn)這種設(shè)計(jì)方法,有必要在確定邏輯門的總數(shù)時(shí),將編碼和映射功能模塊以及一個(gè)5MHz調(diào)制器也考慮進(jìn)去。

編碼和碼元映射

在確定編碼器和信號(hào)映射器的邏輯數(shù)目時(shí),我們可以借鑒過去標(biāo)準(zhǔn)調(diào)制解調(diào)器的設(shè)計(jì)。如V.32中的編碼器包括一個(gè)提供180度雙相保護(hù)的差分編碼器和一個(gè)能加入冗余以減小接收器的位誤差率(BER)的卷積編碼器。編碼器和映射器都是有限狀態(tài)機(jī)實(shí)現(xiàn)的,所有狀態(tài)由五個(gè)寄存器(2.5個(gè) CLB)實(shí)現(xiàn),連接邏輯由八個(gè)二輸入異或門(4個(gè)CLB)及三個(gè)二輸入與門(1.5 CLB)構(gòu)成。在這個(gè)16-QAM發(fā)送器中,一個(gè)串并轉(zhuǎn)換寄存器(2個(gè)CLB)捕獲到四個(gè)20-Mbps的串行比特后形成一個(gè)4比特碼元,這樣編碼器就可以處理降低到每秒5兆碼元的數(shù)據(jù)流,而這種速率CLB很容易處理。數(shù)據(jù)通道控制需要沿著數(shù)據(jù)通道的寄存器進(jìn)行時(shí)鐘控制,所需CLB的數(shù)量少于15個(gè)。接著,一個(gè)經(jīng)編碼的5比特輸出碼元對(duì)應(yīng)映射器的地址線,很簡(jiǎn)單,該映射器是一對(duì)3比特輸出的LUT。

這些輸出作為正交分量(I和Q) 映射一個(gè)二維平面(星座)內(nèi)的碼元位置。64個(gè)交叉點(diǎn)(星)中僅有16個(gè)代表有效的碼元位置。映射器的大小為32字 x 3比特 x 2 即6個(gè)CLB。這些功能模塊的CLB總數(shù)是31個(gè)。

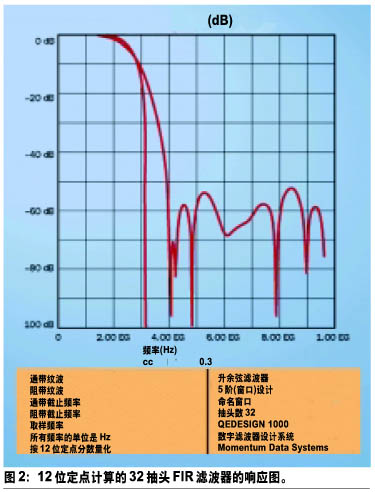

平方根升余弦濾波器

平方根升余弦濾波器是在傳輸通道的有限帶寬內(nèi)抑制碼元相互干擾的一種可行方法。頻譜由發(fā)射器和接收器單元分別調(diào)制,形成了平方根升余弦濾波器。濾波器形狀及其系數(shù)用QEDesign 1000軟件輔助開發(fā)。圖2為12比特定點(diǎn)計(jì)算的32抽頭有限脈沖響應(yīng)(FIR)濾波器的響應(yīng)圖。我們將采用一個(gè)12比特濾波器模型并確定其邏輯門數(shù)(采用12比特量化的方式,QEDesign程序僅需28個(gè)對(duì)稱系數(shù),但是這種設(shè)計(jì)方案將使用一個(gè)完全32抽頭對(duì)稱FIR濾波器)。

設(shè)計(jì)技巧

平方根升余弦濾波器用于I、Q兩個(gè)通道上的頻譜形成。當(dāng)以每秒5兆采樣速率產(chǎn)生I、Q采樣點(diǎn)時(shí),濾波器為調(diào)制器產(chǎn)生每秒20兆的采樣數(shù)據(jù)。這樣,濾波器充當(dāng)了一個(gè)1:4的插值器。相應(yīng)的計(jì)算量(采用對(duì)稱系數(shù))為2通道 x 16階對(duì)稱抽頭x每秒20兆采樣點(diǎn) = 每秒640兆乘法-累加運(yùn)算。這一速度大大超過大多數(shù)定點(diǎn)DSP芯片的運(yùn)行速度。現(xiàn)在FPGA已成為一種很有吸引力的選擇,但是,還要挑選一種濾波器形式使之能最有效地映射到基于CLB的設(shè)計(jì)。

現(xiàn)在有多種邏輯電路的配置或形式可實(shí)現(xiàn)FIR濾波器。最主要的有直接形式(即一種常用的軟件模型)、帶變量的轉(zhuǎn)置形式(已由專用濾波器芯片實(shí)現(xiàn))以及多相濾波器(適用于多速率應(yīng)用)。但這些形式都不能采用對(duì)稱系數(shù)的方法來減少乘法計(jì)算量。設(shè)計(jì)多速率濾波器的一個(gè)技巧是在采樣點(diǎn)-系數(shù)平面標(biāo)出信號(hào)流軌跡。

縱軸表示采樣點(diǎn),水平軸表示系數(shù),畫出的數(shù)據(jù)軌跡顯示了90度翻轉(zhuǎn)后濾波器的響應(yīng)圖。因?yàn)橄禂?shù)對(duì)稱,只需列出一半濾波器系數(shù)。插入系數(shù)為K,即在輸入采樣點(diǎn)間填入K-1個(gè)零點(diǎn),從而得到32抽頭FIR的V形軌跡。雖然輸入數(shù)據(jù)采樣點(diǎn)間隔為200 ns,但新的軌跡點(diǎn)必須每隔50ns一點(diǎn)。

由該圖可以得出兩種計(jì)算模型。第一種是轉(zhuǎn)置形式的變形,其中非零輸入采樣值與所有32個(gè)系數(shù)的乘積在部分和寄存器中相加。32個(gè)乘積相加后并且濾波器的完全響應(yīng)輸出后,乘法-累加器電路可用于計(jì)算新軌跡。在此,每隔200ns進(jìn)行32次MAC運(yùn)算。第二種模型是延遲相加,即FIR濾波器的直接形式。正如在濾波器軌跡中所看到的,需要八個(gè)存儲(chǔ)的采樣值計(jì)算一個(gè)濾波響應(yīng)。通過計(jì)算五個(gè)連續(xù)濾波器響應(yīng)我們可觀察到表1給出的模型。

由同樣的八個(gè)采樣點(diǎn)輸入組可計(jì)算出四個(gè)連續(xù)的20MHz響應(yīng)。只使用了兩組濾波器系數(shù)。濾波器系數(shù)與每個(gè)采樣數(shù)據(jù)組的第三和第四個(gè)響應(yīng)( y d和y e )順序相反。這些響應(yīng)方程能映射到有效的FPGA電路中嗎?當(dāng)然能!關(guān)鍵就是應(yīng)用分布式計(jì)算技術(shù),所有現(xiàn)行的設(shè)計(jì)工具都不具備這種算法。實(shí)現(xiàn)響應(yīng)方程組以前,可先作一下簡(jiǎn)化。

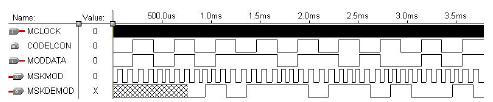

5 MHz載波

載波調(diào)制的簡(jiǎn)單方程為:Y(k) = yI(k)cos(wC*t) + yQ(k)sin(wC*t),其中wC為載波頻率= 2p(5 MHz), I和Q表示同相和正交的碼元分量。

此方程每50 ns執(zhí)行一次。一個(gè)碼元周期內(nèi)(200 ns)僅有四個(gè)載波值。這些值可以方便地定義為:cos(wC*t) = 1, 0, -1, 0和sin(wC*t)= 0, 1, 0, -1 ,1。

調(diào)制輸出既不需要任何乘法或加法,也不需要每隔50ns計(jì)算一次I、Q濾波器響應(yīng)。50 ns計(jì)算一個(gè)I響應(yīng)接著在下一個(gè)50 ns計(jì)算一個(gè)Q響應(yīng),然后再計(jì)算I響應(yīng)、Q響應(yīng),周而復(fù)始。

分布式計(jì)算(DA)技術(shù)

DA是專門針對(duì)乘積和方程的一種計(jì)算技術(shù),方程中的一項(xiàng)乘積因子是常數(shù)。DA設(shè)計(jì)可實(shí)現(xiàn)門級(jí)高效率、串行位算法及高性能位并行運(yùn)算,它是經(jīng)典的串/并綜合方案。DA技術(shù)可應(yīng)用于很多重要的線性、時(shí)不變數(shù)字信號(hào)處理算法,如濾波器(FIR和IIR)、變換(快速傅立葉變換[FFT])及矩陣向量乘積,如8 x 8離散余弦變換(DCT)。

二十多年前就有了DA技術(shù),已經(jīng)證實(shí)它不適于可編程DSP的定點(diǎn)指令集結(jié)構(gòu)。然而,DA非常適于FPGA實(shí)現(xiàn),尤其是如Xilinx CLB的LUT邏輯模塊。用Xilinx XC3000系列的FPGA設(shè)計(jì)DA FIR濾波器早在1992年就已提出。

DA電路中沒有獨(dú)立的乘法器。乘法是由LUT完成的。DA預(yù)存一個(gè)方程式中所有部分乘積項(xiàng)的和,并且根據(jù)所有輸入變量位查表(此處為DALUT)運(yùn)算。串行DA電路有一個(gè)獨(dú)立的DALUT,它從最低的有效位開始查表。部分乘積的輸出和存儲(chǔ)在累加器中,這種方法讓我們想起了早期計(jì)算機(jī)中的移位相加子程序,連續(xù)的DALUT輸出累加到部分乘積的二進(jìn)制下移累加和中。這樣可得到一個(gè)真正的雙精度結(jié)果。

濾波器的實(shí)現(xiàn)

平方根升余弦濾波器的數(shù)據(jù)通道由已可轉(zhuǎn)換為CLB的標(biāo)準(zhǔn)功能模塊定義。每隔200ns將映射器輸出的3比特I、Q信號(hào)傳至并串轉(zhuǎn)換移位寄存器(PSR)。RAM移位寄存器(SR)鏈中存儲(chǔ)了七個(gè)先前的碼元。前三個(gè)濾波器響應(yīng)Y b , Y c , Y d與移位寄存器中的循環(huán)數(shù)據(jù)一起運(yùn)算。PSR還需要一個(gè)反饋通道,但RAM SR在只讀時(shí)循環(huán)受到模塊尋址的影響。這里的模塊有六個(gè),前三次移位用于Y b,緊接著的三次用于Y c,最后三次則是用于Y d。在計(jì)算Y e時(shí),數(shù)據(jù)沿SR鏈下移。這種模塊尋址模式隨著前級(jí)傳輸(寫)的數(shù)據(jù)不斷重復(fù)。所有十二次移位和相應(yīng)的PSR加載、RAMSR尋址及寫控制都來源于60MHz系統(tǒng)時(shí)鐘。

由于相同的系數(shù)組要用于兩個(gè)采樣周期,一個(gè)用于I通道數(shù)據(jù)計(jì)算,另一個(gè)用于Q通道數(shù)據(jù)計(jì)算,用一組DALUT和2/1復(fù)用器將串行數(shù)據(jù)流導(dǎo)向相應(yīng)的地址端口。這些端口可以表示DALUT的結(jié)構(gòu)。h 3端口的邏輯高電平選擇部分乘積和包含h 3的所有內(nèi)存地址。與此類似,h 7端口的邏輯高電平選擇所有包含h 7的所有地址,h 3和h 7端口的邏輯高電平選擇所有包含h 3和h 7的地址。剩余的六個(gè)系數(shù)仍采用這種模式。事實(shí)上,八個(gè)系數(shù)將需要2 8或256個(gè)字存儲(chǔ)。對(duì)于12比特系數(shù)的情況,將需要 (每個(gè)CLB為256/32 字) x 12 = 96 個(gè)CLB。另一個(gè)訣竅是使用兩個(gè)DALUT,每個(gè)需要四個(gè)系數(shù)并增加它們的輸出。這樣CLB的數(shù)目則減少到(2 x 24)/32 x 12 + 13/2 (并行加法器) = 18.5 個(gè)CLB.

同樣的簡(jiǎn)化也可用到以h 1開始的第二套濾波器系數(shù)中。采用2/1復(fù)用器可分時(shí)共享并行加法器。該加法器擴(kuò)展為13個(gè)比特后,輸入到前述執(zhí)行移位和加法運(yùn)算的標(biāo)量累加器。當(dāng)輸入變量的符號(hào)位傳輸給DALUT時(shí),就進(jìn)行減運(yùn)算。此過程可通過在DALUT輸出增加EXOR門并向累加器第一級(jí)進(jìn)位的標(biāo)準(zhǔn)方法來完成。對(duì)于負(fù)響應(yīng)Y d和Y e,數(shù)據(jù)采樣可不管符號(hào)位,而對(duì)所有的DALUT輸出數(shù)據(jù)取反來求補(bǔ)。

對(duì)于分?jǐn)?shù)二進(jìn)制補(bǔ)碼格式的I、Q數(shù)據(jù),濾波器系數(shù)要進(jìn)行調(diào)整以防在最后輸出中溢出。十個(gè)最高有效位可加載到D/A轉(zhuǎn)換驅(qū)動(dòng)寄存器中。

濾波器數(shù)據(jù)通道的CLB總數(shù)為71.5個(gè),F(xiàn)PGA輸出端口帶有觸發(fā)器,可作為D/A轉(zhuǎn)換的驅(qū)動(dòng)寄存器。算上編碼器(31個(gè)CLB)及定時(shí)和控制功能(估計(jì)要少于50個(gè)CLB)在內(nèi),總數(shù)大約為159個(gè)CLB,正好可置于Xilinx XC4000系列中較小(稍大于最小)的芯片中,即XC4005 (196個(gè)CLB)。如果采用Xilinx Virtex等更高級(jí)的FPGA器件,則可減少CLB的數(shù)量并提高性能。

整個(gè)設(shè)計(jì)可確保60MHz系統(tǒng)時(shí)鐘條件下的性能。數(shù)據(jù)流采取統(tǒng)一形式且單向傳輸。可以插入管道寄存器(不增加CLB)以縮短組合路徑。通過標(biāo)量累加器的十四級(jí)的進(jìn)位鏈?zhǔn)亲铋L(zhǎng)的組合路徑。然而,通過內(nèi)置預(yù)進(jìn)位電路可確保足夠的速度余量

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論