摘要: 介紹一種用于衛星姿態測量的CMOS圖像敏感器--STAR250的時序驅動信號,并使用Verilog HDL語言設計驅動時序電路。經布線、仿真、測試后驗證了驅動信號的正確性。

關鍵詞: Verilog HDL STAR250 CMOS 圖像敏感器

CMOS圖像敏感器是近年來興起的一類固態圖像傳感器。CMOS圖像敏感器具有低成本、低功耗(是CCD耗的1/1000~1/100)、簡單的數字接口、隨機訪問、運行簡易(單一的CMOS兼容電池供給)、高速率(可大于1000幀/秒)、體積小以及通過片上信號處理電路可以實現智能處理功能等特點而得到廣泛應用。有些CMOS圖像敏感器具有標準的I2C總線接口,可方便應用到系統中。有些沒有這類總線接口電路的專用CMOS圖像敏感器需要增加外部驅動電路。由于CMOS敏感器的驅動信號絕大部分是數字信號,因此可采用FPCA通過Verilog HDL語言編程產生驅動時序信號。Verilog HDL語言是IEEE標準的用于邏輯設計的硬件描述語言,具有廣泛的邏輯綜合工具支持,簡潔易于理解。本文就STAR250這款CMOS圖像敏感器,給出使用Verilog HDL語言設計的邏輯驅動電路和仿真結果。

1 CMOS圖像敏感器STAR250STAR250是一款專為衛星天文導航的星跟蹤器(tracker)設計的CMOS圖像敏感器。由于太空中含有大量輻射,芯片中加入了抗輻射電路以提高空間應用的可靠性。STAR250的技術指標如下:

(1)0.5μm CMOS工藝;

(2)512x512分辨率,像素大小25μmx25μm;

(3)每個像素4個光敏二極管,提高MTF(幅值轉換功能)和減少PRNU(非均一化光響應);

(4)抗輻射設計;

(5)片上雙采樣電路抵消FPN(固定模式噪聲);

(6)電子快門:(7)最大30幀/秒;

(8)可以取子窗口;

(9)片上10位ADC;

(10)陶瓷JLCC-84針封裝。

STAR250是有源像素的線掃描CMOS圖像敏感器。所有像素的輸出都連接到列總線,并且在列總線上每例都有一個列放大器。使用二次采樣技術,控制列放大器可以從讀出信號中減去光敏單元上一次采集殘留的電荷。片上ADC獨立于敏感器,可以使用也可以通過軟件關閉,而用外部的ADC。STAR250為了應用方便有多種讀出數據的方法(窗口方式、電子快門等),不同的讀出方式有不同的時序要求。

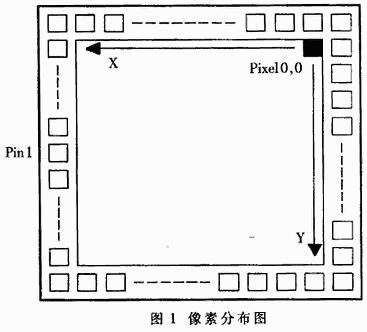

傳統的計算機或打印機的圖像座標系定義左上角為原點(0,0),在STAR250中定義右上角為原點(0,0),如圖1。這樣敏感器輸出數字信號后能夠方便地轉換為計算機格式的圖像,方便后續的處理。窗口掃描方式是從上向下、從左向右一個像素一個像素地掃描。

圖3

2 STAR250時序信號STAR250通過兩個步驟完成圖像的采集。第一步是逐行掃描RESET像素。行內像素RESET后,本行自上一次RESET或讀出后積累的所有光敏電荷被排空。從RESET行像素開始新的曝光周期。第二步是本次曝光周期數據讀出。以電壓的形式讀出,然后經過ADC轉換為數字量。由于電荷采用排出式讀取,CMOS圖像敏感器的像素讀出不可恢復,讀取過程也相當于RESET像素,所以CMOS敏感器行RESET的速度與讀取速度一樣。

STAR250通過三個指針標定整個圖像地址:Yrd當前掃描行,Yrst當前RESET行,Yrd當前讀出像素。這三個指針都有相應的移位寄存器,通過設置這三個寄存器的初始值可以調整采集窗口的大小和位置。圖像采集的流程圖如圖2。每秒鐘的圖像幀數通過設置Yrd和Yrst進行控制,曝光周期也由這兩個量控制。這個時間量可以用空間距離(行距)表示,定義DelayLines=︱Yrst-Yrd+︱。由于每一行的RESET和讀取時間是固定的,所以DelayLines如果固定那么幀率也就固定了。將DelayLines轉換成像素的有效積分時間(曝光時間),是將Delay-Lines乘以讀取一行像素所用的時間。讀取一行像素所用的時間由四部分組成:(1)行中有效像素的個數(由行的長度定義);(2)讀取一個像素所用的時間;(3)像素累積電荷轉換為數字量的時間;(4)選擇新一行所用的時間。例如在主時鐘頻率為12MHz時,像素的輸出頻率為主時鐘的二分頻6MHz,因此一行像素所需要的時間為512×1/6MHz=85.3μs。再加上換行所需時間,一行像素的讀取時間大約90μs左右。因此可以根據這個時間設置DelayLines來控制曝光時間。

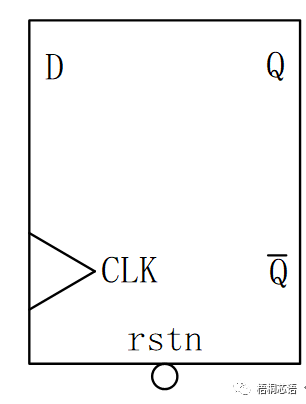

3 Verilog HDL驅動時序設計經過以上分析可知,CMOS圖像敏感器采集時可以分為RESET過程和采集過程。時間上兩個過程是獨立的,如圖3。但在FPGA內部處理這兩部分的電路物理上是同時存在,因此必須將相應的信號通過置標志位的方法置為有效或無效。

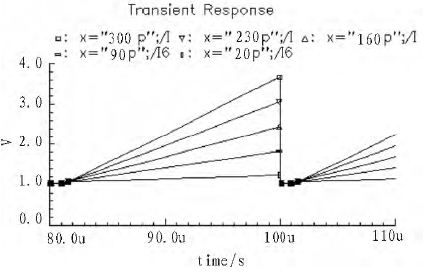

STAR250所需數字驅動信號共28個,其中SELECT信號在正常使用時,直接接PCB板的Vcc。因此需FPGA控制的驅動信號有27個。根據采集過程可以把信號劃分為列放大器信號,包括CAL、Reset、Lr、S、R、LdY。這6個信號在每一行的初始化部分都要用到,因此可以編寫到一個模塊(ColControl)中;模式信號(PaternCtrl)模塊用來設置CMOS敏感器的工作模式及初始地址,包括G0、G1、Bitlnvert和Addr[8:0]共12個信號。其中G0、G1用來設計輸出的放大倍數,BitInvert用于將輸出取反,Addr[8:0]則設置采集的起始地址;行讀出信號控制模塊(YlCtrl)產生行讀出地址的同步信號SyncYl及時鐘驅動信號ClkYl;行RESET信號控制模塊(YrCtrl)產生行RE-SET地址的同步信號SyncYr及時鐘驅動信號ClkYr;像素控制模塊(RowCtrl)產生行內像素初始地址的裝載信號LdX及同步信號SyncX;行內時鐘信號模塊(RowClk)產生列內像素的時鐘驅動CLKX、ADC驅動時鐘信號CLkAdc及輸出三態控制信號TriAdc。系統的輸入信號為主時鐘CLK、EosX行內像素結尾信號、EosYl幀內行結尾信號、EosYr幀內RESET行結尾信號、芯片的RESET信號。經過這樣劃分后的模塊化Verilog程序就比較易寫了。經過頂層模塊綜合生成的網表如圖4。布線仿真時序圖如圖5,其中時鐘信號過于密集變成黑色帶狀,同樣輸出時鐘CIkX及ClkAdc也是黑色帶狀。在時序上ClkX與ClkAdc是反相關系,在TriAdc保持低電平時輸出有效。所設計的驅動信號仿真波形與理論波形十分符合。這樣就完成了STAR250的時序驅動電路設計。

使用Verilog語言設計時序邏輯具有很高的效率。結合CMOS敏感器特性可以方便地開發出驅動時序電路。但必須對CMOS圖像敏感器的信號分析準確,正確分離那些獨立的信號和共用的信號,用時序邏輯設計驅動信號,用組合邏輯實現不同采集過程時間上的分離。布線延遲是必須考慮的,采用流水線技術可以預測延遲,保證信號的正確性。雖然文中并未給出像素ADC輸出的存儲電路,但實際上直接使用TriAdc信號作為SRAM的片選,ClaAdc的低電平作為寫信號,SRAM的地址在ClkAdc的上升沿增加、下降沿寫入。這樣就可以完成圖像數據的存儲。以上Verilog程序在FLEXl0kl0上布線實現。經示波器觀察邏輯正確,CMOS敏感器正常工作。

基于Verilog HDL的CMOS圖像敏感器驅動電路設計

- Verilog(109207)

- HDL(47095)

相關推薦

微光CMOS圖像傳感器讀出電路設計

當前固體微光器件以EBCCD 及EMCCD 器件為主,隨著CMOS 工藝及電路設計技術的發展, 微光CMOS 圖像傳感器的性能在不斷提高,通過采用專項技術,微光CMOS 圖像傳感器的性能已接

2015-08-05 10:21:38 6815

6815

6815

6815CMOS圖像傳感器電路設計

當前固體微光器件以EBCCD 及EMCCD 器件為主,隨著CMOS 工藝及電路設計技術的發展, 微光CMOS 圖像傳感器的性能在不斷提高,通過采用專項技術,微光CMOS 圖像傳感器的性能已接近EMCCD 的性能, 揭開了CMOS 圖像傳感器在微光領域應用的序幕。

2016-01-18 09:59:58 7695

7695

7695

7695

Verilog HDL代碼

誰可以用Verilog HDL寫一個關于彩燈控制器的代碼,要求如下:1、設計一個彩燈控制器,使彩燈(LED管)能連續發出四種以上不同的顯示形式;2、隨著彩燈顯示圖案的變化,發出不同的音響聲。教學提示

2016-03-10 17:08:14

Verilog HDL入門教程

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174 Verilog HDL 基本語法

2017-12-08 14:39:50

Verilog HDL入門教程(全集)

的具體控制和運行。Verilog HDL語言不僅定義了語法,而且對每個語法結構都定義了清晰的模擬、仿真語義。因此,用這種語言編寫的模型能夠使用 Ve r i l o g仿真器進行驗證。語言從C編程語言

2020-11-30 19:03:38

Verilog HDL測試激勵之時鐘激勵

(59)Verilog HDL測試激勵:時鐘激勵11.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)Verilog HDL測試激勵:時鐘激勵15)結語1.2 FPGA簡介FPGA

2022-02-23 06:57:59

Verilog HDL的基本語法

Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結構描述

2019-09-06 09:14:16

Verilog HDL的時鐘激勵簡析

(69)Verilog HDL測試激勵:時鐘激勵21.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)Verilog HDL測試激勵:時鐘激勵25)結語1.2 FPGA簡介FPGA

2022-02-23 07:31:44

Verilog HDL經典黑金資料(入門教程+實例精講+百例設計)

設計方法學等方面的基本概念出發來研究和探討用于數字信號處理等領域的復雜硬線邏輯電路的設計技術和方法。特別強調利用Verilog硬件描述語言的Top-Down設計方法的介紹。Verilog HDL電路設計指導書

2018-12-10 15:31:15

Verilog HDL語言是什么

嵌入式開發Verilog教程(二)——Verilog HDL設計方法概述前言一、Verilog HDL語言簡介1.1 Verilog HDL語言是什么1.2前言在數字邏輯設計領域,迫切需要一種共同

2021-11-08 09:30:31

CCD和CMOS圖像傳感器的比較

相互補充的關系。在有些時候,兩種傳感器之間是互補的,可以適用在不同的應用場合。CCD提供很好的圖像質量、抗噪能力和相機設計時的靈活性。盡管由于增加了外部電路使得系統的尺寸變大,復雜性提高,但在電路設計

2015-09-06 10:58:21

【FPGA學習】Verilog HDL有哪些特點

Verilog HDL 的特點Verilog HDL 語言不僅定義了語法,而且對每個語法結構都定義了清晰的模擬、仿真語義。使用這種語言編寫的模型可以方便地使用 Verilog 仿真器進行驗證

2018-09-18 09:33:31

基于I2C總線的CMOS圖像傳感器接口電路設計

摘要:詳細闡述了一種用于百萬像素數碼相機的CMOS圖像傳感器接口電路設計及其VLSI 實現:文章按照數碼相機的功能要求進行整體設計,由上而下討論了各個子模塊的設計,并給出了電路的 FPGA 驗證:本

2018-11-30 11:27:23

如何實現CMOS圖像敏感器驅動電路設計?

如何實現CMOS圖像敏感器驅動電路設計?CMOS圖像敏感器STAR250的技術指標是什么?如何實現Verilog HDL驅動時序設計?

2021-04-20 06:59:27

如何對Verilog HDL的復位激勵進行測試

(70)Verilog HDL測試激勵:復位激勵21.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)Verilog HDL測試激勵:復位激勵25)結語1.2 FPGA簡介FPGA

2022-02-23 06:29:31

微光CMOS圖像傳感器讀出電路設計

當前固體微光器件以EBCCD 及EMCCD 器件為主,隨著CMOS 工藝及電路設計技術的發展, 微光CMOS 圖像傳感器的性能在不斷提高,通過采用專項技術,微光CMOS 圖像傳感器的性能已接

2018-11-12 15:37:40

求一款基于VerilogHDL的CMOS圖像敏感器驅動電路設計

本文就STAR250這款CMOS圖像敏感器,給出使用Verilog HDL語言設計的邏輯驅動電路和仿真結果。

2021-04-23 06:50:58

Verilog HDL綜合實用教程

Verilog HDL 綜合實用教程第1章 基礎知識第2章 從Verilog結構到邏輯門第3章 建模示例第4章 模型的優化第5章 驗證附錄A 可綜合的語言結構附錄B 通用庫

2009-07-20 11:21:13 86

86

86

86基于Verilog HDL語言的FPGA設計

采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實現了RISC_CPU 的關鍵部件狀態控制器的設計,以及在與其它各種數字邏輯設計方法的比較下,顯示出使用Verilog HDL語言的優越性.關鍵詞

2009-08-21 10:50:05 69

69

69

69Verilog-HDL實踐與應用系統設計

Verilog-HDL實踐與應用系統設計本書從實用的角度介紹了硬件描述語言Verilog-HDL。通過動手實踐,體驗Verilog-HDL的語法結構、功能等內涵。在前五章,以簡單的實例列舉了Verilog-HDL的用法;

2009-11-14 22:57:40 146

146

146

146Verilog HDL華為入門教程

Verilog HDL 華為入門教程

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的基本要素,能

2010-02-11 08:35:38 140

140

140

140Verilog HDL入門教程(華為絕密資料)

Verilog HDL入門教程(華為絕密資料)

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的

2010-04-02 11:52:21 0

0

0

0什么是Verilog HDL?

什么是Verilog HDL?

Verilog HDL是一種硬件描述語言,用于從算法級、門級到開關級的多種抽象設計層次的數字系統建模。被建模的數字系統

2009-01-18 14:53:26 3678

3678

3678

3678

Verilog HDL語言在FPGA/CPLD開發中的應用

摘 要:通過設計實例詳細介紹了用Verilog HDL語言開發FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優越性。

2009-06-20 11:51:28 1857

1857

1857

1857

Verilog HDL程序基本結構與程序入門

Verilog HDL程序基本結構與程序入門

Verilog HDL程序基本結構

Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的

2010-02-08 11:43:30 2185

2185

2185

2185Verilog HDL語言實現時序邏輯電路

Verilog HDL語言實現時序邏輯電路

在Verilog HDL語言中,時序邏輯電路使用always語句塊來實現。例如,實現一個帶有異步復位信號的D觸發器

2010-02-08 11:46:43 4468

4468

4468

4468VHDL和Verilog HDL語言對比

VHDL和Verilog HDL語言對比

Verilog HDL和VHDL都是用于邏輯設計的硬件描述語言,并且都已成為IEEE標準。VHDL是在1987年成為IEEE標準,Verilog HDL

2010-02-09 09:01:17 10317

10317

10317

10317Verilog HDL與VHDL及FPGA的比較分析

Verilog HDL與VHDL及FPGA的比較分析. Verilog HDL優點:類似C語言,上手容易,靈活。大小寫敏感。在寫激勵和建模方面有優勢。

2011-01-11 10:45:29 1182

1182

1182

1182Verilog HDL程序設計教程_王金明

《Verilog HDL 程序設計教程》對Verilog HDL程序設計作了系統全面的介紹,以可綜合的設計為重點,同時對仿真和模擬也作了深入的闡述。《Verilog HDL 程序設計教程》以Verilog-1995標準為基礎

2011-09-22 15:53:36 0

0

0

0Verilog基本電路設計指導書

本文列舉了大量的基本電路的Verilog HDL 代碼,使初學者能夠迅速熟悉基本的HDL 建模;同時也列舉了一些常用電路的代碼,作為設計者的指導。

2012-04-26 16:03:17 0

0

0

0Verilog_HDL的基本語法詳解(夏宇聞版)

Verilog_HDL的基本語法詳解(夏宇聞版):Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結

2012-10-08 14:48:31 0

0

0

0設計與驗證Verilog HDL(吳繼華)

本書以實例講解的方式對HDL語言的設計方法進行介紹。全書共分9章,第1章至第3章主要介紹了Verilog HDL語言的基本概念、設計流程、語法及建模方式等。

2012-11-28 13:32:57 943

943

943

943Verilog HDL 數字設計教程(賀敬凱)

Verilog HDL 數字設計教程【作者:賀敬凱;出版社:西安電子科技大學出版社】(本資料為ppt) 內容簡介:介紹了Verilog HDL語言,狀態機設計,仿真,還有好幾個可綜合設計的舉例,除了

2012-11-28 13:43:11 489

489

489

489Verilog HDL入門教程

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡單的設計代碼并能夠進行一些簡單設計的Verilog HDL建模。

2016-07-15 15:27:00 0

0

0

0設計與驗證:Verilog HDL(清晰PDF)

;第4章至第6章主要討論如何合理地使用Verilog HDL語言描述高性能的可綜合電路;第7章和第8章重點介紹了如何編寫測試激勵以及Verilog的仿真原理;第9章展望HDL語言的發展趨勢。

2016-10-10 17:04:40 566

566

566

566使用Verilog語言實現CMOS圖像敏感器時序驅動電路設計

CMOS圖像敏感器是近年來興起的一類固態圖像傳感器。CMOS圖像敏感器具有低成本、低功耗(是CCD耗的1/1000~1/100)、簡單的數字接口、隨機訪問、運行簡易(單一的CMOS兼容電池供給

2019-05-03 10:02:00 2593

2593

2593

2593

Verilog HDL入門教程之Verilog HDL數字系統設計教程

本文檔的主要內容詳細介紹的是Verilog HDL入門教程之Verilog HDL數字系統設計教程。

2018-09-20 15:51:26 80

80

80

80Verilog HDL入門教程

本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL 設計方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡單的設計代碼并能夠進行一些簡單設計的Verilog HDL建模。

2019-02-11 08:00:00 95

95

95

95Verilog語法基礎

Verilog HDL是一種用于數字系統設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結構描述的語言。

2019-03-08 14:29:12 12094

12094

12094

12094Verilog HDL語言及VIVADO的應用

中國大學MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-08-06 06:12:00 3450

3450

3450

3450

數字設計FPGA應用:Verilog HDL語言基本結構

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-02 07:10:00 2914

2914

2914

2914

Verilog-HDL深入講解

Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。

2019-11-13 07:03:00 3029

3029

3029

3029Verilog HDL的基礎知識詳細說明

硬件描述語言基本語法和實踐

(1)VHDL 和Verilog HDL的各自特點和應用范圍

(2)Verilog HDL基本結構語言要素與語法規則

(3) Verilog HDL組合邏輯語句結構

2019-07-03 17:36:00 53

53

53

53CMOS圖像敏感器STAR250的的邏輯驅動電路設計和仿真

STAR250是一款專為衛星天文導航的星跟蹤器(tracker)設計的CMOS圖像敏感器。由于太空中含有大量輻射,芯片中加入了抗輻射電路以提高空間應用的可靠性。STAR250的技術指標如下:

2020-04-12 18:02:00 2581

2581

2581

2581

Verilog HDL和VHDL的區別

Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。 Verilog HDL

2020-06-17 16:13:11 12911

12911

12911

12911Verilog HDL數字集成電路設計原理與應用第二版PDF電子書免費下載

HDL集成電路測試程序和測試方法、復雜數字電路和系統設計舉例、數字集成電路Verilog HDL的EDA工具和使用等。

2020-07-21 08:00:00 0

0

0

0Verilog HDL語言技術要點

的是硬件描述語言。最為流行的硬件描述語言有兩種Verilog HDL/VHDL,均為IEEE標準。Verilog HDL具有C語言基礎就很容易上手,而VHDL語言則需要Ada編程基礎。另外Verilog

2020-09-01 11:47:09 4002

4002

4002

4002

Verilog HDL語言的設計入門詳細教程

學習內容:使用HDL設計的先進性,Verilog的主要用途,Ⅴerilog的歷史如何從抽象級( levels of abstraction)理解,電路設計,Ⅴerilog描述

2020-10-29 17:30:37 28

28

28

28Verilog教程之Verilog HDL數字集成電路設計方法和基礎知識課件

本文檔的主要內容詳細介紹的是Verilog教程之Verilog HDL數字集成電路設計方法和基礎知識課件

2020-12-09 11:24:19 52

52

52

52Verilog教程之Verilog HDL數字邏輯電路設計方法

在現階段,作為設計人員熟練掌握 Verilog HDL程序設計的多樣性和可綜合性,是至關重要的。作為數字集成電路的基礎,基本數字邏輯電路的設計是進行復雜電路的前提。本章通過對數字電路中基本邏輯電路的erilog HDL程序設計進行講述,掌握基本邏輯電路的可綜合性設計,為具有特定功能的復雜電路的設計打下基礎

2020-12-09 11:24:00 33

33

33

33Verilog HDL為門級電路建模的能力詳解

門電平模型化 本章講述Verilog HDL為門級電路建模的能力,包括可以使用的內置基本門和如何使用它們來進行硬件描述。 5.1 內置基本門 Verilog HDL中提供下列內置基本門: 1) 多輸

2021-03-05 15:23:12 5811

5811

5811

5811

如何使用Verilog HDL描述可綜合電路?

1、如何使用Verilog HDL描述可綜合電路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL語言僅是對已知硬件電路的文本描述。所以編寫前: 對所需實現的硬件

2021-04-04 11:19:00 3838

3838

3838

3838

Verilog HDL verilog hdl和vhdl的區別

Verilog HDL是一種以文本形式描述數字系統硬件的結構和行為的硬件描述語言,也可描述邏輯電路圖、邏輯表達式等。Verilog HDL和VHDL是目前主流的、最受歡迎的兩種硬件描述語言。

2021-07-23 14:36:55 9911

9911

9911

9911教你們如何使用Verilog HDL在FPGA上進行圖像處理

該FPGA項目旨在詳細展示如何使用Verilog處理圖像,從Verilog中讀取輸入位圖圖像(.bmp),處理并將處理結果寫入Verilog中的輸出位圖圖像。提供了用于讀取圖像、圖像處理和寫入圖像

2021-09-23 16:17:07 3476

3476

3476

3476嵌入式開發Verilog教程(二)——Verilog HDL設計方法概述

嵌入式開發Verilog教程(二)——Verilog HDL設計方法概述前言一、Verilog HDL語言簡介1.1 Verilog HDL語言是什么1.2前言在數字邏輯設計領域,迫切需要一種共同

2021-11-03 16:36:01 13

13

13

13(70)Verilog HDL測試激勵:復位激勵2

(70)Verilog HDL測試激勵:復位激勵21.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)Verilog HDL測試激勵:復位激勵25)結語1.2 FPGA簡介FPGA

2021-12-29 19:42:09 1

1

1

1(69)Verilog HDL測試激勵:時鐘激勵2

(69)Verilog HDL測試激勵:時鐘激勵21.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)Verilog HDL測試激勵:時鐘激勵25)結語1.2 FPGA簡介FPGA

2021-12-29 19:42:19 0

0

0

0(59)Verilog HDL測試激勵:時鐘激勵1

(59)Verilog HDL測試激勵:時鐘激勵11.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)Verilog HDL測試激勵:時鐘激勵15)結語1.2 FPGA簡介FPGA

2021-12-29 19:42:29 0

0

0

0(77)Verilog HDL測試激勵:復位激勵3

(77)Verilog HDL測試激勵:復位激勵31.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)Verilog HDL測試激勵:復位激勵35)結語1.2 FPGA簡介FPGA

2021-12-29 19:42:39 0

0

0

0(60)Verilog HDL測試激勵:復位激勵1

(60)Verilog HDL測試激勵:復位激勵11.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)Verilog HDL測試激勵:復位激勵15)結語1.2 FPGA簡介FPGA

2021-12-29 19:42:49 2

2

2

2(76)Verilog HDL測試激勵:時鐘激勵3

(76)Verilog HDL測試激勵:時鐘激勵31.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)Verilog HDL測試激勵:時鐘激勵35)結語1.2 FPGA簡介FPGA

2021-12-29 19:43:00 2

2

2

2FPGA技術之Verilog語法基本概念

Verilog HDL是一種用于數字系統設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結構描述的語言。

2022-12-08 14:00:57 1928

1928

1928

1928使用Verilog HDL描述寄存器的硬件

剛接觸數字集成電路設計,特別是Verilog HDL語言的同學,往往不理解什么時候變量需要設置為wire型,什么時候需要設置成reg型。

2023-07-13 15:53:26 550

550

550

550

二十進制編碼器及Verilog HDL描述 Verilog HDL程序的基本結構及特點

節通過硬件描述語言Verilog HDL對二十進制編碼器的描述,介紹Verilog HDL程序的基本結構及特點。

2023-08-28 09:54:34 1116

1116

1116

1116

電子發燒友App

電子發燒友App

評論