摘要:提出了一種基于FPGA的實時、多分辨率圖像采集系統的控制邏輯設計方案;并對其中的圖像數據預處理和幀存乒乓刷新機制這兩個關鍵技術進行了闡述;為了驗證圖像采集系統在整個圖像處理系統中所起的作用,還對圖像壓縮系統的幀率進行了比較實驗。實驗結果表明,設計并實現的圖像采集系統不僅運行穩定,而且顯著提高了圖像處理系統的整體性能。

關鍵詞:FPGA 圖像采集 圖像壓縮

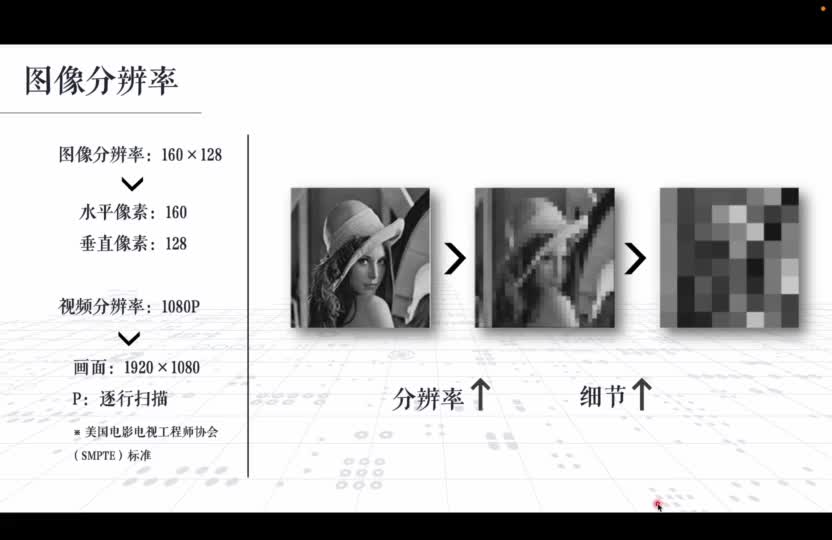

隨著數字多媒體技術的不斷發展,數字圖像處理技術被廣泛應用于可視電話、電視會議、監控系統等各種民用、商用及工業生產領域中。但在這些數字圖像處理系統中,一個突出的問題就是數據量龐大,特別是在圖像幀率及分辨率要求比較高的場合下,僅用專用的視頻壓縮芯片(Video ASIC)、專用的視頻信號處理器(Video DSP)或通用的高性能數字信號處理芯片(DSP),均無法獲得令人滿意的效果。為此,人們提出了多種解決方案,其中比較有代表性的方案有以下兩種:

一是在中央控制器的調度下,兩片或多片圖像處理主芯片并行對圖像進行處理。

二是整個圖像處理系統由圖像采集系統和圖像壓縮系統組成,其中圖像采集系統負責接收原始的圖像數據并對其進行一定的預處理;圖像壓縮系統負責接收圖像采集系統預處理后的數據并進行壓縮。

本文將基于第二種方案,分析其中圖像采集系統的控制邏輯設計思想;并結合圖像壓縮算法的需求,著重介紹圖像數據預處理的控制流程及實現方法;最后通過實驗,對預處理前后圖像處理系統的效率進行比較分析。

1 圖像采集系統的結構及工作原理

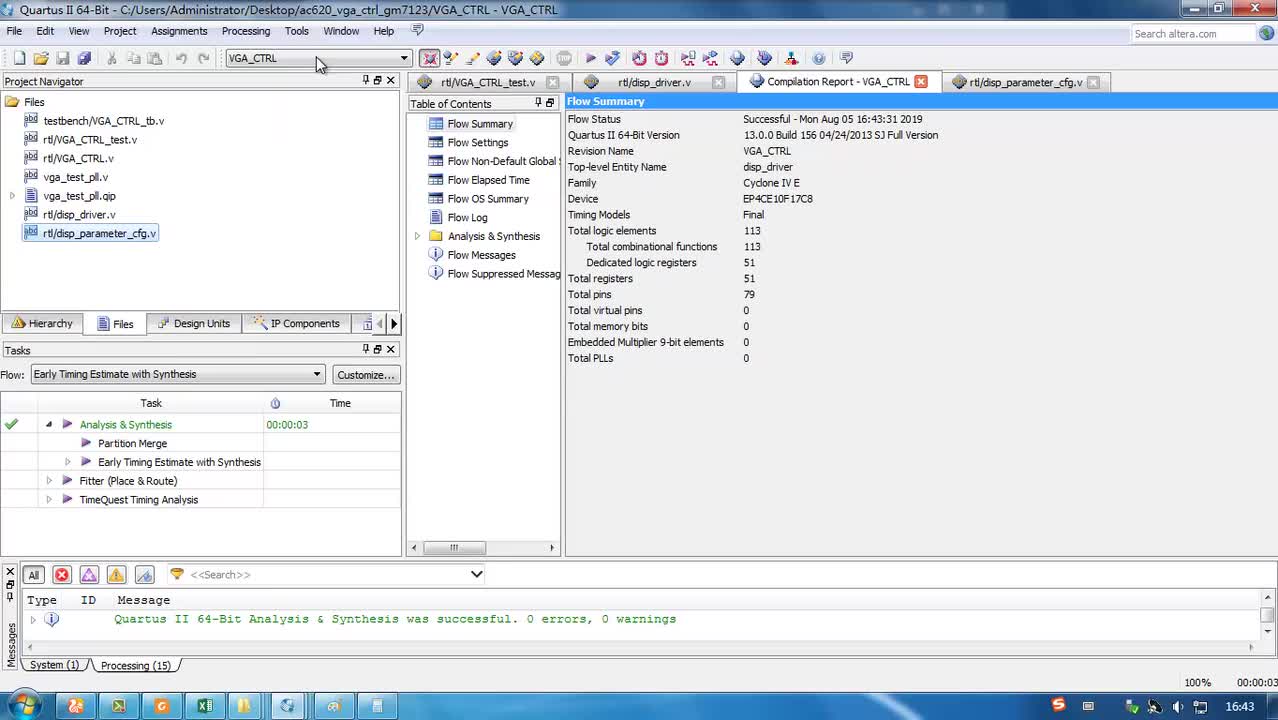

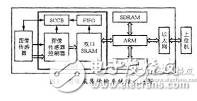

本文以高性能、高集成度、低功耗系列FPGA作為核心部件,利用FPGA的在系統可編程以及控制邏輯實現方式靈活等特點,設計出圖像采集系統。該系統能夠滿足多分辨率灰度和彩色圖像的實時壓縮處理要求,其硬件結構如圖1所示,主要包括A/D轉換部分、幀存部分和核心控制部分。下面分別對這三個部分進行介紹。

1.1 A/D轉換部分

A/D轉換部分即圖1中的視頻解碼器,用來完成模擬視頻信號到數字信號的轉換,產生復合的YUV數據流,并送入采集系統的FPGA中。

A/D轉換部分所選用的視頻解碼器是Philips公司的視頻A/D芯片SAA7111A_4,它不僅具有自動場頻檢測牧場 生而且其場同步參考信號VREF、行同步參考信號HREF、奇偶場標志信號RTS0、像素時鐘信號LLC2幸免可從芯片的輸出管腳直接得到,從而簡化了時鐘鎖相與同步功能模塊的設計,使整個系統的性能和穩定性均有所提高,同時減少了整個系統的功耗[2]。

1.2 幀存部分

幀存部分采用雙幀存結構,包括圖1中的幀存A與幀存B,每個幀存由兩片IDT71V424 SRAM構成,能夠存放720X576分辨率的一幀YUV圖像數據。由于采用了乒乓機制,這種結構能夠使圖像數據的采集與壓縮并行,從而提高圖像的壓縮幀率。

1.3 核心控制部分

采集系統的核心控制部分即圖1中的FPGA。首先對A/D轉換部分的輸出數據流進行一定的預處理;其次將預處理后的數據在幀存乒乓、刷新機帛的控制下寫入適當幀存中;最后完成與圖像壓縮系統的接口控制,即適時幀存的控制權轉交給圖像壓縮系統,由圖像壓縮系統將幀存中的數據讀出后釋放幀存的控制權。另外本部分還負責接收用戶輸入的圖像分辨率、色彩以及相應壓縮碼流傳輸信道的帶寬等控制信息,并在這些信息發生變化時用中斷的方式通知圖像壓縮系統。

核心控制部分所選用的FPGA為Xilinx公司的Virtex-100E繁列,它具有10萬等效系統門,系統時鐘頻率可達240MHz,用戶可用的I/O管腳有196個,核電壓為1.8V,峰值功耗較低[3]。

1.3.1 圖像采集系統控制邏輯功能框圖

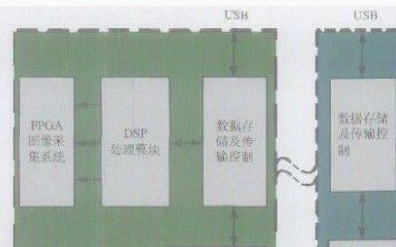

圖像采集系統控制邏輯框圖如圖2所示。①作為采集系統核心控制邏輯的主控模塊,用來調用②~⑥各子功能模塊。子功能模塊②是整個控制邏輯執行的起點,它根據I2C協議來配置視頻解碼器,并且只有I2C配置過程結束后,才能啟動其它子功能模塊的運行。子功能模塊③用于完成圖像采集系統與圖像壓縮系統的交互。子功能模塊④~⑥用于完成圖像采集、預處理、存儲控制等功能。下邊介紹介紹各子模塊的設計思想。

1.3.2 基于I2C配置視頻解碼器

視頻解碼器的初始化配置是由FPGA通過I2C總線完成的,主要包括對視頻解碼器的工作模式、輸出行場同步參考信號的時序關系以及輸出數字信號的格式等進行的設置。

1.3.3 與圖像壓縮系統握手

為了確保圖像壓縮系統與圖像采集系統的同步、需要在FPGA中實現兩者之間的握手機制,主要是接收圖像壓縮系統請示幀存控制權和釋放幀存控制權的信號,并根據FPGA內部邏輯的當前運行狀態進行響應。

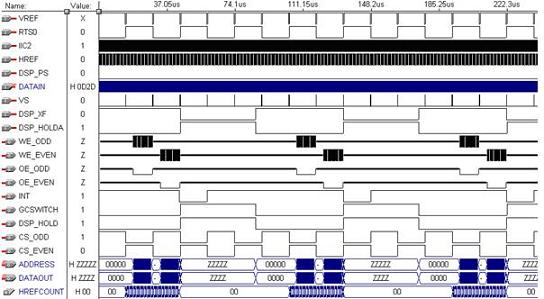

1.3.4 原始圖像數據采集

在一幀圖像數據的采集過程中,最重要的就是對一幀圖像數據開始和結束時刻的判斷。在仔細研究了SAA7111A_4所提供的同步信號(奇偶場標識信號RTS0、場同步參考信號VREF、行同步參考信號HREF)的時序關系的基礎上,用狀態機實現了對采集過程起止點的精確控制。圖3所示為一幀圖像采集期間三個同步信號的時序示意圖。

RTS0信號的上升沿標識一幀新圖像的起點,VREF信號為高電平對應圖像場正程掃描時的有效像素行期間,在有效像素行期間,HREF信號為高電平對應像素有效采樣時間。基于這三個信號確定一幀圖像采集過程起止點的流程如下:

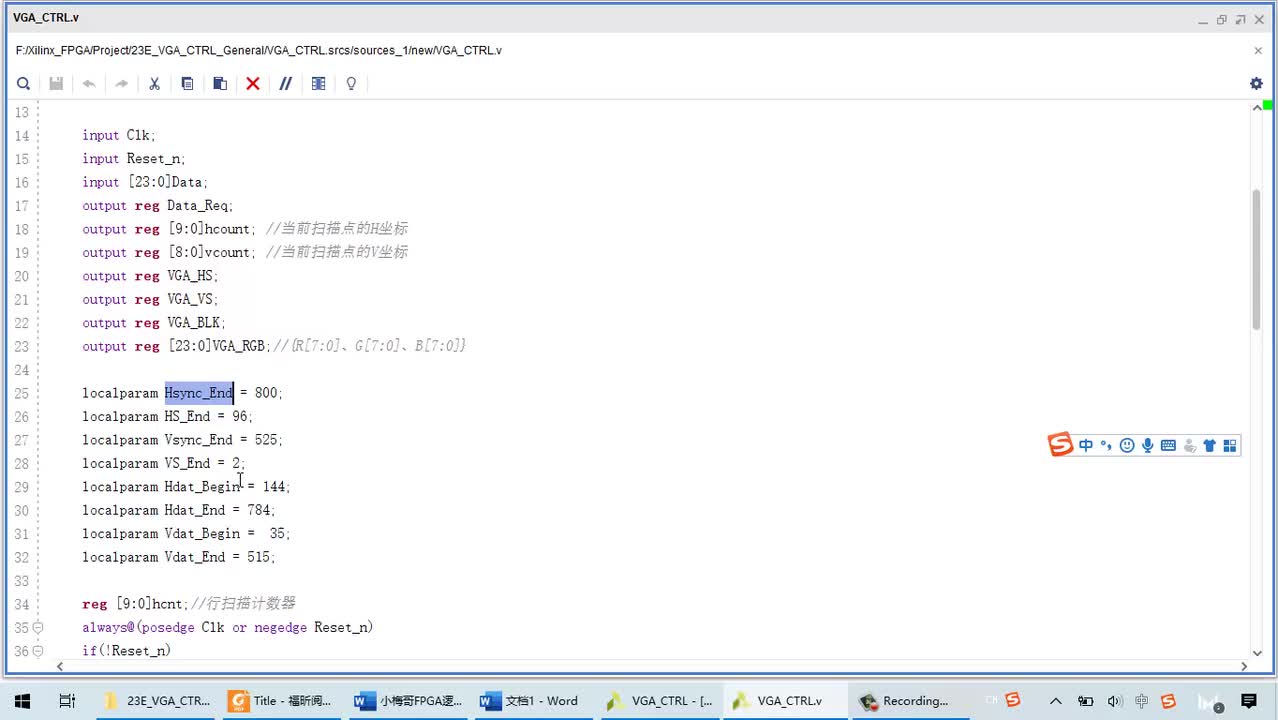

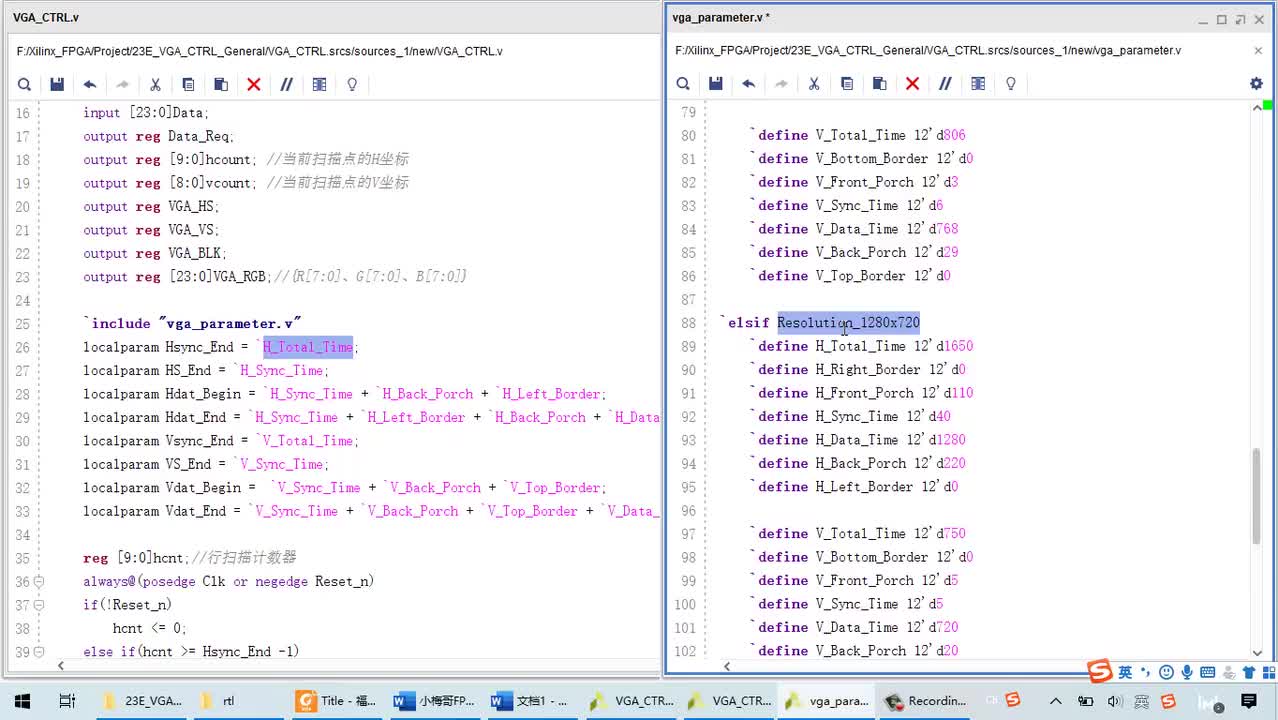

①若檢測到RTS0信號的電平為低,轉到②;②若檢測到RTS0信號的電平為高,轉到③,同時開始一幀新圖像的采集;

③若檢測到VREF信號的電平為高,轉到④;

④若檢測到VREF信號的電平為低,則表明352X288分辨率模式下的一幀圖像采集過程結束或720X576分辨率模式下的第一場圖像采集過程結束,轉到⑤,否則在HREF信號的電平為高期間進行有效的圖像數據采集;

⑤若檢測到VREF信號的電平為高,轉到⑥;

⑥若檢測到VREF信號的電平為低,則表明720X576分辨率模式下第二場圖像采集過程結束,轉到①,否則在HREF信號的電平為高期間進行有效的圖像數據采集。

?

1.3.5 采集圖像數據的預處理及存儲

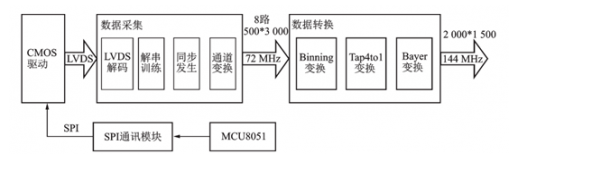

圖像壓縮系統所需要的輸入圖像數據流是按照宏場-SLICE-圖像的分層結構組織的,如圖4所示(以720X576分辨率為例)。而圖像采集系統中,A/D轉換后的輸出數據流結構如圖5所示。因此,必須對圖5所示的數據流進行相應的預處理,圖像壓縮系統才能夠直接從圖像采集系統中得到需要的數據格式,從而提高整個圖像處理系統的性能。

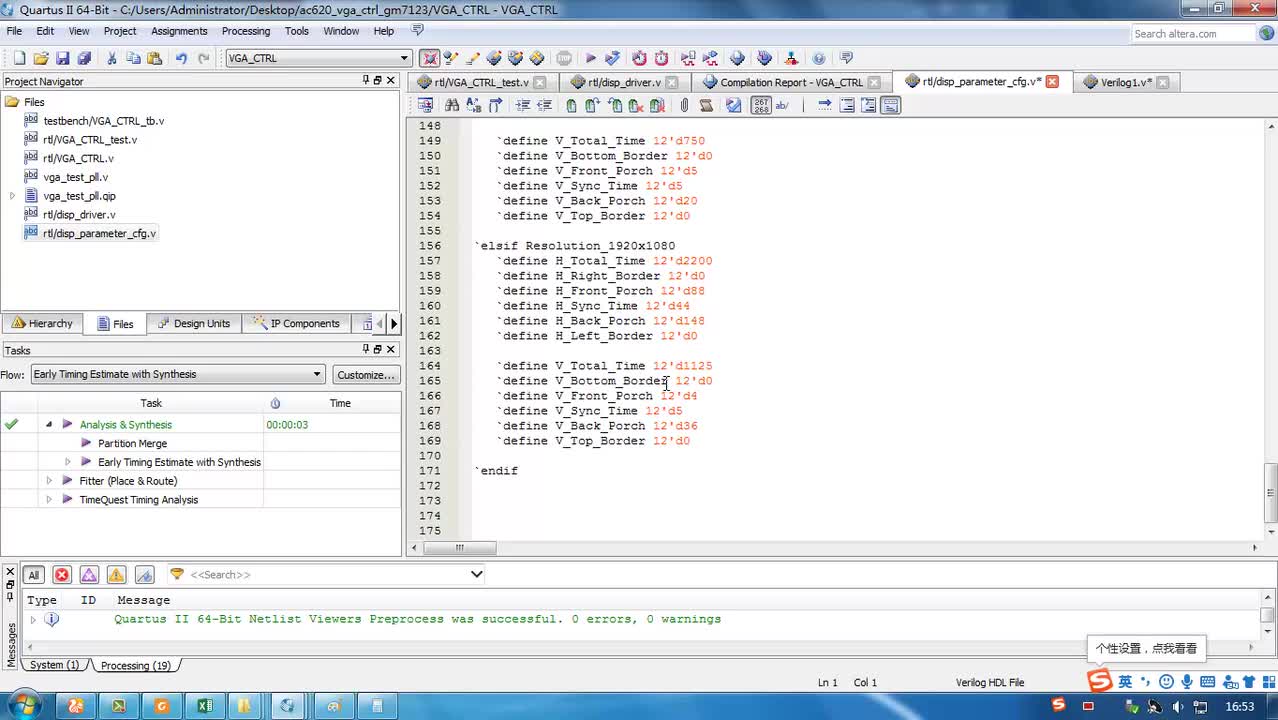

按照圖4所示的分層結構,圖像數據在幀存中以SLICE為單位順序存儲,其中SLICE的尺寸既要考慮圖像壓縮系統中圖像壓縮算法的要求,又要考慮與圖像分辨率有著密切的關系。圖6所示為圖像數據在幀存中的存儲結構。下面主要以720X576分辨率下的圖像為例討論數據存儲地址的計算。

由A/D轉換輸出數據格式與圖像壓縮系統輸入數據格式間的對應關系可知中,一幀圖像中的任意像素可以用分層尋址方式準確定位,并據此產生此像素所對應的三個分量的幀存存儲地址值。首先,從一幀圖像的一第一行開始,每連續的16行作為一個像素塊,稱為行塊,一幀720X576分辨率的圖像可劃分為36個行塊;其次,每一個行塊又在水平方向上平均分為3段,每段稱為一個列組,每個列組的寬度為水平方向上連續的240個像素,高度為垂直方向上連續的16行。720X576圖像像素分層尋址示意圖如圖7所示。Y、U、V三個分量在幀存中的存儲地址產生過程如下:首先確定含像素所屬行塊在一幀圖像中的偏移量及像素所屬列組在行塊中的像移量,即確定行塊序號和列組序號;然后確定像素在所屬列組中水平方向上和垂直方向上的偏移量;最后根據上述4個偏移量計數器的值即可產生此像素所對應的三個分量的幀存存儲地址值。

在720X576分辨率下,一幀圖像中任一像素的Y、N、V分量對應的幀存地址計算公式如下:

y_addr=(C-1)×8640+(E+1)×2880+(D-1)×120+(F-2)/2

u_addr=(C-1)×8640+(E-1)×2880+(D-1)/2)×60+(F-3)/4+1920

v_addr=(C-1)×8640+(E-1)×2880+(D-1)/2)×60+(F-4)/4+2400

式中,y_addr、u_addr、v_addr分別對應Y、U、V三個分量的幀存存儲地址;C表示行塊序號,取值范圍為1~36;D表示在列組垂直方向上的偏移量,取值范圍為1~16;E表示列組序號,取值范圍為1~3;F表示在列組中水平方向上的偏移量,取值范圍為1~240。

上述地址計算公式在FPGA中實現時,考慮到各乘積項常系數(8640、2880等)所對應的二進制數中"1"較少,可將各乘積運算轉化為移位與加法運算的組合,并將加法操作用分組超前進位[4]方式實現。

?

1.3.6 幀存乒乓刷新控制機制

兩組幀存的讀寫過乒乓機制來管理。為確保在任何時刻,最多只有一個幀存處于圖像壓縮系統的控制下,設置了一個讀互斥鎖;同樣,最多有一個幀存可接收預處理后的數據,因此又設置了一個寫互斥鎖。

因為圖像壓縮系統的壓縮幀率在720×576分辨率下小于25幀/秒,為了保證圖像壓縮系統每次從采集系統所到的一幀圖像數據是最近由FPGA預處理過的,使得圖像延時較小,設計了雙幀存刷新機制[5]。

在系統初始狀態,幀存A處于等待寫狀態,幀存B處于讀結束狀態。采集過程開始,兩個幀存的狀態轉換控制流程完全相同。下邊以幀存A為例介紹基于讀寫互斥鎖的幀存控制機制。幀存乒乓刷新控制機制如圖8所示,其設計思想如下:

①采集過程未開始,幀存A處于等待寫狀態,并獲得寫互斥鎖;

②收到一幀新圖像的開始信號,采集過程開始,幀存A進入可寫狀態,接收圖像數據;

③一幀圖像的采集過程結束后,幀存A進入寫結束狀態,并釋放寫互斥鎖;

④在寫結束狀態下,若此時幀存B擁有讀互斥鎖,由幀存A保持寫結束狀態,否則幀存A獲得讀互斥鎖,進入讀等待狀態,并在下一個控制周期切換到再次讀等待狀態;

⑤幀存A在再次讀等待狀態下,如果幀存B處于寫結束狀態,則幀存A釋放讀互斥鎖,進入讀結束狀態,否則若圖像壓縮系統請求幀存的控制權,則幀存A進入可讀狀態,并處于圖像壓縮系統的控制下,若以上兩個條件均不滿足,則幀存A保持再次讀等待狀態。

⑥在可讀狀態下,若圖像壓縮系統請求FPGA回收幀存控制權,則幀存A進入讀結束狀態,并釋放讀互斥鎖;

⑦在讀結束狀態下,若幀存B擁有寫互斥鎖,由幀存A保持讀結束狀態,否則幀存A進入等待寫狀態,并獲得寫互斥鎖。

?

2 FPGA邏輯設計中的常見問題討論

在FPGA內部,由于LLC2時鐘驅動的邏輯非常多,布線尋徑優化的選擇余地小,從而導致它到達每個邏輯模塊驅動端的時間有一定的差異。在極端情況下這一差異(Skew)會非常大,并導致邏輯執行時的時序錯誤。因此在基于FPGA進行邏輯設計時,盡管各邏輯模塊及模塊間的通信信號基本上都是由LLC2驅動的,但模塊間的通信信號與通信的接收方模塊應視為異步,并按異步邏輯的思路實現模塊間的通信機制[6~7]。

另外本設計中LLC2的時鐘頻率達13.5MHz,且FPGA內部邏輯資源的使用率已經超過了70%。為了確保控制邏輯在FPGA中的穩定運行,需要對設計進行精心的時序仿真,提高仿真程序的測試覆蓋率,并對實現(Implementation)過程中生成的靜態時序分析報告仔細研究,確定設計中的時序關鍵路徑,采用先修改設計、分割關鍵路徑,后加限制條件的方式,盡量減少關鍵路徑的個數、降低關鍵路徑的延時。 在對設計進行仿真驗證的過程中,要盡量將所發現毛刺的發生條件找出,并用修改源設計的方法將其去除。

?

3 實驗結果

為了驗證圖像采集系統的作用,進行了對比實驗,實驗結果如表1所示。

在兩種分辨率下,經過圖像采集系統的預處理,圖像壓縮系統的幀率有不同程度的提高,尤其是在720×576分辨率下,幀率的提高超過了60%。這主要是由于圖像采集系統預處理機制的采用,使得圖像壓縮系統能夠與圖像采集系統并行工作,在很大程度上減少了圖像壓縮系統的等待執行時間,從而提高了圖像壓縮系統的壓縮幀率。從表1中可以看到,在352×288分辨率下,整個系統的性能提高不大(甚至沒有變化)。這是因為在此分辨率下,圖像數據量較小,僅靠圖像壓縮系統的處理能力即可達到實時效果,所以圖像采集系統預處理機制的采用無法進一步提高整個系統的性能。

當然,本采集系統還存在改進的余地[8],具體來說有以下兩點:

①基于FPGA實現的圖像預處理操作若具有圖像增強、去噪等功能,并對圖像的場景變換進行一定的處理,會使圖像采集系統的輸出圖像質量得到很大的提高。 ②幀存乒乓刷新機制在實用中還有一定的局限性,圖像的主以遲效果不是很理想,而且有時會使圖像壓縮系統的讀數據請求不能立即得到響應。考慮到系統的性價比,如果用一片高密度的SDRAM作為存儲器,并且將它在物理上分為三個幀存,通過這三個幀存之間的乒乓機制,相信采集系統所輸出的圖像在主觀效果上會于本文所采用的雙幀存結構。

表1 圖像采集系統對圖像處理系統的性能影響

| 圖像分辨率 |

720×576 |

352×288 | ||||

| 采集系統預處理 |

有 |

無 |

提高百分比 |

有 |

無 |

提高百比 |

| 灰度圖像壓縮幀率(幀/秒) | 13 | 8 | 62.5% | 25 | 25 | 0% |

| 彩色圖像壓縮幀率(幀/秒) | 10 | 6 | 66.7% | 25 | 22 | 12% |

電子發燒友App

電子發燒友App

評論