設計背景: 二進制轉十進制在設計應用中十分的廣泛。尤其在AD轉化中是必須所用到的一個小知識點,學習二進制轉十進制的方法顯的非常的重要。今天就和筆者來學習二進制轉十進制的方法,通過簡單的學習來掌握這么

2018-09-20 09:38:39 15588

15588

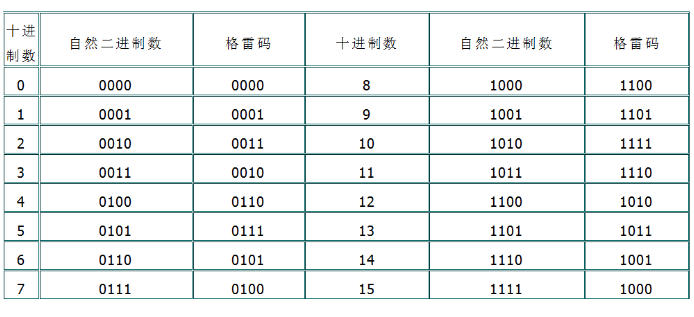

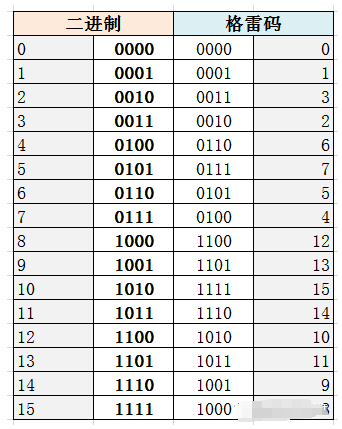

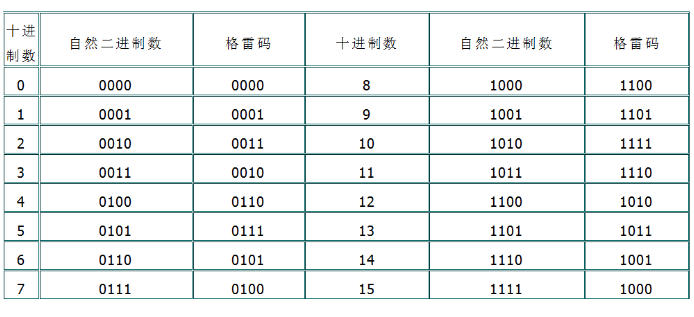

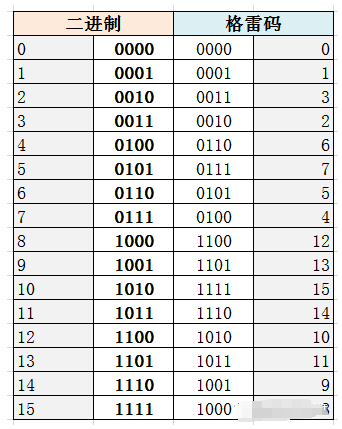

其中采用循環二進制編碼的絕對式編碼器,其輸出信號是一種數字排序,不是權重碼,每一位沒有確定的大小,不能直接進行比較大小和算術運算,也不能直接轉換成其他信號,要經過一次碼變換,變成自然二進制碼。

2020-09-23 16:23:04 6149

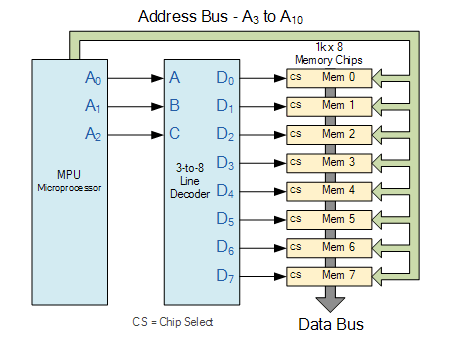

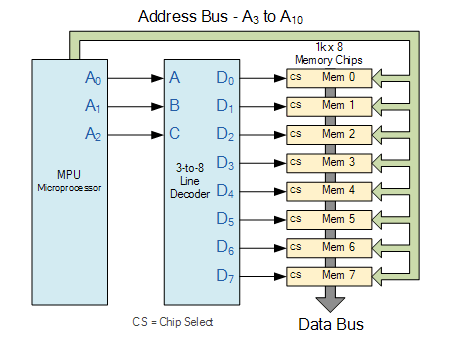

6149 二進制解碼器是由單獨的邏輯門構成的另一種組合邏輯電路,與編碼器完全相反。名稱“解碼器”是指將編碼信息從一種格式轉換或解碼為另一種格式,因此二進制解碼器使用2 n個輸出將“ n”個二進制輸入信號轉換

2020-12-29 12:10:32 8355

8355

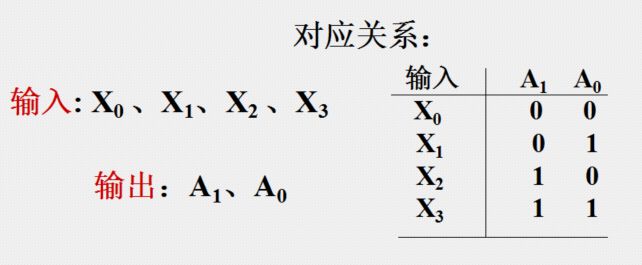

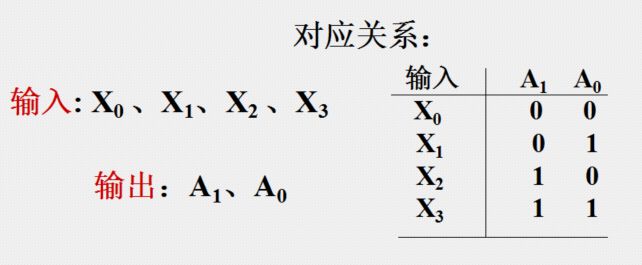

的邏輯電路稱為編碼器。編碼器有若干個輸入,在某一時刻只有一個輸入信號被轉換成為二進制碼。如果一個編碼器有N個輸入端和n個輸出端,則輸出端與輸入端之間應滿足關系N≤2n。例如8線—3線編碼器和10線—4線編碼器分別有8輸入、3位二進制碼輸出和10輸入、4位二進制碼輸出。

2023-10-27 09:29:49 2051

2051

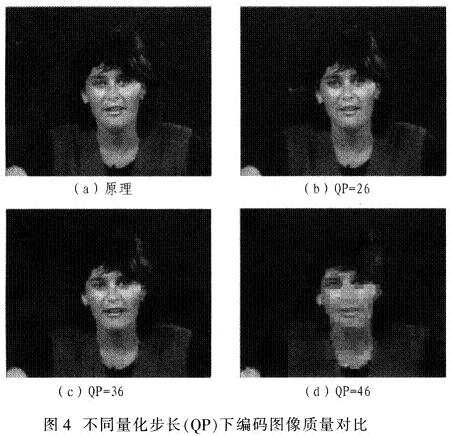

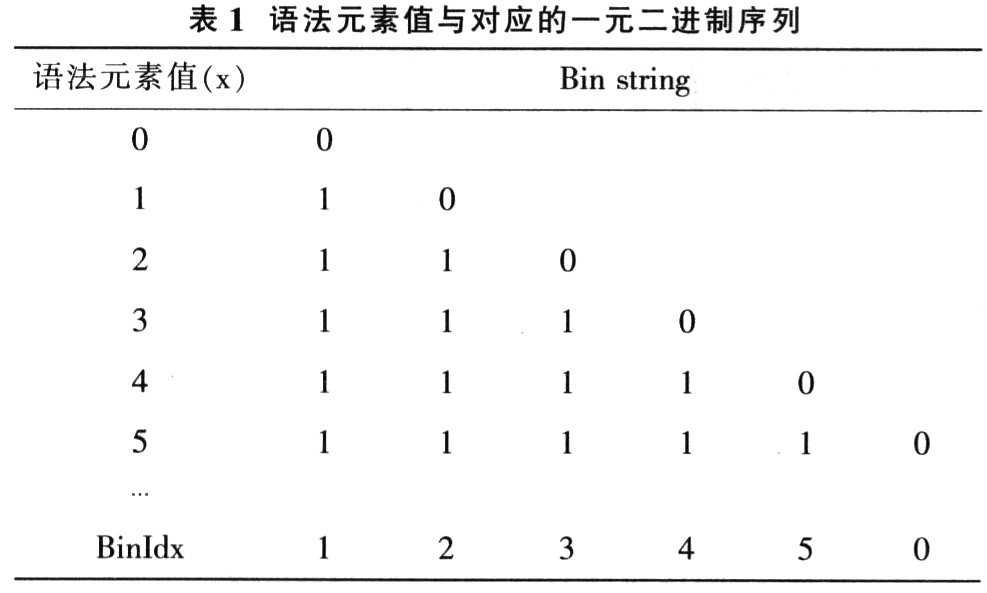

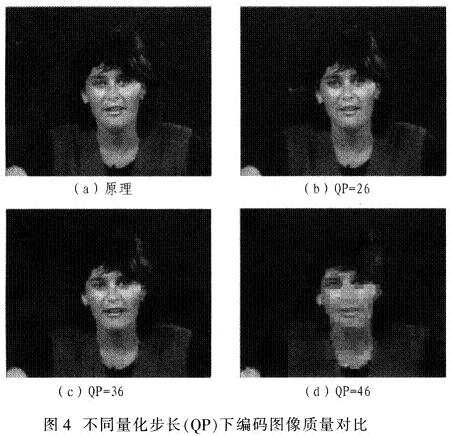

2003年發布的H.264視頻壓縮編碼標準在一定程度上解決了要在盡可能低的碼率下獲得盡可能好的圖像質量這一問題。在相同的重建圖像質量下,H.264能夠比H.263節約50%左右的比特率。此外

2020-03-05 07:05:07

H.264編碼器流程圖說明:1.參考代碼版本為jm61.流程圖中有些地方直接引用已經修改過的代碼,未作說明.2.代碼經過刪減,但是整個流程沒有變化. 看該流程圖時可能用得到的約束

2008-06-25 11:43:55

物體的形狀,于是,在每個宏塊中可包含有1、2、4、8或16個運動矢量。 多參數幀估計 在H.264中,可采用多個參數幀的運動估計,即在編碼器的緩存中存有多個剛剛編碼好的參數幀,編碼器從其中選擇一個給出

2008-06-04 14:29:02

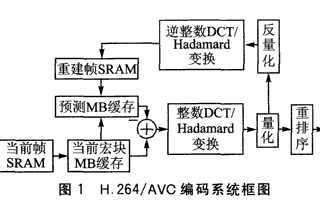

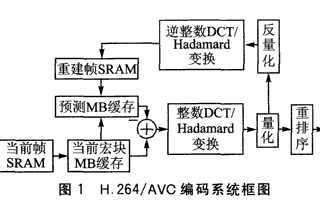

減小算法的存儲器需求,減少中間結果的存儲需求,可縮減片外存儲器訪問次數,提高應用的實時性能。下面主要討論降低H.264 INTRA幀編碼的運算復雜性和存儲器需求的方法。圖1 H.264編碼器的結構流程圖 圖2

2019-08-06 06:37:38

各位大神有做過H.264 CABAC Verilog HDL實現的嗎?小弟急求源代碼,希望做過的大嬸們給予指導,定重重酬謝@@

2015-01-14 14:13:25

×2160)和8K(8192×4320)超高清視頻。可以說,H.265標準讓網絡視頻跟上了顯示屏“高分辨率化”的腳步。 H.264 H.264,同時也是MPEG-4第十部分,是由ITU-T視頻編碼

2020-12-11 15:45:33

什么是編碼技術?H.264編碼技術在視頻會議中的應用是什么?

2021-06-02 06:17:58

h.264協議中文版下載 訪問單元:AC變換系數:自適應二進制算術解碼過程:自適應二進制算術編碼過程...中英文版,直接翻譯的。。還能讓你學習學習英語。。。不錯哦。。。。下了記得頂一頂了

2008-05-30 17:48:51

。而絕對式編碼器是直接輸出數字量的傳感器,它是利用自然二進制或循環二進制(格雷碼)方式進行光電轉換的,編碼的設計一般是采用自然二進制碼、循環二進制碼、二進制補碼等。特點是不要計數器,在轉軸的任意位置

2011-03-08 14:16:59

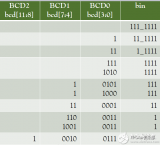

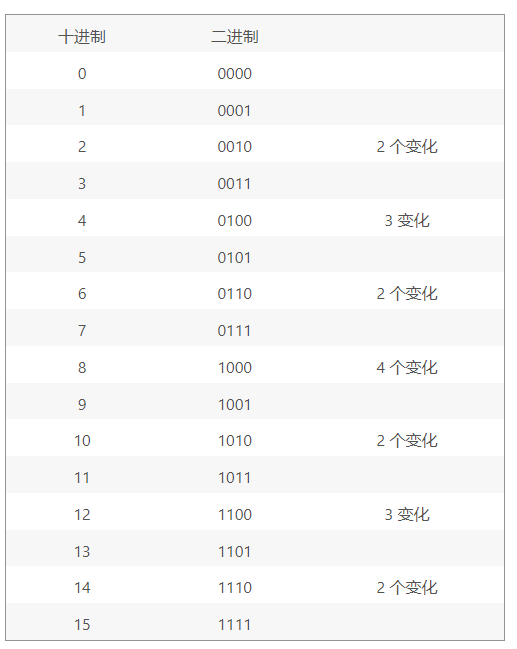

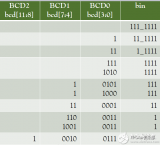

Binary-Coded-Decimal,二進制編碼的十進制碼。 這種編碼僅僅使用4位二進制數來表示十進制數中的0~9十個數碼。二進制數碼每位的值稱為權或位權。 其中b0位的權為20=1,b1位

2009-04-06 23:55:36

在LabVIEW中,如何實現一個十六進制的數取反后加1,如FFFFFFCB表示為二進制是11111111111111111111111111001011,取反后

2014-03-15 00:32:43

實現兩個二進制除法運算,并在八個七段數碼管上進行顯示實現兩個二進制除法運算,并在八個七段數碼管上進行顯示實現兩個二進制除法運算,并在八個七段數碼管上進行顯示

2013-11-01 20:34:01

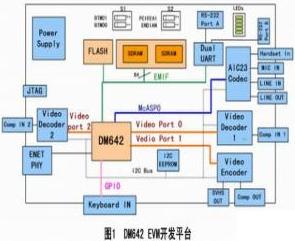

編碼器的實現 H.264視頻編碼器的實現有多種方法,不過大部分都是進行移植、優化的操作。H.264代碼要在DSP的軟件平臺CCS環境下運行,需要注意幾個問題:如配置文件、庫文件的改動、數據類型

2011-08-10 14:54:09

小妹在做一個心電信號發生器 其中從ACCESS數據庫中需要讀一個WaveData.data 的長二進制數據 這是心電圖波形的數據 每個圖500個點每個點2字節。怎么才能讀出這個長二進制數據?用變體么?

2014-10-26 20:51:14

`各位大神,我想把一張圖片通過變成二進制通過TCP傳輸,現在我把圖片轉換成二進制文件,但文件只有1KB大小。我想讀取但是不知道二進制的圖片數據類型。能否幫我畫一個簡易的讀取二進制圖片的程序,謝謝`

2017-12-29 09:26:42

SUNNISKY ENC264HD是一款實用的、且符合H.264標準的ASI-TS IP實時視頻/音頻的高清HD壓縮編碼或轉碼設備,其功能是將一路模擬視音頻(或Y/PB/PR)輸入的信號/或數字

2011-03-06 19:27:12

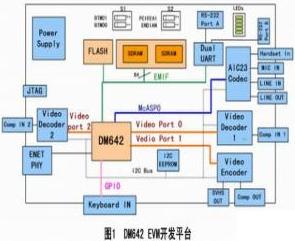

/davinciedu.html成都宇鴻科技是一家在TI DAVINCI 平臺專注3G和視頻編解碼算法優化和實現的公司,是國內少數能整體提供嵌入式3G, H.264超低碼率編碼器,基于VPN的視頻聯網傳輸平臺的公司之一

2009-12-02 14:10:03

每一個元素都是復數,類似這樣的-59.4184087630243-2.62712122987465i。 小弟想實現這個Levinsondurbin的功能仿真,首先把向量實部虛部給導入,該怎么操作這樣的浮點數變成有符號的二進制表示呢。

2020-07-21 16:10:48

用verilog實現變量flag為1表示變量a的數值中二進制1的個數是奇數,flag為0表示變量a的數值中二進制1的個數是偶數,比如:a為8’b1111_0000,則二進制1的個數為4,即偶數

2023-08-15 10:42:24

的設計中會經常遇到。轉換原理對于一個8位二進制碼,其在十進制編碼方式下的值為:把上式寫出套乘的形式:式中的每項乘2,相當于將寄存器中的二進制碼左移1位,這就意味著利用移位寄存器可以完成二進制

2017-01-09 14:38:01

文件名 -coding 7 -t 2 -w 320 -h 240其中-t 2是表示進行編碼動作。這是編譯好的二進制文件,可以直接push進系統測試。你猜對了,這個文件也一樣具有之前帖子提到的裸碼流解碼功能。

2015-02-10 18:02:25

在LABVIEW中使用二進制讀寫節點時,遇到一個奇怪的問題,當我通過新建文件創建二進制文件(見第一張圖),之后將數據寫入到二進制文件中(見第二張圖),最后讀取二進制文件(見第三張圖)。現在問題是當我

2017-09-30 15:03:01

,其余的用0代替,最后得到的二進制數為10011011。 需要指出的是,多數計算機或數字系統中只處理4、8、16、32位的二進制數據,因此,數據的位數需配成規格化的位數,如例題1.3.3種轉換結果為

2009-04-06 23:54:14

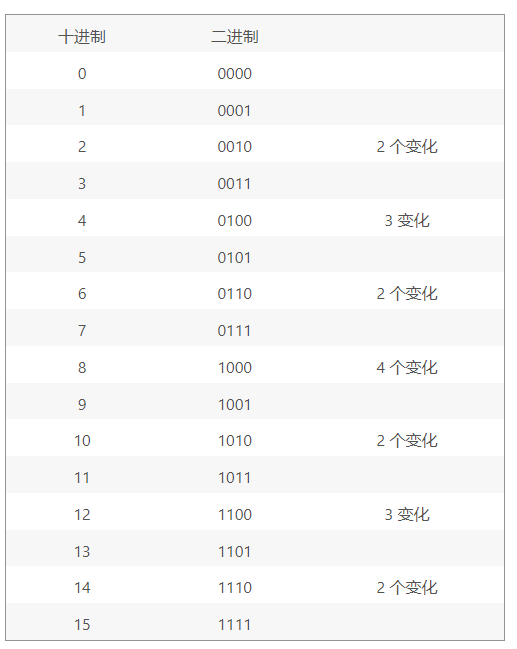

字邏輯設計課程中,我們已經學過了BCD碼的相關知識,它用4位二進制數來表示1位十進制數中的09,是二進制編碼的十進制代碼,常見的BCD碼有8421BCD碼,2421BCD碼,5421BCD碼,余3碼以及格雷

2022-07-12 16:41:42

制。遞歸算法,如 IIR 濾波、MPEG 1/2/4 中的變長編碼(VLC)、上下文自適應變長編碼(CAVLC),以及 H.264/AVC 中的上下文自適應二進制算術編碼(CABAC),當映射到這些可編程

2008-06-25 11:33:26

,有時候需要將輸入的數據信息變換為某種特定的編碼輸出,編碼器便是實現這一編碼功能的邏輯電路。編碼器的邏輯功能是將輸入的高低電平信號轉換為二進制編碼輸出,通常是將多比特的輸入數據轉換為少比特的二進制編碼

2022-08-04 17:39:32

在C語言中二進制表示是0bxxx開頭的,

為什么給寄存器賦值GpioCtrlRegs.GPAMUX2.bit.GPIO16??=?0b00;? 會出錯??

2018-05-14 07:02:41

創建前面板,該前面板有8個led指示器和一個8位無符號十進制整數的垂直滑動條控件。顯示滑動條帶有數字指示器,確保led均勻分布并且排列在底部。要求實現8個led的亮滅狀態與滑動條中的十進數的數字的二進制相對應。(即十進制向二進制轉換)

2015-09-19 10:06:39

平臺總體框架圖 圖3 H.264編碼模塊圖 2 H.264編碼器的優化 2.1 總體優化 [td] 總體優化主要包括兩部分內容:程序模塊化的設計及數據結構的設計。 程序模塊化設計時,既要考慮

2011-07-13 17:12:01

一個8位二進制數經過二進制LDPC編碼器編碼后等到一個幾位二進制的數,怎么計算的?

2017-03-14 13:07:56

系統的硬件結構 視頻編碼器的硬件結構如圖1所示。從攝像頭輸出的原始視頻流通過USB接口進入PXA255芯片進行h.264壓縮,壓縮后的碼流由網口(ETHERNET)傳到主機進行顯示,Flash中燒寫了

2011-08-24 08:59:17

應用程序 : 示例代碼演示了如何丟棄函數的二進制代碼, 然后填入 SRAM 的二進制代碼, 然后調用它 。

BSP版本:M451系列BSP V3.01.001

硬件: 任何 M451 系列板塊

2023-08-23 06:34:10

我想制作一個以8個LED的形式實現二進制計數器。該計數器通過USART發送一個8位二進制數,并讓8個LED顯示數字(如果位為0,則指示燈熄滅,當位為1時指示燈亮)。這樣做的最佳方法是什么?

2018-10-08 14:07:42

。如何判斷接收到的數據是二進制的0還是二進制的1?電路原理圖:源碼下載鏈接:工程項目結構如下圖所示:其中畫紅色方框部分為重要函數來進行講解DHT11.c#include "DHT11/DHT11.h"#include "DELAY/Delay.h"/**

2022-02-22 06:24:51

什么是H.264視頻編碼技術?如何去實現并優化一種H.264視頻編碼器?

2021-06-03 07:00:52

在Nios II中,我們可以通過Nios II 中的flash燒寫功能往FPGA中固化程序和系統參數,如果我們想單獨燒寫系統參數呢?就是想在flash或者EPCS的空閑區域寫入二進制數據。在軟件

2012-03-08 15:33:17

二進制運算規則二進制的運算算術運算二進制的加法:0+0=0,0+1=1 ,1+0=1, 1+1=10(向高位進位);二進制的減法:0-0=0,10-1=1(向高位借位) 1-0=1,1-1=0 (模

2019-12-11 17:49:02

在DSP平臺上進行視頻產品開發有什么優勢?怎么實現基于ADSP-BF561的H.264編碼器設計?

2021-06-07 06:46:01

我正在使用Labview來控制網絡分析儀E5072A。我想從VISA輸出中獲取二進制數據,而不是默認的字符串格式。在這種情況下,我想速度會更快,因為我們直接獲得機器語言,因此CPU不需要

2019-01-07 15:49:29

足H.264標準的編解碼運算速度要求。因此,在穩定的媒體處理器平臺上實現H.264標準有著較好的工程意義和應用前景。

2019-09-04 06:19:09

一種基于NiosII的低碼率實時H.264視頻編碼器設計

2021-06-07 07:06:49

增加了NAL層,負責將編碼器的輸出碼流適配到各種類型的網絡中,從而提供了友好的網絡接口。H.264之所以能夠達到以上性能,是因為采用了以下一些先進的技術:首先是幀內預測編碼,充分利用圖像空域相關性,來降低

2008-06-25 10:35:31

最新視頻編碼標準H.264及其核心技術H.264是ITU-T和ISO聯合研究制定的編碼效率高、網絡適應性強的最新數字視頻編碼國際標準.H.264是面向視頻電話、視頻會議等實際應用的標準,它能以低

2008-06-25 11:42:03

用FPGA 怎么實現BCD碼轉換成二進制啊!新手求指教PCB打樣找華強 http://www.hqpcb.com 樣板2天出貨

2013-03-15 12:00:01

、8或16個運動矢量。 多參數幀估計 在H.264中,可采用多個參數幀的運動估計,即在編碼器的緩存中存有多個剛剛編碼好的參數幀,編碼器從其中選擇一個給出更好的編碼效果的作為參數幀,并指出是哪個幀被

2008-05-28 16:28:11

量化的功能有哪些?量化的算法是什么?怎樣用Verilog語言實現H.264的量化?如何運用Modelsim對H.264進行仿真?

2021-04-28 06:12:51

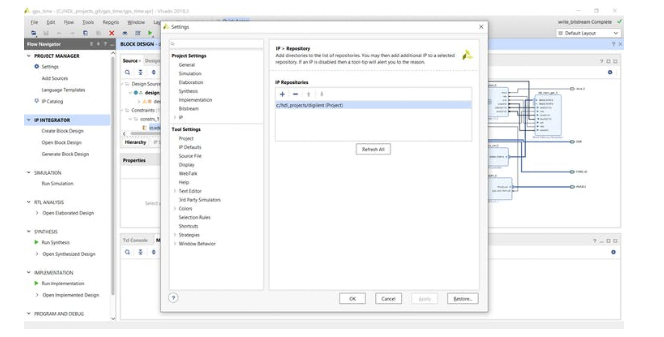

請問在FPGA上如何去實現H.264/AVC視頻編碼標準?

2021-05-07 07:27:02

H.263和MPEG一4可以節省20%~50%的碼率。就其基本檔次而言,編碼器的復雜度是H.263的10倍左右。H.264良好的網絡親和性和優異的壓縮性能使其成為視頻應用的首選,但其巨大的運算量

2019-07-29 06:52:57

針對硬件實現的H.264視頻編碼算法改進,不看肯定后悔

2021-06-04 06:25:51

Changes for Version JM7.3 to JM 7.2h.264編碼器源代碼,帶有H.264編碼器流程圖。Bug fixes- encoder: DPB for field

2008-06-25 11:46:18 164

164 H.264三大開源編碼器之評測報告Peter Lee 2005.6.19 Outline1、三大開源編碼器介紹2、實驗條件3、實驗結果4、實驗結論plus:增加t264 high quality mode的實驗結果note: 新

2008-08-25 13:07:10 51

51 闡述H.264/AVC 二進制算術編碼的原理,論述此編碼的IP 核設計方案及其FPGA 驗證。整個設計使用VerilogHDL 語言描述,在 ALDEC 的Active_HDL6.2 平臺上進行時序仿真,在 Synplicity 的Synplify7.0平

2009-09-03 09:11:20 25

25 設計并實現了基于DSP 芯片TMS320DM642 的H.264 編碼器。詳細介紹了H.264 算法在DSP上的移植和優化。為使編碼器達到實時應用的要求,采用基于C64x CPU 的軟件優化技術,對H.264的一些核

2009-09-03 14:30:34 23

23 H.264 實時編碼器的研究和實現是目前視頻通信研究領域的一個熱點問題,本文介紹了基于TMS320DM642 平臺的H.264 編碼器的優化,重點介紹了基于DM642 的整數DCT 變換、量化和匹配

2009-12-18 12:13:37 19

19 為了在改進的H.264 上實現無再損幀內編碼,該文提出了一種新的基于整數線性規劃的優化clip 算法及改進算法,解決了H.264 多次編碼中由當前clip 模塊和幀內預測運算引入的視頻畸

2010-02-09 14:28:11 35

35 基于ADSP-BF561的H.264視頻編碼器的實現

H.264/AVC是ITU-T VCEG和ISO/IECMPEG聯合制定的最新視頻編碼國際標準,是目前圖像通信研究領域的熱點技術之一。H.264的視頻編碼層(VCL)

2008-12-26 14:43:44 706

706 二進制

二進制與十進制的區別在于數碼的個數和進位規律有很大的區別,顧名思義,二進制的計數規律為逢二進一,是以2為基數的計數體制。10這個數在二進

2009-04-06 23:48:01 7548

7548

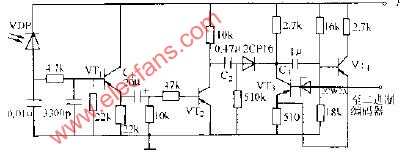

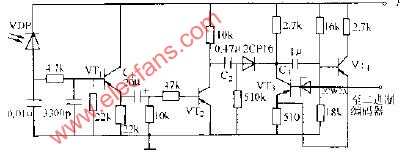

配用二進制編碼器的光控電路圖

2009-06-06 09:30:38 645

645

二進制編碼和二進制數據

二進制編碼是計算機內使用最多的碼制,它只使用兩個基本符號"0"和"1",并且通過由這兩個符號組成的

2009-10-13 16:22:51 4459

4459 基于TMS320DM6446的H.264編碼器實現與優化

1 引言

H.264是ITU-T的視頻編碼專家組(VCEG)和ISO/IEC的活動圖像專家組(MPEG)聯合制定的視頻壓縮標準。

2010-02-10 09:20:11 1311

1311

什么是二進制計數器,二進制計數器原理是什么?

計數器是數字系統中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈沖的個數,還可以實現

2010-03-08 13:16:34 30352

30352 二進制電平,什么是二進制電平

在二進制數字通信系統中,每個碼元或每個符號只能是“1”和“0”兩個狀態之一。若將每個碼元可能取的狀態增

2010-03-17 16:51:58 2255

2255 十進制數的二進制編碼

在人機交互過程中,為了既滿足系統中使用二進制數的要求,又適應人們使用十進制數的習慣

2010-05-02 19:04:06 8947

8947 Jointwave發布的H.264編碼器可實現1080p

Jointwave發布的H.264編碼器技術提供了單芯片HD和超低功耗廣播級視頻— 針對65nm處理器60mW可實現1080p。

正如在強調Jointwave的H.26

2010-01-04 08:41:20 1116

1116 摘要:在DM642 EVM平臺上實現了 H.264視頻編碼器,并從內存分配、Cache優化、代碼優化以及匯編程序級優化等幾個方面對編碼

2011-01-10 14:12:14 3202

3202

介紹了基于嵌入式平臺PXA255的h.264視頻編碼器的實現。在描述了視頻編碼器的硬件結構設計及視頻采集軟件的實現的基礎上,詳細介紹了h.264對視頻編碼標準的一些改進以及基于PXA2

2011-09-02 16:41:57 87

87 為了實現基于DSP的H.264視頻編碼器的實時性能,提出了一系列優化實現方法。首先結合TMS320DM6437硬件特點,描述了X264代碼向TMS320DM6437平臺的移植過程和優化方法,重點介紹了整數DCT變換

2012-05-22 15:10:25 63

63 基于PowerPC的H.264編碼器中斷處理程序解析

2016-01-04 15:26:58 6

6 格雷碼,又叫循環二進制碼或反射二進制碼,格雷碼是我們在工程中常會遇到的一種編碼方式,它的基本的特點就是任意兩個相鄰的代碼只有一位二進制數不同,這點在下面會詳細講解到。格雷碼的基本特點就是任意兩個相鄰的代碼只有一位二進制數不同。

2018-03-02 15:48:53 16613

16613

BCD碼亦稱二進碼十進數或二-十進制代碼。用4位二進制數來表示1位十進制數中的0~9這10個數碼。它是一種二進制的數字編碼形式,用二進制編碼的十進制代碼。BCD碼這種編碼形式利用了四個位元來儲存一個十進制的數碼,使二進制和十進制之間的轉換得以快捷的進行。

2018-03-14 10:15:42 6149

6149 目前的視頻監控行業,基于DSP的H.264編碼器解決方案占有絕對優勢的市場份額,這是由DSP方案開發周期相對較短的特性決定的。在ASIC或FPGA方案仍處于研發階段時,DSP方案已捷足先登,并較好地解決了視頻監控行業中H.264編碼器方案從無到有的過程,為H.264在監控應用中走向成熟立下了汗馬功勞。

2018-10-29 08:21:00 12470

12470 二進制解碼器是另一種由各個邏輯門構成的組合邏輯電路,與編碼器完全相反。

2019-06-22 09:41:36 8521

8521

目前高清H.264 攝像機的核心SoC基本上都是ASIC,而FPGA作為近年來發展迅速的可編程器件,在高清H.264 攝像機的SoC領域如何能有一席之地?這是我們的設計需要實現的目標。

2020-07-27 10:50:01 12

12 二進制解碼器是由單獨的邏輯門構成的另一種組合邏輯電路,與編碼器完全相反。名稱“解碼器”是指將編碼信息從一種格式轉換或解碼為另一種格式,因此二進制解碼器使用2 n個輸出將“ n”個二進制輸入信號轉換為等效代碼。

2021-01-03 17:42:00 5675

5675

根據H.264/AVC編碼器原理及結構,同時考慮到現有硬件資源的限制以及該設計的應用需求,設計了圖1所示的H.264/AVC編碼系統結構。

2021-03-16 14:12:54 2117

2117

基于FPGA的二進制相移鍵控設計方案

2021-05-28 09:36:50 11

11 絕對編碼器中的傳感器輸出格雷碼序列,需要一些復雜的轉換方法才能正確使用。本文展示了如何獲取絕對編碼器使用的格雷碼并將其轉換為二進制。

2022-05-05 15:41:49 5409

5409

本方案是一個基于FPGA的二進制時鐘,使用GPS作為時間參考。

2022-05-13 17:41:31 1786

1786

將二進制數視為元胞自動機可能有助于數字二進制計數器的設計和實現嗎?

2022-07-28 11:47:10 1181

1181

格雷碼是一種循環二進制編碼,特點是相鄰數變化時只有一位數據跳變。

2023-01-17 11:15:17 3292

3292

將信息(如數和字符等)轉換成符合一定規則的二進制代碼。

2023-03-21 11:55:48 7723

7723

二進制最佳接收原理 二進制最佳接收機的實現形式有哪兩種? 二進制最佳接收原理是計算機通信中的重要概念,它是指在二進制通信中通過一定的方法,使接收機在信號傳輸過程中能夠準確、可靠地接收到發送端傳輸

2023-11-27 16:19:07 429

429 如何實現二進制和BCD碼數據的相互轉變? 二進制碼是將十進制數字表示為二進制數和十進制數的一種表示方法。在計算機系統中,二進制數是最基本的數制表示方法,而BCD碼則是用于將數字直接轉換為二進制

2024-02-18 14:51:58 215

215

電子發燒友App

電子發燒友App

評論