0 引言

??? 可重構體系結構已經成為FPGA系統開發的研究熱點,并已有許多令人矚目的研究成果及產品應用。FPGA可重構的應用為用戶提供了方便的系統升級模式,同時也實現了基于相同硬件系統的不同工作模式功能。在當今快速發展的市場環境條件下,產品是否便于現場升級,是否便于靈活使用無疑是產品能否進入市場的關鍵因素,FPGA的可重構設計顯得尤為重要。

??? 目前,很多可重構的設計方式都采用單片機、CPLD等器件直接對FPGA器件進行編程配置,從而實現系統工作模式的可重構。本設計則通過開發CPLD先對FPGA的配置芯片EPCS進行編程配置,然后再由FPGA從EPCS配置芯片下載配置程序來實現可重構,并通過用戶界面的簡單操作來完成FPGA的工作方式重構,這種可重構方式結構簡單,配置靈活,用戶操作更加方便。本文首先介紹了FPGA常用的配置方式,然后詳細闡述了基于對EPCS配置芯片在線編程的可重構設計方案。

1 FPGA的常用配置方式

??? FPGA器件有三類常用的配置下載方式。其中主動配置方式(AS)是由FPGA器件引導配置操作過程。它控制著外部存儲器和初始化過程,可使用Altera串行配置器件來完成。期間FPGA器件處于主動地位,配置器件處于從屬地位。配置數據通過DATA0引腳送入FPGA。配置數據被同步在DCLK輸入上,1個時鐘周期傳送1位數據。

??? 被動配置方式(PS)則是由外部計算機或控制器控制配置過程。在PS配置期間,配置數據從外部儲存部件通過DATA0引腳送入FPGA。配置數據在DCLK上升沿鎖存,1個時鐘周期傳送1位數據。

??? JTAG配置方式中的JTAG接口是一個業界標準,主要用于芯片測試等功能,它使用IEEE Std1149.1聯合邊界掃描接口引腳,支持JAM STAPL標準,可以使用Altera下載電纜或主控器來完成。FPGA在正常工作時,它的配置數據存儲在SRAM中,關電后數據會消失,再次加電時必須重新下載配置程序。實驗中通常用計算機或控制器進行調試,因此,可以使用PS。而在實用系統中,多數情況下必須由FPGA主動引導配置操作過程,這時,FPGA將主動從外圍專用存儲芯片中獲得配置數據,而此芯片中的FPGA配置信息則用普通編程器將設計所得的pof格式文件燒錄進去。

??? 在做FPGA實驗板時,通常采用AS+JTAG方式,這樣可以用JTAG方式進行調試,而最后程序已經調試無誤后,再用AS模式把程序燒到配置芯片中,這樣操作有一個明顯的優點,就是在AS模式不能下載的時候,可以利用Quartus自帶的工具生成JTAG模式下可以利用的文件來驗證配置芯片是否工作正常。

2 對EPCS在線編程的FPGA可重構配置

2.1 FPGA可重構簡介

??? 可重構體系結構指能夠利用可重用的硬件資源,根據不同的應用要求,靈活改變自身的體系結構,以便為每個特定的應用需求提供與之相匹配的體系結構。可重構電路的設計可利用FPGA的可重配置特性。所謂可重配置,就是基于SRAM的FPGA在掉電后配置數據會自動丟失,再次上電后必須重新配置FPGA,FPGA才能正常工作。這樣可以利用有限的硬件資源完成多種邏輯功能,這就是采用基于SRAM工藝的FPGA的可重構系統的可重構電路設計原理。

??? 設計時,可以通過開發單片機或CPLD器件來控制FPGA配置不同的邏輯功能以實現重構系統。FPGA有一個專用的配置引腳nCONFIG,在FPGA正常工作過程中,如果此引腳上加一個低電平脈沖,那么,當FPGA檢測到其上升沿后,FPAG將自動清除其內部的配置存儲器,并進行重新配置,這樣,FPGA才能工作。利用這一特性,設計時便可通過用戶界面操作在FPGA的nCONFIG引腳上加一個低電平脈沖,隨后發送數據,從而完成對FPGA的重新配置。

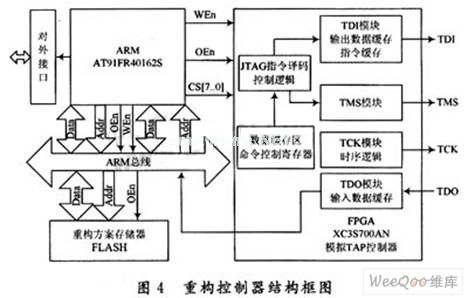

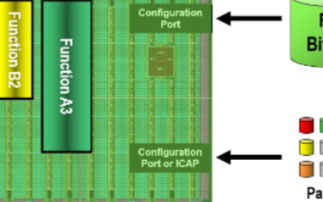

??? 本設計是通過DSP處理器來接收PC主機的FPGA配置數據流,并開發CPLD器件以實現控制邏輯,最終把所需的FPGA配置數據流存儲到支持AS配置模式的EPCS配置芯片中,并實現FPGA配置數據流的更新,從而達到FPGA的重新配置,實現整個系統的可重構。其可重構電路由DSP與CPLD串行通訊電路、CPLD讀寫EPCS配置芯片電路和EPCS配置FPGA電路組成。

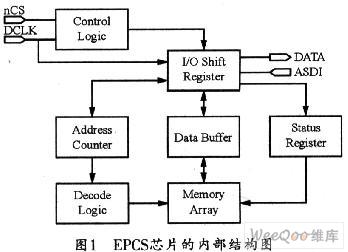

2.2 EPCS配置器件

??? FPGA的串行配置芯片主要包括EPCS1,EPCS4,EPCS16,EPCS64,EPCS128等。它們的主要區別是容量不同,分別為1 M,4 M,16 M,64 M,128 M Bits的容量,可配置的FPGA器件也有所不同,用戶可根據不同需求來選擇。EPCS配置芯片的擦除或編程次數可以達到十萬次左右,一般情況下足以滿足用戶需求。EPCS器件電平的選擇包括3.3 V、2.5 V、1.8 V、1.5 V,主要可參考對應的FPGA所用I/O bank的VCCIO引腳電平的選擇。

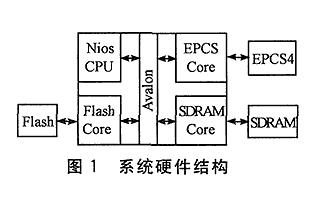

EPCS芯片的內部結構框圖如圖1所示,EPCS配置器件與所配置的FPGA器件的連接引腳有時鐘輸入管腳DCLK。可為串行數據的傳送提供時鐘,一般由FPGA發送;其次是串行數據輸出管腳DATA,用于向FPGA傳送配置數據;第三是主動串行數據輸入管腳ASDI,負責接收來自FPGA的不同字符串以實現對EPCS的讀寫控制;另外,還有片選信號nCS。

??? 上位機通過下載線用Quartus軟件工具對EPCS配置芯片進行配置程序的燒寫操作,其配置文件必須為pof文件格式。在所設計的系統文件編譯完成后,Quartus軟件就可以生成燒寫所需的pof格式文件。

2.3 可重構系統設計

??? 本設計主要是通過DSP的串口向CPLD器件發送控制命令以及要進行配置的數據包,CPLD解析命令后再執行相應的操作,以完成EPCS配置芯片所需的下載時序及配置數據。當EPCS配置芯片的數據下載完成后,再進行FPGA從配置芯片下載新的系統配置程序過程。一般情況下,在系統上電后,FPGA都要馬上從EPCS配置芯片中下載配置文件。在對EPCS配置芯片進行控制時,首先要讓FPGA釋放對EPCS配置芯片的控制,而且,在對EPCS配置芯片寫數據的操作完成后,又要將控制權交與FPGA,以便FPGA能夠下載最后一次完成的配置程序。本系統的可重構原理圖如圖2所示。

??? FPGA可重構系統中,DSP通過一個串口與CPLD進行通信,串口由數據信號線BDX、幀信號線BFSX以及時鐘信號線BCLKX組成,所有的控制命令和程序數據都是通過這三條信號來傳送的。FPGA器件的CONF_DONE信號線、nSTATUS信號線和nCONFIG信號線均需要用大小為10kΩ的電阻上拉,而nCE信號線則需用10kΩ的下拉電阻。CPLD器件通過nCONFIG信號線和nCE信號線對EPCS配置芯片的控制權進行控制或釋放。當系統上電后,CPLD器件首先對EPCS配置芯片表現為釋放狀態,而FPGA則執行EPCS配置芯片的數據讀取操作,即FPGA的配置過程是:FPGA通過nCSO管腳置EPCS配置芯片的nCS信號線為低電平,并通過ASDO管腳向EPCS發送控制命令和地址,然后在DCLK的上升沿,由配置芯片通過DATA0信號線將配置程序和數據發送到FPGA,在程序發送完畢以后,CONF_DONE由低電平變為高電平,隨后進行FPGA初始化并進入工作狀態。

??? 當需要進行系統重構時,可由上位機向DSP器件發送控制命令以進行系統的重構操作。系統重構的流程圖如圖3所示,整個過程包括以下幾個步驟:

??? (1)上位機發送重構命令后,由DSP通過串口向CPLD器件發送控制選通命令字符串,命令經CPLD器件解析后將nCONFIG信號線置為低電平,并將nCE信號線置為高電平,從而取得對EPCS配置器件的nCS、DCLK、ASDI、DATA管腳的掌控權。此時,FPGA可釋放對EPCS的掌控權,但不讀取EPCS的配置程序數據。

(2)主機通過儀器接口向DSP器件發送所需要的重構數據,并存儲在DSP器件的數據存儲區內。經實驗分析,Quartus軟件生成的pof格式文件數據并不能直接寫入EPCS配置芯片,而是需要進行一定方式的格式轉換,然后才能重新組合成需要下載到EPCS配置芯片的數據流。所以,需要在DSP內做一步數據轉換的操作。

??? (3)在對EPCS配置芯片進行數據寫入以前,先要將其內部的原有數據擦除掉。所以,這一步的任務是向EPCS配置芯片發送控制命令,并打開寫使能,隨后發送擦除命令,將EPCS原有數據擦除。要注意的是,擦除時間必須大于3 s,否則不能完成擦除操作。

??? (4)為了確認擦除操作是否已操作成功,可以執行一次讀狀態控制命令。讀狀態命令也需要先打開寫使能,再發送讀狀態命令。如果擦除過程正在進行,則DATA信號線上會返回0000 0001的數據,擦除操作完成后,DATA信號線上將返回0000 0000的數據,此時便可以進行下一步的工作。

??? (5)當確認擦除操作完成后,就可以進行EPCS配置芯片的數據寫入操作了。數據的寫入需要按幀依次寫入到對應的存儲地址,數據存儲的首地址為0000 0000。

??? (6)所需的配置數據流發送完畢后,可發送控制命令以使CPLD器件釋放對EPCS配置芯片的控制權,即置nCS、DCLK、ASDI、DATA信號線為高阻狀態,并將nCONFIG信號線由低電平置為高電平,nCE信號線置為由高電平置為低電平。一旦FPGA器件接手EPCS配置芯片的控制權,在檢測到nCONFIG信號線的上升沿后,FPGA將下載EPCS配置芯片內的數據進行重新配置,此過程與系統上電時的配置過程相同。經過上述一系列的操作,便可實現一次FP-GA的重構過程。

2.4 系統設計特點

??? 本文所述的FPGA可重構設計方案可以在系統不關電的情況下進行重構過程,這樣就不會影響系統其它部分電路正在進行的工作,極大地方便了用戶的實際應用。當一次用戶所需的配置完成后,系統下次上電后就會自動執行最后一次所重構的工作模式,不必每次上電進行重構工作。

3 可重構設計的驗證

??? 圖4所示是按照本系統設計的步驟要求,在數字化儀平臺上對可重構系統進行全面測試的部分重構波形變化圖,以此完成對主控邏輯功能的FPGA器件EP1C6Q24017的功能重構實驗驗證。

??? 圖4中所有波形圖的上面位置顯示的均為時鐘信號波形,其中圖4 (a)所示是打開EPCS配置芯片寫使能時,發送控制字的時序圖,圖中下面位置的波形為ASDO數據線上的信號,指示寫使能控制字為“06”;圖4(b)所示是讀寫使能的狀態時序圖,圖中下面位置的波形為DATA0數據線上讀取的信號,指示狀態寄存器為“02”;圖4(c)所示是對EPCS配置芯片進行擦除操作的時序圖,圖中下面位置的波形為ASDO數據線上的信號,指示擦除控制字為“C7”;圖4(d)所示是讀擦除操作的狀態時序圖,圖中下面位置的波形為DATA0數據線上讀取的信號,指示狀態寄存器為“03”;圖4(e)所示是對EPCS配置芯片進行寫數據操作的時序圖,圖中下面位置的波形為ASDO數據線上的信號,指示寫數據命令為“02”;圖4(f)所示是向EPCS配置芯片傳輸數據過程的部分波形圖,圖中下面位置為ASDO數據線上的數據信號。

??? 在滿足上述時序要求的條件下,當EPCS配置芯片的數據寫入完成后,FPGA即可進入配置文件所設計的工作模式,設計實驗結果完全符合預期的重構目標。經過反復測試,該重構方式功能正常,能穩定地完成系統所設計的不同重構工作。

4 結束語

??? 利用文本的方法對基于EPCS在線編程的FP-GA進行可重構設計,其硬件電路比較簡單,成本低,同時不需要增加太多的硬件資源(比如大容量的存儲器件等),而且配置過程靈活方便,用戶只需要一個相應的配置文件數據包,即可完成系統重構功能。故此,這種FPGA的可重構設計具備廣泛的應用前景。

電子發燒友App

電子發燒友App

評論