PAD在接收機(jī)動(dòng)態(tài)可重構(gòu)結(jié)構(gòu)中的應(yīng)用設(shè)計(jì)

可重構(gòu)結(jié)構(gòu)是一種可以根據(jù)具體運(yùn)算情況重組自身資源,實(shí)現(xiàn)硬件結(jié)構(gòu)自身優(yōu)化、自我生成的計(jì)算技術(shù)。動(dòng)態(tài)可重構(gòu)技術(shù)可快速實(shí)現(xiàn)器件的邏輯重建,它的出現(xiàn)為處理大規(guī)模計(jì)算問題提供了一種兼具通用處理器靈活性和ASIC電路高速性的解決方案。在筆者所從事的系統(tǒng)設(shè)計(jì)中,當(dāng)模擬器件的一些性能改變但又不能及時(shí)更新調(diào)整后端的數(shù)字基帶處理時(shí),比如濾波器由于工作時(shí)間過長引起的溫漂特性所帶來的影響,此時(shí)就可以用可編程模擬器件替代一部分前端固定模擬器件,進(jìn)而可以實(shí)時(shí)的對(duì)FPGA模塊進(jìn)行動(dòng)態(tài)可重構(gòu)操作,最終達(dá)到系統(tǒng)性能的最優(yōu)化。

可編程模擬器件

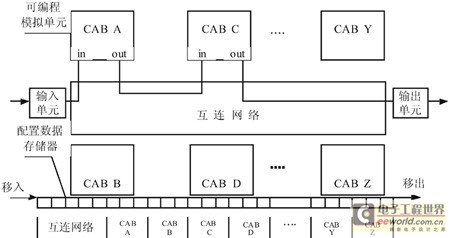

可編程模擬器件是近年來嶄露頭角的一類新型集成電路。它屬于模擬集成電路,即電路的輸入、輸出甚至內(nèi)部狀態(tài)均為隨時(shí)間連續(xù)變化且幅值未經(jīng)過量化的模擬信號(hào);同時(shí),該類器件又是現(xiàn)場可編程的,即可由用戶通過改變器件的配置來獲得所需的電路功能。為支持上述可編程能力,可編程模擬器件需以可編程模擬單元(CAB)和可編程互連網(wǎng)絡(luò)(PIN)為核心,配合配置數(shù)據(jù)存儲(chǔ)器、輸入單元、輸出單元或輸入\輸出單元等共同構(gòu)成[1](見圖1)。

圖1 可編程模擬器件組成框圖

多數(shù)可編程模擬器件在單一的+5V電源電壓下工作,額定功耗為100mW量級(jí)。由于采取了特殊的措施,其輸入、輸出線性范圍通常可達(dá)到接近滿電源電壓量程;閉環(huán)帶寬已達(dá)到數(shù)百千赫到數(shù)十兆赫;頻率失真度、共模抑制比、內(nèi)部噪聲等指標(biāo)也已達(dá)到中、高精度運(yùn)算放大器的水平。

盡管模擬信號(hào)處理的精度低于數(shù)字信號(hào)處理方式,但仍能滿足許多重要應(yīng)用對(duì)計(jì)算精度的要求,而所需的電路規(guī)模較小,成本也較低。同時(shí)利用其可編程特性,還可以實(shí)現(xiàn)精確的自動(dòng)調(diào)諧和自動(dòng)增益控制,顯著提高通信系統(tǒng)的抗干擾能力。

相位檢測器的實(shí)現(xiàn)

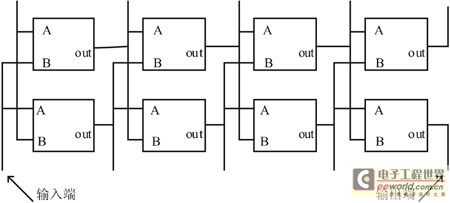

TRAC(完全可重配置模擬電路)是英國FAS公司的現(xiàn)場可編程模擬器件系列產(chǎn)品的總稱。它提供了一條從信號(hào)處理問題出發(fā),可解決各種常見的信號(hào)處理問題。器件參考模擬計(jì)算機(jī)的運(yùn)算單元并加以擴(kuò)充,使器件內(nèi)部的每個(gè)可編程模擬單元均具備加、減、取負(fù)、對(duì)數(shù)、反對(duì)數(shù)、積分、微分等8種運(yùn)算功能,因此只需選定運(yùn)算的類型和給出必要的參數(shù),便可以很方便地完成對(duì)有關(guān)單元的設(shè)計(jì),根本無須考慮單元電路的內(nèi)部結(jié)構(gòu)等具體細(xì)節(jié)。其內(nèi)部各單元之間采取自左向右固定連接的形式,所有單元的輸入\輸出端均引出至器件引腳上,并且允許利用各單元均具備的“直通”和“關(guān)斷”功能或者利用外接的“短路線”來修改這種基本連接[1](見圖2)。

圖2 TRAC器件結(jié)構(gòu)示意圖

在筆者所從事的認(rèn)知無線電硬件平臺(tái)設(shè)計(jì)中,由于需要從強(qiáng)信號(hào)背景環(huán)境中識(shí)別提取出微弱的信號(hào),因而可利用TRAC器件構(gòu)成相敏檢測器,并將其作為鎖存放大器的一部分。要實(shí)現(xiàn)這一目標(biāo),需要電路像窄帶濾波器那樣工作,除去大部分不希望要的強(qiáng)信號(hào)而僅允許待測的微弱信號(hào)通過。

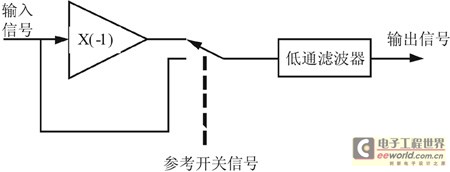

圖3所示為相位檢測器的基本框圖。輸入信號(hào)和參考開關(guān)信號(hào)具有相同的頻率和相位。從所示的開關(guān)輸出中可望得到一個(gè)全波整流信號(hào),而且經(jīng)過低通濾波器后,便可得到和交流信號(hào)電位成比例的直流電壓輸出。在實(shí)際應(yīng)用中,輸入信號(hào)可能非常小,因此還需要加入前置放大級(jí)以支持精確的檢測。因?yàn)橥ǔP枰谝欢ǖ姆秶鷥?nèi)連續(xù)改變參考信號(hào)的頻率,同時(shí)測量相應(yīng)的直流輸出。同樣,若需要檢測某個(gè)單一頻率,則參考信號(hào)必須與待測輸入信號(hào)頻率相同。由于相位檢測器也對(duì)相位敏感,因此當(dāng)兩個(gè)信號(hào)相位相同時(shí)會(huì)得到最大的輸出電壓。

圖3 相位檢測器框圖

相位檢測器和低通濾波器一樣需要利用兩片TRAC器件來實(shí)現(xiàn)。而外部元件對(duì)于放大器和濾波器都是必不可少的,所以必須對(duì)滿足條件的元件進(jìn)行合理取值。

可編程ADC的實(shí)現(xiàn)

認(rèn)知無線電接收機(jī)對(duì)其前端采用的高性能模-數(shù)轉(zhuǎn)換器(ADC)及模擬器件的要求都較高,而FPGA在基帶數(shù)字信號(hào)處理方面又迫切需要?jiǎng)討B(tài)可重配置。為了適應(yīng)以上要求,可以首先考慮使用可編程模擬器件來實(shí)現(xiàn)ADC,以下是兩種具體實(shí)現(xiàn)方法。

FIPSOC混合信號(hào)片上系統(tǒng)

SIDSA公司的FIPSOC混合信號(hào)片上系統(tǒng)是快速開發(fā)模擬、數(shù)字集成應(yīng)用的理想工具。FIPSOC芯片包括內(nèi)嵌的增強(qiáng)型8051微處理器、現(xiàn)場可編程門陣列(FPGA)以及一組面向信號(hào)調(diào)理和數(shù)據(jù)采集應(yīng)用的可靈活配置的模擬單元。與分離的模擬、數(shù)字FPGA方案相比,采用FIPSOC混合信號(hào)片上系統(tǒng),可使產(chǎn)品設(shè)計(jì)周期縮短30~40%。

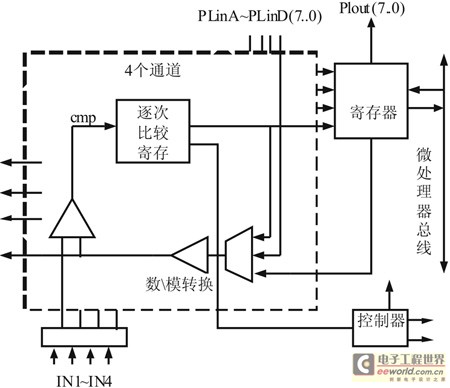

可編程的模擬、數(shù)字單元與8051的單片系統(tǒng)包括模擬單元、轉(zhuǎn)換單元、可編程數(shù)字單元、8051內(nèi)核和該系列中的所有器件具有兼容的存儲(chǔ)器分布,其中轉(zhuǎn)換單元含有4路DAC(分辨率可配置為8至10位),采用逐次逼近算法,可利用這些DAC實(shí)現(xiàn)高達(dá)800KHz采樣率的ADC(見圖4)。

圖4 數(shù)據(jù)轉(zhuǎn)換模塊的框圖

數(shù)據(jù)轉(zhuǎn)換模塊包含4個(gè)8位的逐次比較寄存器(SAR),它可以和內(nèi)部的DAC聯(lián)合工作,以獲得模/數(shù)轉(zhuǎn)換。

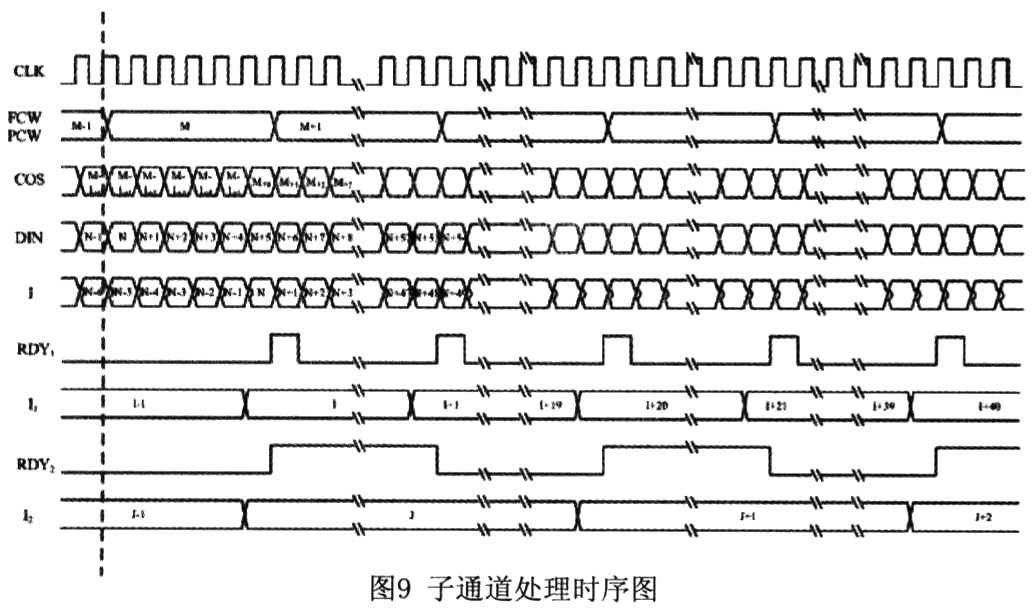

每一個(gè)通道有一個(gè)獨(dú)立的SAR,它接收逐次比較的結(jié)果,并驅(qū)動(dòng)對(duì)應(yīng)的DAC,每一個(gè)通道的轉(zhuǎn)換可以獨(dú)立進(jìn)行。當(dāng)轉(zhuǎn)換模塊編程為9或10位ADC轉(zhuǎn)換時(shí),相應(yīng)的SAR形成組:9位ADC時(shí),SAR1和SAR2為一組,SAR3和SAR4為一組;10位ADC時(shí),所有4個(gè)SAR形成一組。這時(shí),成組的SAR各自工作1至2個(gè)周期,在轉(zhuǎn)換結(jié)束時(shí),SAR將其內(nèi)容寄存在輸入/輸出寄存器中,并使能中斷產(chǎn)生模塊。在連續(xù)轉(zhuǎn)換模式下,將啟動(dòng)下一次轉(zhuǎn)換。在轉(zhuǎn)換過程中,可編程邏輯模塊可以獨(dú)立發(fā)布轉(zhuǎn)換命令,這將給本次以及下一次轉(zhuǎn)換帶來錯(cuò)誤。在連續(xù)轉(zhuǎn)換模式下,這將導(dǎo)致致命錯(cuò)誤,因?yàn)殄e(cuò)誤是可以傳遞的,并將得到不可預(yù)料的結(jié)果。

其控制部分是一個(gè)標(biāo)準(zhǔn)的8051微處理器。復(fù)合后,8051核首先對(duì)可編程元胞進(jìn)行配置,配置完畢后可以當(dāng)作一個(gè)通用的微處理器使用。為了更好的支持FIPSOC的動(dòng)態(tài)可重構(gòu)特性,已對(duì)其指令和功能單元做了一些改進(jìn)。

Cypress半導(dǎo)體公司的PSoC混合信號(hào)架構(gòu)將可編程的模擬與數(shù)字模塊同8位微控制器進(jìn)行了完美集成,這種獨(dú)特的功能組合使設(shè)計(jì)人員能夠針對(duì)各種應(yīng)用實(shí)現(xiàn)無與倫比的靈活性。最新CY8C23x33器件采用8位逐次逼近ADC,能實(shí)現(xiàn)高達(dá)375Ksps的采樣率。此外,該解決方案還具備可實(shí)現(xiàn)出色可配置性的26個(gè)GPIO,能夠快速適應(yīng)不斷變化的特性要求。該器件采用5x5mm的QFN封裝,能夠最大限度地縮小板極空間。

PSoC器件集成了通過一個(gè)片上微控制器進(jìn)行控制的可配置模擬和數(shù)字電路,提供更強(qiáng)大的設(shè)計(jì)修改功能,并進(jìn)一步減少元件數(shù)量。PSoC器件包括最大32Kb的閃存、2Kb的SRAM、一個(gè)帶有32位累加器的8x8乘法器、電源和睡眠監(jiān)控電路,以及硬件I2C通信[2]。

所有的PSoC器件都是可動(dòng)態(tài)重配置的,使得設(shè)計(jì)人員能夠隨意在運(yùn)行過程中改變內(nèi)部資源形式,使用較少的元件完成既定任務(wù)。易用的開發(fā)工具讓設(shè)計(jì)人員能夠選擇可配制程序庫元素來提供模擬功能(如放大器、ADC、DAC、濾波器和比較器),以及數(shù)字功能(如定時(shí)器、計(jì)數(shù)器、PWM、SPI和UART)。PSoC系列器件的模擬性能包括軌至軌輸入、可編程增益放大器和分辨率高達(dá)14位的ADC,以及超低的噪聲、輸入漏電流和電壓偏移。

單個(gè)PSoC器件可集成多達(dá)100個(gè)外圍部件,在提高系統(tǒng)質(zhì)量的同時(shí),節(jié)省客戶的設(shè)計(jì)時(shí)間,縮減板級(jí)空間和功耗,并使系統(tǒng)成本降低。

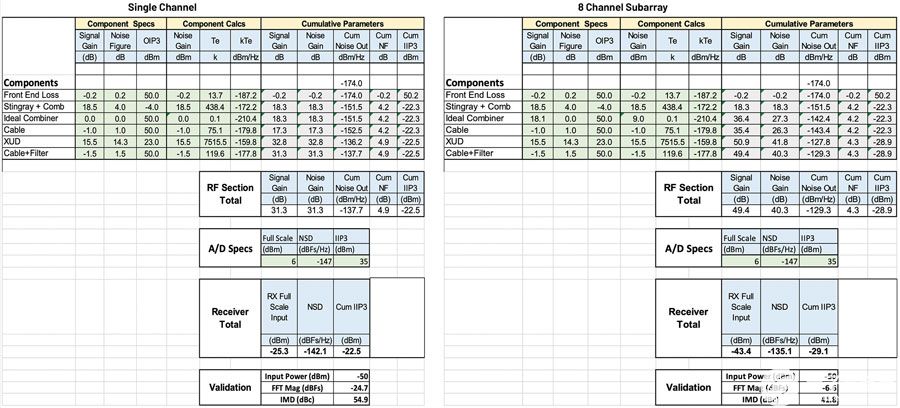

接收機(jī)設(shè)計(jì)

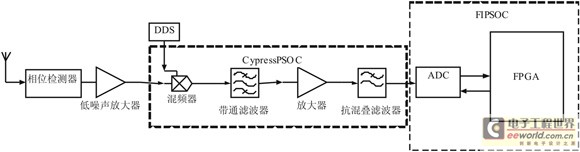

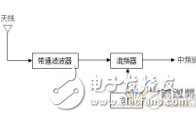

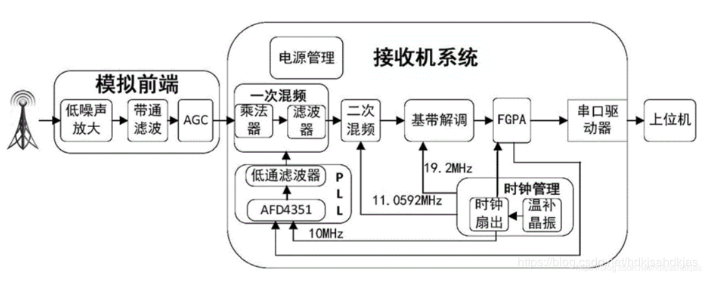

基于以上分析的結(jié)果,結(jié)合前端硬件電路,為實(shí)現(xiàn)一定的認(rèn)知無線電功能,特設(shè)計(jì)接收機(jī)結(jié)構(gòu)(見圖5)。

圖5 接收機(jī)結(jié)構(gòu)

前端低噪聲放大器選用的是ADA4857-1,這是一個(gè)超低損耗、低功率、高速運(yùn)算放大器,在SOIC結(jié)構(gòu)下的3dB帶寬可以達(dá)到750MHz,其開環(huán)增益為57dB,基本滿足此接收機(jī)對(duì)前端低噪聲放大器的要求。在搭建電路時(shí)尤其要注意電源旁路、寄生電容和外圍器件的選擇對(duì)充分發(fā)揮放大器性能的影響[3]。

DDS(直接頻率合成器)選用的是1GSPS的AD9858,其使用先進(jìn)的DDS技術(shù)和一個(gè)內(nèi)置的高速、高性能D/A轉(zhuǎn)換器組成數(shù)字可編程、完全高頻率的合成器,可以產(chǎn)生一個(gè)高達(dá)400MHz的模擬輸出正弦波,完全滿足接收機(jī)對(duì)本振的要求。

混頻器、帶通濾波器、放大器和抗混疊濾波器都可以由Cypress的PSOC器件cy8c23x33來統(tǒng)一實(shí)現(xiàn)。PSOC模擬系統(tǒng)包括一個(gè)8位SAR ADC和4個(gè)可配置模塊,每個(gè)模擬模塊由一個(gè)運(yùn)算放大器電路組成,允許模擬復(fù)信號(hào)流的建立。同時(shí),模擬外圍部件非常容易被定制從而滿足特殊應(yīng)用場合的需求。PSOC可以分別實(shí)現(xiàn)一個(gè)可編程帶通濾波器和一個(gè)低通濾波器以替代接收機(jī)前端需要的帶通濾波器和抗混疊濾波器,實(shí)現(xiàn)一個(gè)可選增益高達(dá)93dB的儀表放大器以替代中頻放大器,一個(gè)乘加累積器提供了一個(gè)快速8位乘法器以替代混頻器,以上可編程模擬器件均能基本滿足接收機(jī)前端性能要求。我們使用PSOC設(shè)計(jì)器進(jìn)行PSOC的工作配置,寫入使用PSOC的應(yīng)用程序并調(diào)試應(yīng)用。拿放大器來舉例,首先在設(shè)計(jì)器中找到這個(gè)模塊并新建一個(gè)電路,搭好外圍電路元件,按照建立時(shí)間、轉(zhuǎn)換速率和增益帶寬等幾個(gè)參數(shù)設(shè)定好初始值,產(chǎn)生應(yīng)用程序代碼,然后寫入主程序和子系統(tǒng)的任何子程序,如果所有程序正確,接著將產(chǎn)生一個(gè)HEX文件,最后由PSOC設(shè)計(jì)器中的調(diào)試器執(zhí)行,它下載HEX文件到在電路模擬器(ICE)中,至此一個(gè)可編程放大器設(shè)置完畢,可以投入使用。

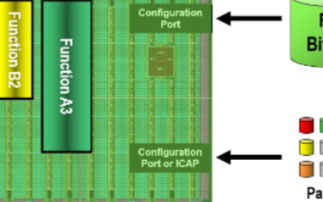

可編程ADC本來可以由Cypress PSOC來實(shí)現(xiàn),但PSOC實(shí)現(xiàn)的ADC采樣速率最多只有375 Ksps,無法滿足認(rèn)知無線電接收機(jī)前端的帶寬要求,因此可以考慮使用SIDSA公司的FIPSOC器件,同時(shí)后端基帶數(shù)字處理任務(wù)也可交由FIPSOC中的8051核和FPGA兼而實(shí)現(xiàn)。利用運(yùn)行于WINDOW環(huán)境下的集成化開發(fā)工具,進(jìn)行ADC的設(shè)計(jì)和編程,結(jié)合上面介紹的一部分內(nèi)容,具體到ADC設(shè)計(jì)時(shí)還需要首先設(shè)置外部輸入/輸出引腳、內(nèi)部輸入/輸出引腳和內(nèi)部信號(hào)的初始化數(shù)值,然后再對(duì)mP控制寄存器和靜態(tài)RAM進(jìn)行配置,以達(dá)到所需要的性能要求。數(shù)字宏單元(DMC)是FPGA的可編程數(shù)字單元,它是基于查找表結(jié)構(gòu)的可編程單元,具有組合邏輯和時(shí)序邏輯資源,而組合部分和時(shí)序部分之間則由布線資源加以連接。利用動(dòng)態(tài)重配置模式可對(duì)多個(gè)DMC單元進(jìn)行設(shè)置,可以改變硬件電路,進(jìn)而在一定程度上可對(duì)前端的可編程模擬器件進(jìn)行實(shí)時(shí)更新配置,這一技術(shù)目前正在探索研究中[4]。

以上只是各個(gè)模塊的分開設(shè)計(jì),但是設(shè)計(jì)好整個(gè)接收機(jī)系統(tǒng),還需要對(duì)各個(gè)模塊之間的連線以及參考時(shí)鐘等許多方面給以足夠的重視。各個(gè)模塊都有屬于自己的輸入/輸出端口,為達(dá)到預(yù)定的系統(tǒng)性能要求,必須嚴(yán)格對(duì)照技術(shù)手冊(cè)和自己的預(yù)先布線安排接好各輸入/輸出端口。至于時(shí)鐘,避免采用時(shí)鐘抖動(dòng)大的門電路是電路設(shè)計(jì)中需要嚴(yán)格遵守的準(zhǔn)則之一,在此基礎(chǔ)上才能最大限度地發(fā)揮器件的性能;除此,拿FIPSOC來說,除某些條件下,8051時(shí)鐘和其送至DMC的副本時(shí)鐘的相對(duì)相位會(huì)交換外,時(shí)鐘停止不影響時(shí)鐘同步;每次不同時(shí)鐘重新配置后,必須重新同步。

結(jié)語

目前,已經(jīng)在理論上證明了以上接收機(jī)結(jié)構(gòu)設(shè)計(jì)的可行性,下一步將逐步搭建出具體的硬件平臺(tái)并測試驗(yàn)證。除了可編程模擬器件外,新興的可進(jìn)化硬件(Evolvable HardWare,EHW)研究領(lǐng)域以硬件在線自適應(yīng)為目標(biāo),也將可編程模擬器件作為實(shí)現(xiàn)模擬電路自動(dòng)設(shè)計(jì)和在線自適應(yīng)的重要評(píng)估手段和實(shí)現(xiàn)載體。可以預(yù)期,隨著模擬可編程技術(shù)的不斷進(jìn)步和器件品種的逐步豐富,可編程模擬器件將會(huì)成為實(shí)現(xiàn)模擬電路的首選器件和最佳選擇。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論