基于FPGA的高斯白噪聲發(fā)生器設(shè)計(jì)

0 引 言

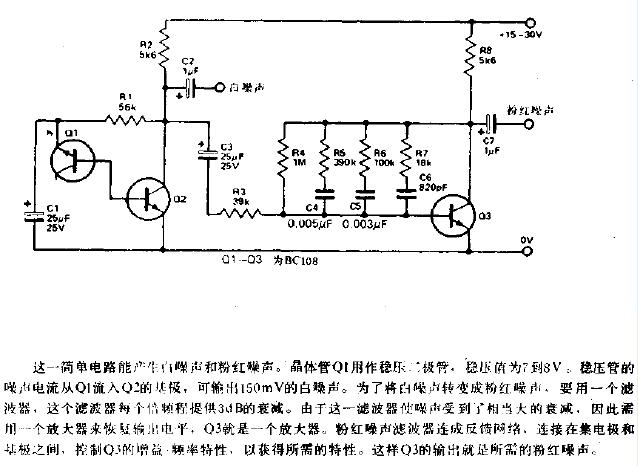

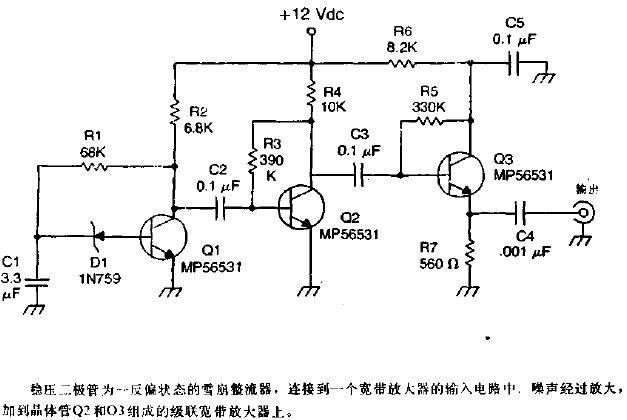

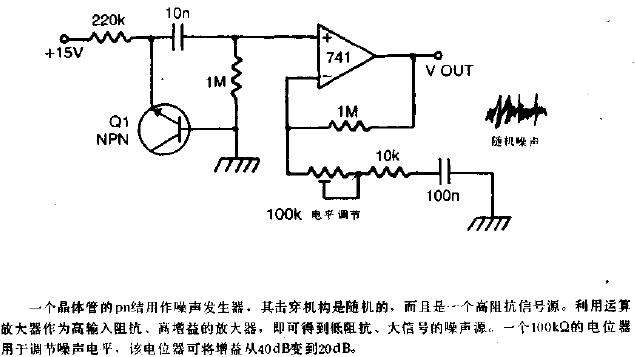

現(xiàn)代通訊電子設(shè)備的抗干擾測(cè)試已經(jīng)成為必須的測(cè)試項(xiàng)目,主要的干擾類型為噪聲干擾。在通信信道測(cè)試和電子對(duì)抗領(lǐng)域里,噪聲始終是最基本、最常用的干擾源之一。如何產(chǎn)生穩(wěn)定和精確的噪聲信號(hào)已經(jīng)成為一個(gè)重要的研究領(lǐng)域。其中,帶限白噪聲信號(hào)時(shí)間相關(guān)性小,目前應(yīng)用最廣泛。現(xiàn)有的硬件高斯白噪聲發(fā)生器通常分為物理噪聲發(fā)生器和數(shù)字噪聲發(fā)生器兩類,數(shù)字噪聲發(fā)生器雖然沒(méi)有物理噪聲發(fā)生器的精度高,但是實(shí)現(xiàn)電路較為簡(jiǎn)單,易于應(yīng)用。

FPGA技術(shù)的發(fā)展,提高了硬件噪聲發(fā)生器的速度和性能,相比基于軟件實(shí)現(xiàn)的噪聲發(fā)生器,展現(xiàn)出更大的優(yōu)勢(shì)。本文設(shè)計(jì)的高斯白噪聲發(fā)生器采用FPGA的方式實(shí)現(xiàn),輸出的基帶白噪聲帶寬可調(diào),范圍為1~66 MHz,步進(jìn)3 MHz,幅度8位可調(diào),同時(shí)可產(chǎn)生正弦波、三角波、鋸齒波、方波等函數(shù)波,通過(guò)更改現(xiàn)場(chǎng)可編程器件的配置波形數(shù)據(jù)也可產(chǎn)生其他復(fù)雜函數(shù)波形。

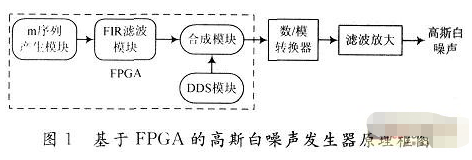

l 高斯白噪聲發(fā)生器原理

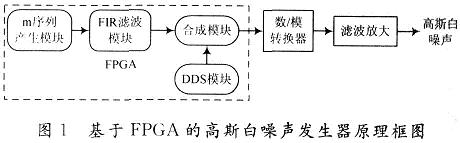

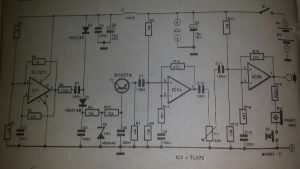

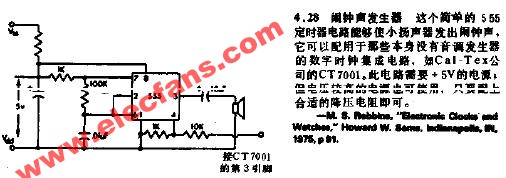

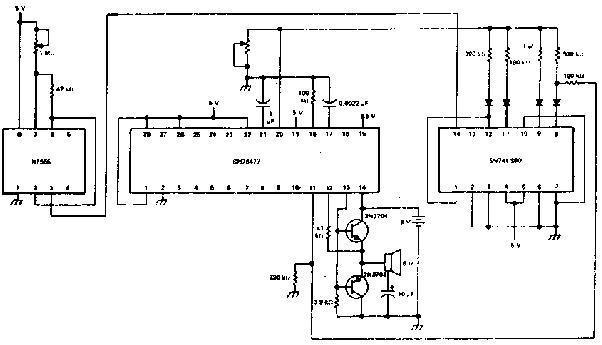

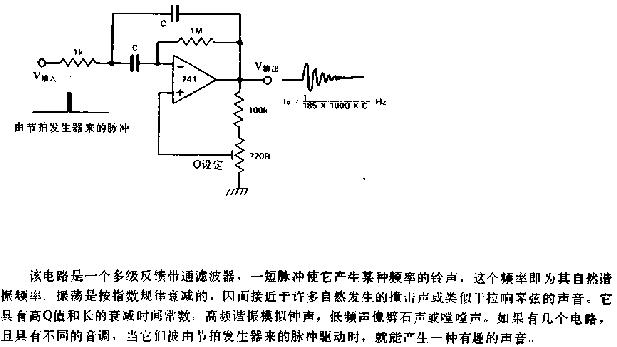

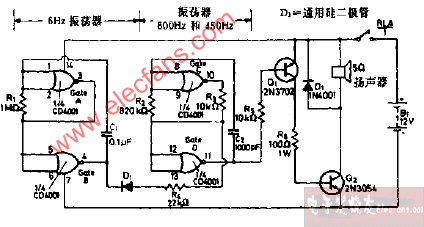

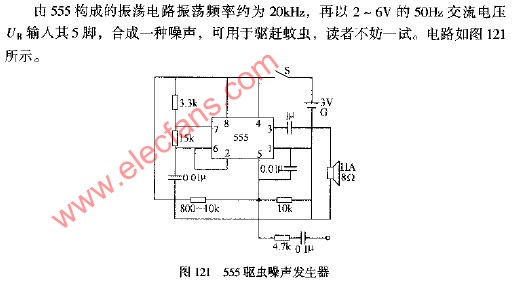

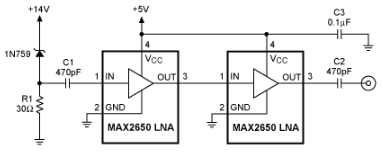

本文所述的高斯白噪聲發(fā)生器如圖1所示。

首先,在現(xiàn)場(chǎng)可編程門(mén)陣列(Field Programmable Gate Array,F(xiàn)PGA)平臺(tái)上以一個(gè)統(tǒng)一的時(shí)鐘速度(以后稱之為噪聲發(fā)生速度,即f0)生成高速m序列偽隨機(jī)碼流,對(duì)該序列進(jìn)行有限沖擊響應(yīng)(Finite Impulse Response,F(xiàn)IR)數(shù)字濾波處理,得到帶限白噪聲數(shù)字序列,同時(shí)在FPGA中實(shí)現(xiàn)直接數(shù)字綜合(Direct Digital Synthesizer,DDS)算法,產(chǎn)生正弦數(shù)字序列,并與噪聲序列合成;其次,將以上得到的數(shù)字序列通過(guò)高速數(shù)/模轉(zhuǎn)換器(Digital Analog Converter,DAC)轉(zhuǎn)換為模擬噪聲信號(hào);再次,通過(guò)LC低通濾波器以及放大器轉(zhuǎn)換為模擬帶限白噪聲和正弦信號(hào),該信號(hào)即為基帶白噪聲信號(hào)。下面對(duì)涉及的基本算法進(jìn)行分析和仿真。

高斯白噪聲發(fā)生方法中涉及偽隨機(jī)碼發(fā)生算法、數(shù)字濾波算法和正弦波發(fā)生算法。本文詳細(xì)論述這幾種算法,及其在FPGA上的實(shí)現(xiàn)方法,分析了各種算法在頻域上的頻譜特性。

2 高斯白噪聲發(fā)生器算法分析

2.1 偽隨機(jī)碼發(fā)生算法

偽隨機(jī)碼(Pseudo-random Sequence,PS)的性能指標(biāo)直接影響產(chǎn)生白噪聲的隨機(jī)性,是系統(tǒng)設(shè)汁的關(guān)鍵。通常產(chǎn)生偽隨機(jī)碼的電路為一反饋移存器,分為線性和非線性兩類。前者產(chǎn)生周期最長(zhǎng)的二進(jìn)制數(shù)字序列為最大長(zhǎng)度線性反饋移存器序列,簡(jiǎn)稱m序列。本文采用的就是m序列偽隨機(jī)碼。

產(chǎn)生m序列的反饋移存器的遞推方程可以寫(xiě)為:

它給出了移位輸入an與移位前各級(jí)狀態(tài)的關(guān)系。

特征多項(xiàng)式寫(xiě)為:

它決定了移位寄存器的反饋連接和序列的結(jié)構(gòu)。

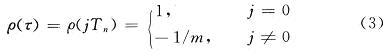

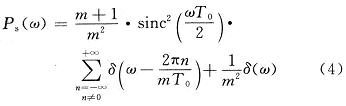

m序列的自相關(guān)函數(shù)可表示為:

式(3)為一個(gè)周期(m=2n-1)內(nèi)的函數(shù),其中Tn為偽隨機(jī)噪聲碼元的寬度。整個(gè)時(shí)域的自相關(guān)函數(shù)的周期為m=2n-1。信號(hào)的自相關(guān)函數(shù)與功率譜密度構(gòu)成一對(duì)傅里葉變換,因此m序列的自相關(guān)函數(shù)經(jīng)過(guò)傅里葉變換,其功率譜密度為:

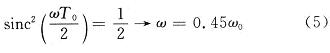

假定零頻處的功率為1,那么功率下降為0.5處的頻率為:

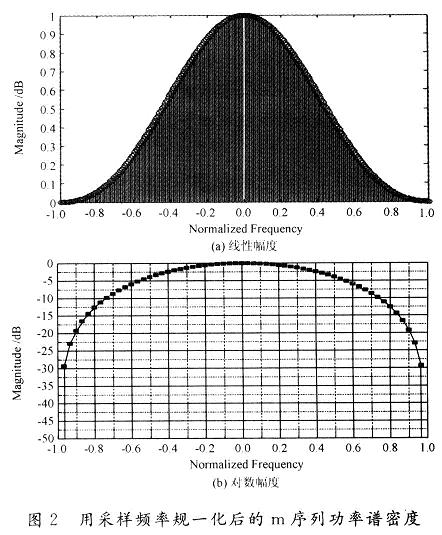

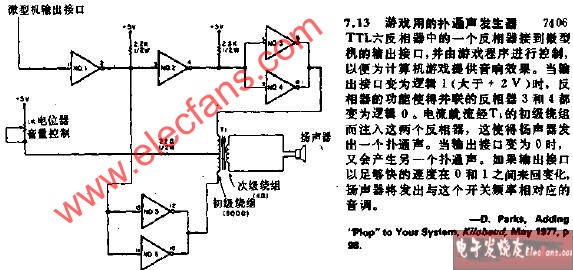

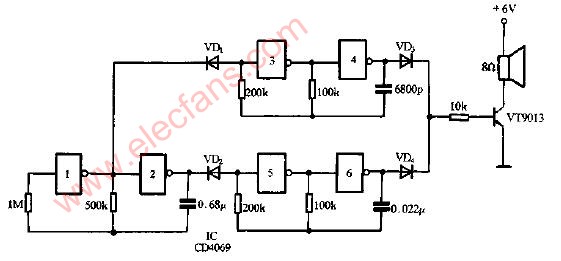

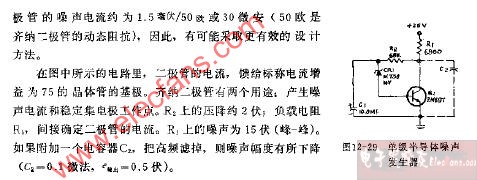

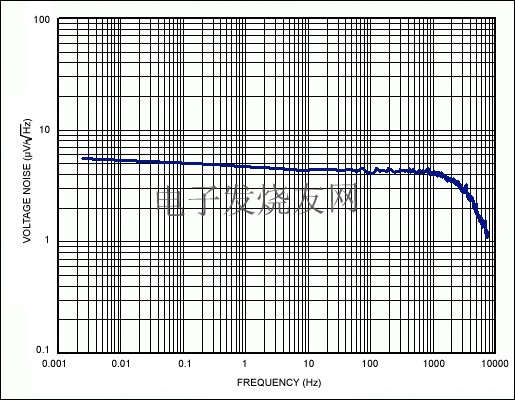

其典型的功率譜密度如圖2所示。

由圖2可以看出,m序列的功率譜密度的包絡(luò)是[(sin x)/x]2形的,它約在偽隨機(jī)序列基本時(shí)鐘頻率的45%帶寬內(nèi)具有均勻功率譜密度,所以用濾波器濾除該頻帶內(nèi)的信號(hào)就可以近似看作帶限白噪聲。m序列的均衡性、游程分布、自相關(guān)特性和功率譜與隨機(jī)序列的基本性質(zhì)很相似,所以m序列屬于偽噪聲的序列或偽隨機(jī)序列。

2.2 FIR數(shù)字濾波算法

m序列的功率譜是固定的,要生成帶寬可調(diào)的數(shù)字噪聲序列需要對(duì)m序列進(jìn)行低通數(shù)字濾波,本文采用的是FIR數(shù)字濾波器。

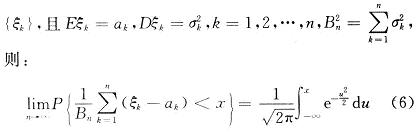

由Lindeberg定理可知,設(shè)有獨(dú)立隨機(jī)變量序列

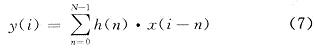

該定理證明了由大量微小且獨(dú)立的隨機(jī)因素引起,并積累而成的變量,必是一個(gè)正態(tài)隨機(jī)變量。FIR濾波器的單位沖激響應(yīng)為h(n),0≤n≤N一1,輸入函數(shù)為x(i),則輸出函數(shù)y(i)可以寫(xiě)為:

該算法需要N次相乘,N-1次累加。為了產(chǎn)生帶寬小于5 MHz高質(zhì)量的數(shù)字噪聲序列,需要構(gòu)建窄通帶、通帶阻帶轉(zhuǎn)換迅速的低通濾波器,對(duì)此僅僅增加單級(jí)FIR濾波的沖激相應(yīng)長(zhǎng)度n是不夠的,對(duì)此本文采用了多級(jí)FIR數(shù)字濾波的方法。為了使得多路多級(jí)FIR濾波器能夠在常用FPGA平臺(tái)上實(shí)現(xiàn),對(duì)FIR數(shù)字濾波模型進(jìn)行算法優(yōu)化,以節(jié)約所需邏輯單元資源是很有必要的。

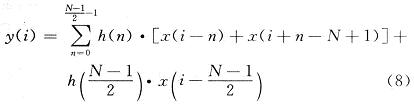

采用單位沖激相應(yīng)h(n)為偶函數(shù)的FIR濾波器,并取階數(shù)N為奇數(shù),則式(6)可以化簡(jiǎn)為:

采用該方法可以將FIR算法中乘的次數(shù)減半,總計(jì)算量減為(N+1)/2次相乘,N-2次累加,極大地節(jié)省了FPGA的邏輯單元資源。FIR的濾波過(guò)程實(shí)質(zhì)上就是一個(gè)延遲后加權(quán)相加的過(guò)程,即濾波輸出y(i)是輸入x(i)以及它的前N一1個(gè)狀態(tài)的加權(quán)疊加。

2.3 DDS算法

隨著數(shù)字集成電路和微電子技術(shù)的發(fā)展,直接數(shù)字頻率合成器(Direct Digital Synthesizer,DDS)逐漸體現(xiàn)出其具有相對(duì)帶寬寬,頻率轉(zhuǎn)換時(shí)間短,頻率分辨率高,輸出相位連續(xù),可編程及全數(shù)字化結(jié)構(gòu)等優(yōu)點(diǎn)。

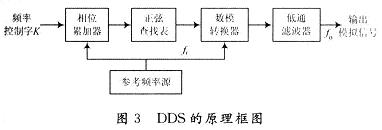

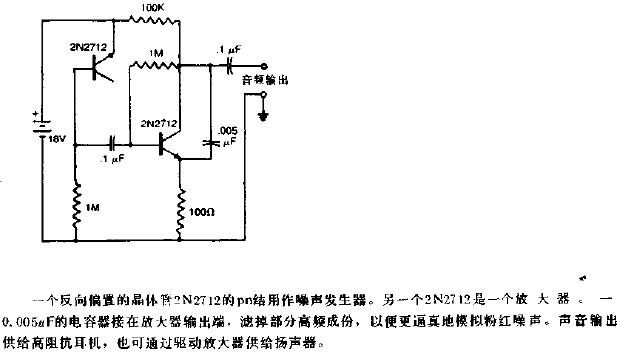

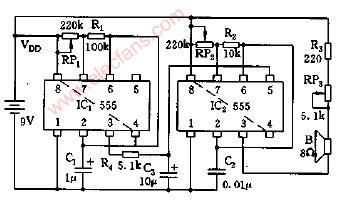

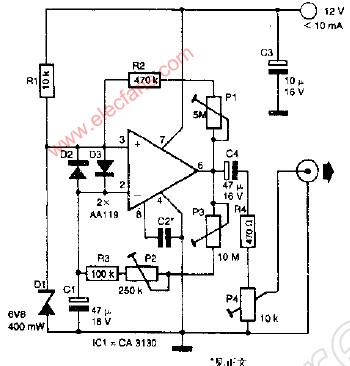

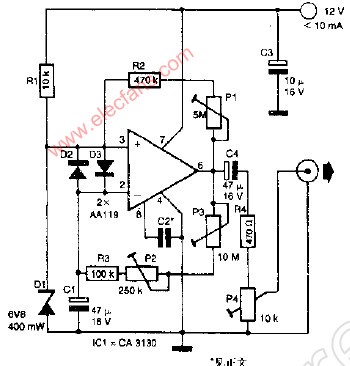

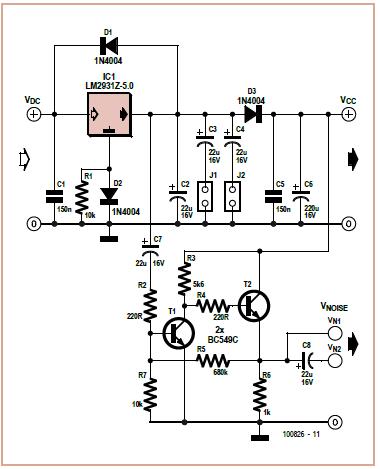

DDS的基本工作原理是根據(jù)正弦函數(shù)的產(chǎn)生,從相位出發(fā),用不同的相位給出不同的電壓幅度,最后濾波平滑出所需要的頻率。圖3是DDS的原理方框圖。

參考頻率源又稱參考時(shí)鐘源,它是一個(gè)穩(wěn)定的晶體振蕩器,用來(lái)同步DDS的各組成部分。相位累加器類似于一個(gè)計(jì)數(shù)器,它由多個(gè)級(jí)聯(lián)的加法器和寄存器組成,在每一個(gè)參考時(shí)鐘脈沖輸入時(shí),它的輸出就增加一個(gè)步長(zhǎng)的相位增量值,這樣相位累加器把頻率控制字K的數(shù)字變換成相位抽樣來(lái)確定輸出合成頻率的大小。相位增量的大小隨外指令頻率控制字K的不同而不同,一旦給定了相位增量,輸出頻率也就確定了。當(dāng)用這樣的數(shù)據(jù)尋址時(shí),正弦查表就把存儲(chǔ)在相位累加器中的抽樣數(shù)字值轉(zhuǎn)換成近似正弦波幅度的數(shù)字量函數(shù)。以上的算法都可在FPGA內(nèi)部實(shí)現(xiàn)。

3 實(shí)驗(yàn)結(jié)果

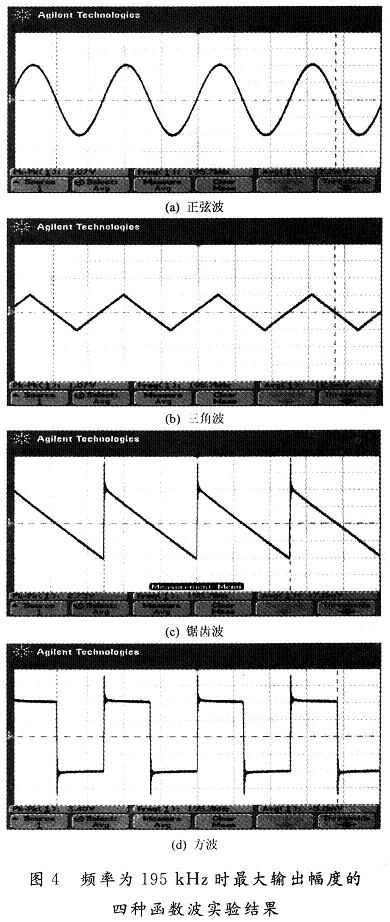

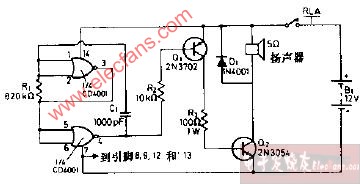

本文的FPGA平臺(tái)選用Altera公司的EP2C8現(xiàn)場(chǎng)可編程邏輯器件,完成所有m序列、FIR數(shù)字濾波和DDS算法,需要FPGA 86%的邏輯單元資源和1%的RAM資源;時(shí)鐘采用50MHz、穩(wěn)定度為50 ppm的有源晶振,通過(guò)EP2C8內(nèi)部PLL(Phase Locked Loop,鎖相環(huán))3倍頻到150 MHz作為系統(tǒng)全局時(shí)鐘;采用ADI公司的AD9731進(jìn)行D/A轉(zhuǎn)換,采樣速度150 MSPS,10位;對(duì)AD9731輸出的電流信號(hào)進(jìn)行7階LC低通濾波,然后進(jìn)行放大,使得噪聲信號(hào)的滿幅輸出都達(dá)到峰峰值3V。圖4是頻率為195 kHz最大輸出幅度的四種函數(shù)波測(cè)試結(jié)果。

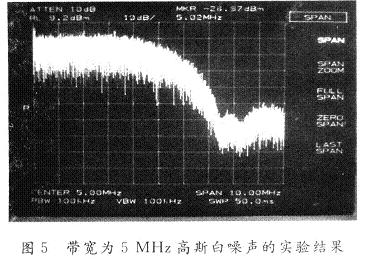

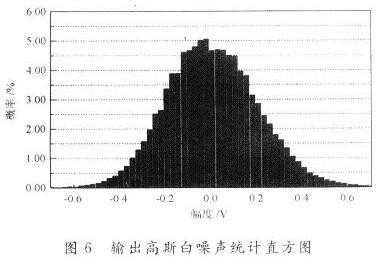

從圖4可以看出,采用DDS模塊,得到了正弦波、三角波、鋸齒波和方波的波形。圖5為該噪聲和函數(shù)波發(fā)生器產(chǎn)生的5 MHz噪聲的實(shí)驗(yàn)結(jié)果,圖6是輸出帶寬為5 MHz的高斯白噪聲統(tǒng)計(jì)直方圖。

從圖5和圖6可以看出,基于FPGA的m序列發(fā)生算法,F(xiàn)IR濾波算法和DDS算法,通過(guò)數(shù)/模轉(zhuǎn)換和低通放大后,本文設(shè)計(jì)的噪聲發(fā)生器產(chǎn)生的5 MHz噪聲的3 dB,帶寬為4.8 MHz,帶內(nèi)平坦度為±1.5 dB,輸出噪聲的統(tǒng)計(jì)特性服從高斯分布,滿足了設(shè)計(jì)需要。

4 結(jié) 語(yǔ)

設(shè)計(jì)了一種基于FPGA高斯白噪聲發(fā)生器,分析了該種噪聲發(fā)生器所用的m序列發(fā)生算法,F(xiàn)IR數(shù)字濾波算法和DDS算法,可產(chǎn)生帶寬為3~66 MHz,步進(jìn)3 MHz,幅度8位可調(diào)的高斯白噪聲;采用現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)實(shí)現(xiàn)噪聲發(fā)生器的設(shè)計(jì),在Altera公司的QuartusⅡ軟件環(huán)境下,實(shí)現(xiàn)了基于FPGA的m序列產(chǎn)生模塊、FIR數(shù)字濾波器模塊、DDS模塊和合成模塊,通過(guò)數(shù)/模轉(zhuǎn)換器和低通放大,得到了可用于雷達(dá)系統(tǒng)和通信信道測(cè)試的高斯白噪聲信號(hào)。實(shí)驗(yàn)結(jié)果驗(yàn)證了本文設(shè)計(jì)的有效性。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論