采用帶有收發器的全系列40-nm FPGA和ASIC實現創新設計

?? 人們對寬帶服務的帶寬要求越來越高,促使芯片供應商使用更多的高速串行收發器。因此,下一代應用采用了多種數據速率,從幾Mbps 到數百Gbps,在一種設備中集成了多種協議和服務。以太網等迅速發展的標準以及對提高數據速率的需求使得高速收發器成為主要的性能判定依據。標準單元ASIC 和ASSP 不具有人們需要的靈活性,其成本和風險無法讓用戶及時實現技術創新。本文介紹帶有收發器的全系列40-nmFPGA 和ASIC,發揮前沿技術優勢,在前一代創新基礎上,解決下一代系統難題。

引言

???? 現代意義上的互聯網雖然只經歷了十幾年的時間,卻已經成為技術創新和帶寬增長的主要推動力量。更新現有通信系統以及新應用的出現要求采用更大的寬帶和更高的數據速率。今天,以視頻為主的網絡下載和點對點網絡連接( 文件共享) 占用了80% 的帶寬。流媒體( 視頻點播電影和電視)、IP 承載視頻和互聯網游戲等新應用占用的帶寬不到10% 。考慮到這些因素,互聯網仍處于發展初期,今后將持續強勁增長。

??? 市場上最近推出的通信設備已經開始向40 甚至100 千兆以太網(GbE) 端口過渡,以更低的成本和功耗,在更緊湊的封裝中實現更大的帶寬。而且,摩爾定律還在不斷推動著半導體行業發展,集成電路上的晶體管數量每兩年就會加倍。新一代產品使用45-nm 或者40-nm 工藝來集成更多的功能,提高每一功能的工作性能和邏輯密度,降低功耗,而滿足日益增長的帶寬需求的關鍵則是更多、更快的高速串行收發器。

??? 本文介紹高速串行收發器的發展趨勢,以及系統規劃人員和設計人員所面臨的挑戰。文章還回顧了某些特殊的市場需求,為滿足這些需求,可編程邏輯器件(PLD) 供應商必須提供帶有收發器的多種產品組合。這些器件具有豐富的邏輯、特性和I/O 功能,客戶利用它們能夠開發出滿足各種性能、功耗和成本目標的產品。

??? 高速收發器技術的發展趨勢提高高速串行收發器的數據速率以及器件中收發器的數量可以實現更大的帶寬和更高的數據速率。使用以

下技術可以獲得帶寬達到100G 的接口:

■ 10 個10.3-Gbps 收發器(CAUI 協議)

■ 20 個6.375-Gbps 收發器(Interlaken 協議)

■ 40 個3.125-Gbps 收發器(XAUI 協議)

■ 100 個1.25-Gbps 收發器(SGMII 協議,注意,這只是用于演示目的,并不實用)

??? 考慮到每個器件所有輸入和輸出數據通道的兩端口需求,如果收發器數據速率不能相應的提高,即使是采用最現代的工藝技術也難以滿足收發器的數量要求。

??? 很多系統混合了DSP 模塊、控制處理器、ASSP、ASIC 和FPGA。系統規劃人員面臨的挑戰是對系統進行劃分,把這些器件連接起來,以滿足應用性能和帶寬要求。在很多情況下,由于ASSP 和ASIC 技術創新發展較慢,無法實現更快的接口。另一挑戰是這些器件所提供的各類協議,規劃人員不得不犧牲性能,重新使用原來的接口。這一般通過橋接器件——傳統的FPGA,連接原來的協議和新協議。解決這些問題最終會降低系統成本。

??? 帶有收發器的數據鏈路不但支持更高的數據吞吐量,而且功效非常高,進一步提高了系統集成度,成為系統的關鍵組成部分。串化器/ 解串器(SERDES) 收發器是替代原有并行技術所必須采用的技術。通過使用收

發器技術,設計人員能夠解決當今高速數據鏈路設計中的關鍵問題:

■ 信號完整性:相對于并行接口,串行接口的延時和偏移都比較低。在串行協議應用,以及驅動背板方面,要求收發器具有優異的信號完整性,較低的抖動和誤碼率(BER)。

采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計Altera 公司

2

■ 復雜的電路板:使用串行接口可以減小電路板面積,減少所使用的電路板元件數量以及電路板層數。例如, PCI Express (PCIe) 接口將引腳和電路板面積減少了50%,而帶寬提高了一倍。

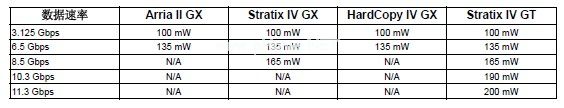

■ 功耗和散熱:串行接口的功耗要低于并行接口。例如,Stratix IV GT FPGA 的10G 接口在10.3 Gbps 時的功耗為190 mW, Altera 40-nm 收發器上的收發器 PMA 功率。表1 詳細列出了40-nm 工藝節點各種數據速率下的功耗。

總之,系統規劃人員面臨三種主要挑戰:

■ 在提高帶寬和數據速率時,需要更多、更快的收發器。

■ 既有原來的高速協議,又有各種不斷發展的新標準。

■ 符合背板和協議要求需要有優異的信號完整性。

收發器接口是系統規劃人員首先要考慮的關鍵因素,而器件選擇取決于所能夠提供的功能、性能、功耗和成本目標。最終,一定的市場需求決定了收發器系列產品最合適的功能。

市場需求

圖1 顯示了使用以太網協議的幾個例子,目前的通信基礎設施中使用了收發器。網絡中的每一部分都使用

了串行收發器技術,但是有不同的帶寬要求。越靠近用戶側,成本和功耗就越敏感,同時,帶寬也在降低,

收發器速率和數量也在減少。此外,隨著實際應用中處理需求的變化,器件密度和特性的關系也在不斷變

化。

圖1. 通信基礎設施中的收發器

表1. PMA 收發器功耗/ 通道對比

3

固網接入、傳輸和網絡設備

以太網已經發展成為當今應用最廣泛的物理層和鏈路層協議。而作為IEEE 標準802.3ae 于2002 年發布的10GbE 是目前最快的標準, IEEE正在制定40GbE和100GbE 以太網標準。網絡已經向數據包傳輸和全以太網設備過渡,應用范圍包括數據包處理和流量管理功能為主的橋接和全數據通道處理等(1)。根據網絡中靠近用戶的程度以及位置,帶寬從10 Gbps 至20 Gbps 發展到 40 Gbps 至80 Gbps,甚至是100 Gbps。并不存在能夠滿足所有需求的解決方案,因此,設備必須能夠支持不同的密度、特性、性能、功耗和成本目標。

關鍵需求推動了技術創新,包括對集成10G 收發器、高密度和高性能的需求,以及對以太網、GPON、CEI-6/Interlaken 和SONET/SDH 等協議標準的支持。

無線設備

?? 過去,無線標準( 空中接口) 在發展過程中采用了不同的技術和物理通道,但是,對于3.9G/4G,更大的載波帶寬(20 MHz) 使得所有主要空中新接口使用OFDMA 技術。雖然正交頻分復用多址接入/ 多輸入多輸出(OFMDA-MIMO) 方法有可能在不久的將來實現技術融合,但目前的標準仍在不斷發展,繼續得以實施。

??? 主要的無線需求包括在同一系統中對多種標準的支持,新一代體系結構中較強的信號處理能力,減少系統總延時等,所有這些需求都要求進一步提高集成度。而且,無線解決方案必須能夠靈活的延伸到名為毫微微基站( 以及微微基站、微基站和宏基站等) 的家庭基站中。這些市場和技術要求推動了高度集成方案的發展,最終成為芯片系統(SoC)。而且,這些收發器PLD 所具有的優點和其他解決方案具有可比性,甚至優于其他方案:

■ 在用戶數量或者每單元吞吐量上的成本和性能

■ 每Mbps 和每mm2 功耗和面積

■ 不同空中接口和協議的芯片間、卡對卡以及機箱之間接口高速收發器的靈活性和可更新能力

?? 此外,很難有能夠滿足所有需求的通用解決方案。推動技術創新的關鍵需求包括更高的集成度,更低的成本,更好的性能,集成了DSP 功能的信號處理能力,以及支持CPRI/OBSAI 和Serial RapidIO? 等專用協議。

軍事、廣播、計算機和存儲、測試和醫療,以及其他市場領域

?? 其他市場領域對收發器的需求各有不同,需要綜合考慮密度、性能、特性和功耗要求。PCIe Gen1 和Gen2以及以太網等標準協議得到了廣泛應用。某些市場對協議有特殊的要求,例如,廣播應用的SDI,以及計算機和存儲的SATA/SAS、HyperTransport? 和QPI 等。由于很多應用只需要采用支持專用協議的收發器,因此, 10G 收發器在寬帶連接上迅速得到了應用,成為很多產品的主要技術推動力量。

關鍵技術

??? 帶有收發器的FPGA 和ASIC 系列產品采用的技術包括工藝技術、支持可編程功耗技術的功耗和性能優化措施、邏輯架構、I/O、PLL、外部存儲器接口、高速串行收發器、時鐘數據恢復和時鐘產生、預加重和均衡,以及在PCIe 等協議上應用硬核知識產權(IP) 等。

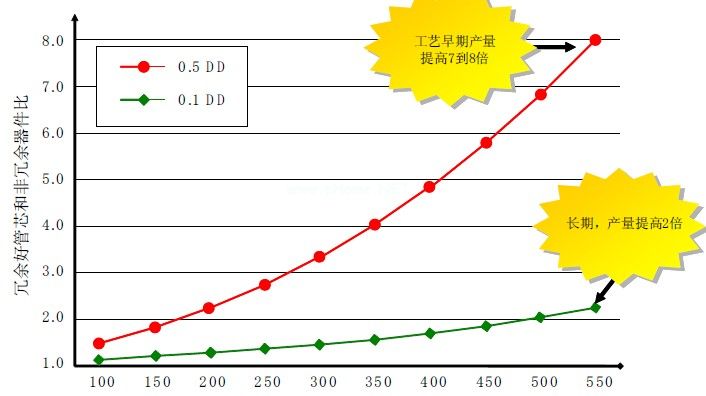

?? 工藝技術和40-nm 的優勢和以前的65-nm 節點以及最近的45-nm 節點相比, 40-nm 工藝有很大的優勢。最顯著的一點是更高的集成度,半導體生產商可以在更小的管芯中集成更多的功能,生產出密度更高的器件。

???? 40-nm 工藝還進一步提高了性能。40 nm 最小的晶體管邏輯門長度比65 nm 邏輯門長度短38.5%,比45-nm 工藝的邏輯門長度短11%。40 nm 的阻抗進一步降低,從而提高了驅動能力,實現了性能更好的晶體管。應變硅技術使電子和空穴的移動能力提高了30%,晶體管性能提高了近40%。

采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計Altera 公司

4

?? 雖然密度和性能的提高非常顯著,但是,當今系統開發人員在設計中需要著重考慮的是功耗問題。40-nm節點在功耗上也有一定的優勢,更小的工藝尺寸減小了導致動態功耗的雜散電容。特別是,臺積電(TSMC)的40-nm 工藝技術要比其45-nm 工藝技術的有功功耗低15%。(2)

??? 但是,工藝尺寸的降低卻增大了待機功耗。Altera 使用多種方法來降低靜態功耗,包括多閾值晶體管、長度不同的晶體管溝道、三重氧化等,并且在對性能要求不高的PLD 上綜合考慮性能和功耗,例如配置邏輯等。

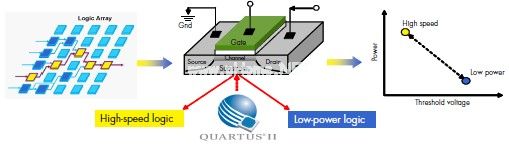

可編程功耗技術和性能

除了常用的電路設計方法, Altera 還引入了65-nm Stratix? III FPGA 的可編程功耗技術(3) 來降低靜態功耗。可編程功耗技術使靜態功耗降低了70%,在設計中以最低的功耗實現最好的性能。這一創新技術利用了這一事實——在典型設計中,全部邏輯中只有很少一部分用在關鍵時序通道上。基準測試表明,時序余度很小的高性能邏輯和時序余度較大的慢速邏輯比平均為30:70。

??? 在任何設計中, Altera 的Quartus? II 開發軟件自動確定設計中每一通道的松弛余度。這樣,通過調整晶體管的反向偏置電壓,將每一邏輯模塊、存儲器和DSP 模塊的晶體管自動設置為合適的模式——高性能或者低功耗:

■ 在低功耗模式中, Quartus II 軟件減小反向偏置電壓,使晶體管很難接通。這樣,減小了時序不重要電路中的亞閾值泄漏電流,以及無用的靜態功耗( 圖2 中的藍色部分)。

■ 在高性能模式中, Quartus II 軟件增大反向偏置電壓,時序關鍵通路上的晶體管更容易接通,以滿足設計中規定的時序約束要求,實現最佳性能( 圖2 中的黃色部分)。

圖2. Quartus II 軟件降低了功耗,提高了性能

邏輯架構和通用I/O

?? Altera 的40-nm 器件架構使用了包括自適應邏輯模塊(ALM)、TriMatrix 片內存儲器模塊和DSP模塊的通用內核邏輯體系結構。ALM 含有一個可配置8 輸入分段式查找表(LUT)、兩個嵌入式加法器和兩個寄存器,并采用了MultiTrack 互聯結構進行布線,以支持高速邏輯、算法和寄存器功能,器件利用率非常高。

?? TriMatrix 片內存儲器提供三種不同的存儲器模塊容量,大大提高了效率和靈活性,如圖3 所示。

Power

High speed

Low power

Threshold voltage

Source

Substrate

Drain

Channel

Gnd

Gate

High Speed Logic Low Power Logic

High-speed logic Low-power logic

Altera 公司 采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計

5

圖3. TriMatrix 存儲器結構

圖4 中的DSP 模塊是高性能芯片體系結構,其強大的可編程能力可以在多種應用中實現最佳處理功能。每一模塊含有8 個18x18 乘法器,以及寄存器、加法器、減法器、累加器和求和單元,這些都是典型DSP 算法中常用的功能。DSP 模塊支持可變位寬和各種取整飽和模式,有效地滿足了應用需求。

圖4. DSP 模塊體系結構

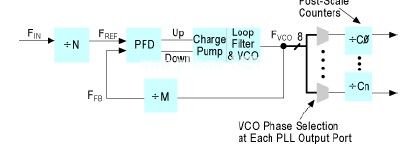

通用PLLAltera 的通用鎖相環(PLL) 包括閉環頻率控制系統,該系統基于輸入時鐘信號和受控振蕩器反饋時鐘信號之間的相位差。圖5 顯示了PLL 中主要組件的簡要結構。

6

圖5. PLL 結構圖

這些PLL 的模擬特性使其具有非常低的抖動,能夠實現可靠的時鐘方案。很多可配置時鐘輸出能夠非常靈活的實現系統時鐘,為存儲器接口和I/O 接口輸出時鐘。

最佳通用I/O 和外部存儲器接口

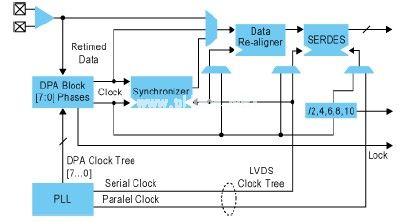

如圖6 所示, I/O 結構的關鍵構建模塊包括:

■ 單端I/O 支持,提供可編程擺率和驅動能力,可變延遲鏈補償電路板走線,以及串行和并行動態片內匹

配(OCT)。

■ 支持差分片內匹配的高性能LVDS 傳輸和接收差分信號

■ 為多通道LVDS 接口提供的硬核動態相位對齊(DPA) 模塊,避免了時鐘至通道和通道至通道偏移,以及

時鐘轉發功能,實現軟核時鐘數據恢復(CDR)。

圖6. DPA 結構圖

Altera 的I/O 引腳支持已有以及新興的外部存儲器標準,例如,DDR、DDR2、DDR3、QDRII、QDRII+ 和RLDRAMII 等。它們包括自校準數據通路,對自己不斷進行動態調整,在工藝、電壓和溫度變化時,提供最可靠的工作頻率。其他電路包括對齊和同步、通道去偏移、讀/ 寫調平,以及時鐘域交叉功能等。

高速串行收發器

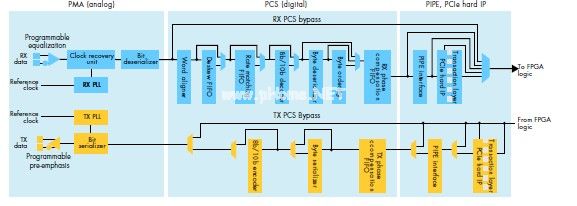

Altera的高速收發器模塊在物理介質附加(PMA)和物理編碼子層(PCS)使用通用體系結構(圖7所示)。 根據設計人員的不同要求,可以旁路PCS 中的模塊。

Altera 公司 采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計

7

圖7. PMA 和PCS 結構圖

PMA 功能可以用在模擬電路中,包括:

■ CDR

■ SERDES

■ 可編程預加重和均衡

■ I/O 緩沖,支持動態可控設置( 輸出差分電壓和差分OCT)。

PCS 提供數字功能以適應背板、芯片至芯片和芯片至模塊應用的多種關鍵協議。這些數字模塊為增強對協議的支持而進行了優化,減少了實現物理層協議所需要的器件資源,同時降低了功耗。與特定的IP 和參考設計相結合,這些模塊能夠提供完整的協議解決方案,縮短了設計周期,降低了風險。PCS 功能的例子包括8b/10b 編碼器/ 解碼器、相位補償FIFO 緩沖、字對齊器和速率匹配器,在收發器模塊中提供對協議的支持。

此外,還提供專用狀態機,支持PCIe、GbE 和XAUI 協議。

時鐘數據恢復

如圖8 所示, Altera 的高速CDR 電路使用混合體系結構,支持兩種工作模式,進一步發展了傳統的數據驅動體系結構。可以自動或者手動設置這兩種模式——鎖定至數據和鎖定至參考。采用參考時鐘作為輸入,將CDR 單元中的模擬PLL 鎖定到需要的頻率上。然后,電路從參考時鐘輸入切換到數據信號, CDR 和數據信號實現相位鎖定,從而恢復數據中的時鐘。這種體系結構的關鍵優勢在于縮短了鎖定時間,降低了功耗,能夠承受較大的抖動。結果, Altera 的收發器在驅動背板時,具有最低的抖動和最好的BER 性能,BER 達到10E–12 以上,而且協議兼容性非常好。

8

圖8. CDR 體系結構

時鐘產生和PLL 技術

?? 時鐘產生是高速收發器的一項重要功能。時鐘抖動會影響發射器和接收器的性能,從而影響高速鏈路的BER 性能。PLL 的關鍵組成是振蕩器,它是抖動的主要來源。理想情況下,高速壓控振蕩器(VCO) 提供較寬的調諧范圍,較高的頻率(GHz),較低的噪聲和功耗,體積很小,集成度較高。

?? Altera 的高速收發器支持兩類振蕩器,環行振蕩器(RO) 和LC諧振振蕩器(LC諧振腔)。RO的集成度較高,功耗也比較低,管芯面積較小,在較寬的調諧范圍內都具有優異的抖動性能,每一接收通道都有獨立的RO,工作范圍在600 Mbps 至10.3 Gbps。然而,隨著頻率的提高,相位噪聲和抖動性能出現劣化,當高頻時需要優異的相位噪聲和抖動性能時, LC 諧振振蕩器則顯示出很大的優勢。LC 諧振振蕩器的缺點是其電感和可變電容( 變容),這些都是體積較大的元件。

■ 發送通道RO

● 在較寬的頻率范圍內具有優異的抖動性能

● 600 Mbps 至10.3 Gbps 的數據工作范圍

■ 發送通道LC 諧振振蕩器

● 技術實現了較好的抖動性能,較窄的工作范圍。

● 4.9–6.375 Gbps LC 諧振振蕩器,適用于PCIe/CEI-6。

● 9.9–11.3 Gbps LC 諧振振蕩器 ,適用于XLAUI/CAUI/CEI-11G。

預加重和均衡

???? 所有傳輸介質普遍存在的一個問題是由頻率引起的損耗,特別是趨膚效應和電介質損耗導致的印刷電路板(PCB) 設計損耗。這種損耗導致高頻分量的衰減更大,從而降低了遠端信號的接收能力,縮短了驅動長度,增大了BER。預加重和均衡用在Altera 的高速收發器中,以克服傳輸損耗,驅動帶有兩個連接器的40"

FR-4 背板。

??? 在數據信號發送至通道之前,高速收發器的發射器采用預加重技術放大數據信號的高頻分量。由于所生成數據信號的前面和后續數據位在發射器中是確定的,因此,預加重方法應用在相對于主脈沖的不同數據位上。Altera 的預加重方案使用預抽頭,其后是主脈沖和兩個后抽頭。

??? 在接收器開始進行均衡,當數據進入接收器時,均衡起到了高通濾波器的功能,成功地重建信號。Altera的高速收發器支持各種均衡方案(4):

Altera 公司 采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計

9

■ 連續時間線性均衡(CTLE)

■ 自適應散射補償引擎(ADCE)(5)

■ 判定反饋均衡(DFE)

由于不同的數據速率和背板特性,因此,很難從數千種設置中選擇最佳均衡設置。使用收發器HSPICE 模型和背板S 參數特性進行仿真可以簡化這一過程。但是,某些應用在工作中需要插拔系統卡,當條件變化時,不得不迅速更新均衡設置。利用即插即用信號完整性功能, Altera 引入了ADCE,熱插拔收發器支持在40" FR-4 背板上2.5 Gbps 至6.5 Gbps 的數據傳輸。

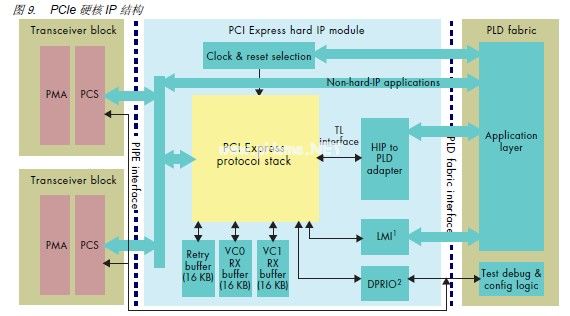

面向PCI Express 的硬核IP

??? PCIe 的廣泛應用推動了集成PCIe 功能的發展,在實際中它作為預驗證和符合標準的硬核IP 模塊來實現。

???? PCIe 的重要優勢是能夠大大節省資源( 最大40K LE),降低功耗,其編譯時間更短,從而縮短了設計周期。

如圖9 所示,硬核IP 模塊嵌入在PCIe 協議棧的所有層中,包括收發器模塊、物理層、數據鏈路層和協議層。PCIe 硬核IP 模塊符合以下PCI-SIG 規范:

■ PCIe 基本規范, Rev 1.1 (2.5 Gbps)

■ PCIe 基本規范, Rev 2.0 (2.5 和5.0 Gbps)

圖9. PCIe 硬核IP 結構

注釋:

(1) LMI:本地管理接口

(2) DPRIO:動態部分可重新配置輸入/ 輸出

Altera 的收發器系列器件

新器件的發展符合摩爾定律——密度每兩年加倍,開發新器件需要不同的方法,由于開發成本隨之增加,應盡量采用相關的技術。在開發全系列收發器FPGA 和ASIC 時, Altera 采用了以下方法:

■ 重新使用已有工藝所采用的技術

■ 通過技術進步,發揮每一新工藝節點的優勢來逐步改進。

10

■ 使用通用體系結構,綜合考慮不同的性能、功耗和成本要求,優化構建模塊。

■ 進行革命性的創新,以滿足重新使用已有技術所不能解決的需求。

系列產品組成

基于TSMC 的40-nm 工藝, Altera 采用了相同的成熟收發器體系結構來開發每一帶有收發器的FPGA 和ASIC,這種結構非常適合寬帶串行接口應用。在每個器件中,集成收發器模塊針對目標應用進行了優化。

Arria II GX FPGA

Arria? II GX FPGA 滿足了對成本和功耗敏感的應用,在低密度和中密度范圍內提供豐富的特性。最大收發器數據速率是3.75 Gbps,滿足了GPON、IP DSLAM、遠程射頻前端、廣播和橋接等中等性能應用領域對高速協議和寬帶的需求。收發器和I/O 經過優化,綜合考慮特性和性能,具有較高的性價比。雖然Arria IIGX FPGA 的固定功耗模式不具有可編程功耗技術的靈活性,但是,它大大降低了靜態功耗。Arria II GXFPGA 采用可編程預加重和均衡技術,適合背板應用,并且具有優異的信號完整性。由于只有速率較高的背板應用才需要ADCE 和DFE 等功能,為降低成本和功耗,該器件不支持這類功能。

Stratix IV GX FPGA

Stratix IV GX FPGA 提供最大的密度,最好的性能以及最低的功耗,收發器速率高達8.5 Gbps, 48 個收發器提高了帶寬,其豐富的功能可支持背板應用和高速協議。關鍵應用包括對性能要求較高的無線基站、40G/100G 應用、高端路由器和橋接應用。其優異的信號完整性保證了與PCIe Gen2 和CEI-6 等嚴格協議的兼容性。可編程功耗技術提高了設計中關鍵時序通路的性能,同時優化了性能較低部分的功耗。

HardCopy IV GX ASIC

HardCopy? IV GX ASIC 滿足了對成本和功耗敏感的大批量應用需求。其性能與用作原型開發器件的StratixIV GX FPGA 相當。這種獨特的設計方法基于采用了Quartus II 開發軟件的統一工具包, 實現了風險最低的ASIC,并且集成了6.5-Gbps 收發器。

Stratix IV GT FPGA

Stratix IV GX FPGA 滿足了40G/100G 應用需求,是需要10G 收發器功能的最佳解決方案。Stratix IV GTFPGA 具有Stratix IV GX FPGA 的密度、特性和性能優勢,同時集成了11.3-Gbps 收發器。這樣,可以實現MAC/ 成幀器、數據包處理和流量管理功能的最佳系統集成,并且具有可編程架構的產品及時面市優勢。需要很大帶寬的橋接應用也能夠受益于這些器件。Stratix IV GT 器件可以直接連接至光模塊,從而總體上實現了最低的系統成本和系統功能,大大降低了電路板復雜度。

通用IP 系列產品和開發環境

所有Altera 定制邏輯器件都具有效能優勢,包括統一全面的設計軟件,一組通用IP 內核,并提供各種參考設計和設計實例。

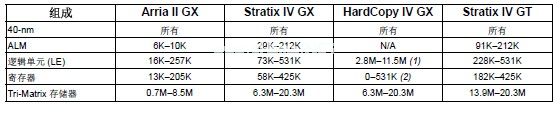

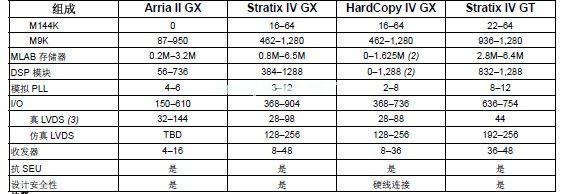

系列產品規范

本節對比收發器系列產品的關鍵標準技術規范,表2 突出介紹了通用體系結構組成。所有器件均支持全部

專用組成功能。

表2. Altera 器件的體系結構組成 11

11

注釋:

(1) 每LE 的ASIC 邏輯門數量以12 個進行計算;每個18x18 乘法器5000 個邏輯門。

(2) 采用HCell 進行構建。

(3) 全雙工對,包括接收和發送。

表3 在功耗和性能上對比了系列器件。

注釋:

(1) 低功耗(LP)/ 高性能(HP)

(2) 支持-2 內核和-3 I/O 速率等級。支持PCIe Gen1 和Gen2 x8。

(3) 未定的特性

M144K 0 16–64 16–64 22–64

M9K 87–950 462–1,280 462–1,280 936–1,280

MLAB 存儲器0.2M–3.2M 0.8M–6.5M 0–1.625M (2) 2.8M–6.4M

DSP 模塊56–736 384–1288 0–1,288 (2) 832–1,288

模擬PLL 4–6 3–12 2–8 8–12

I/O 150–610 368–904 368–736 636–754

真LVDS (3) 32–144 28–98 28–88 44

仿真LVDS TBD 128–256 128–256 192–256

收發器4–16 8–48 8–36 36–48

抗SEU 是是是是

設計安全性是是硬線連接是

表3. Altera 器件功耗和性能

功耗和性能Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT

可編程功耗技術(1) 僅LP LP/HP 不需要LP/HP

性能

速率等級-4, -5, -6 -2/-2x (2), -3, -4 N/A -1, -2, -3

時鐘500 MHz 600 MHz 600 MHz 600 MHz

DSP 350 MHz 550 MHz 495 MHz 550 MHz

內部存儲器390 MHz 550 MHz 500 MHz 550 MHz

LVDS

I/O 1 Gbps 1.6 Gbps 1.25 Gbps 1.6 Gbps

DPA 是是是是

存儲器

DDR 200 MHz 200 MHz 200 MHz 200 MHz

DDR2 300 MHz 400 MHz 400 MHz 400 MHz

DDR3 300 MHz 533 MHz 533 MHz (3) 533 MHz

QDRII 250 MHz 350 MHz 350 MHz 350 MHz

QDRII+ TBD 350 MHz 350 MHz 350 MHz

RLDRAMII TBD 400 MHz 400 MHz 400 MHz

表2. Altera 器件的體系結構組成

組成Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT

采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計Altera 公司

12

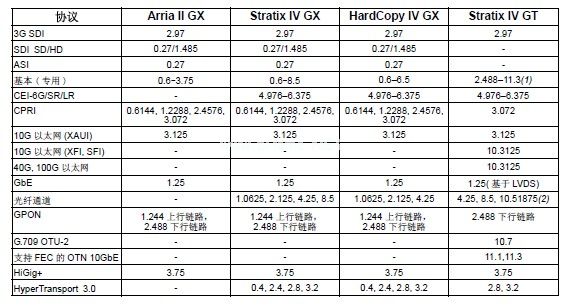

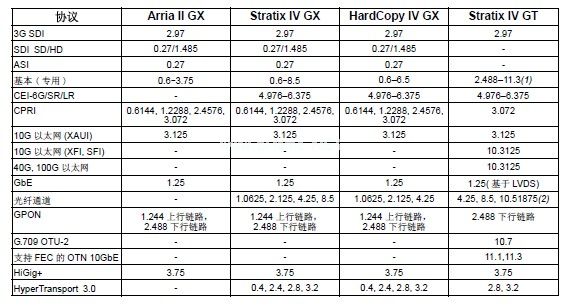

表4 主要介紹了高速收發器特性和性能。

注釋:

(1) 初步數據,有可能會改變。

(2) 0°C - 100°C

表5 列出了每一產品系列支持的協議和數據速率。

表4. Altera 的高速收發器特性和性能

特性Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT (1)

3G 收發器4–16 8–48 8–36 36–48

6G 收發器N/A 8–48 8–36 36–48

8.5G 收發器N/A 0–32 N/A 24–32

10G 收發器N/A N/A N/A 12–24

收發器總數4–16 8–48 8–36 36–48

最大數據速率(Gbps)

商用3.75 8.5 6.5+ 11.3

工業3.125 6.5 6.5 11.3 (2)

面向PCIe 的硬核IP 1 1–4 2 1 (1)

Gen Gen1 Gen1 和Gen2 Gen1 和Gen2 Gen1 和Gen2

通道寬度x1, x2, x4, x8 x1, x2, x4, x8 x1, x2, x4, x8 x1, x2, x4 (1)

均衡是是是是

預加重是是是是

ADCE N/A 是是是(1)

DFE N/A 是是是(1)

背板是是是是

最大數據速率3.75 Gbps 6.5 Gbps 6.5 Gbps 6.5 Gbps

表5. Altera 的高速協議和數據速率( 每通道Gbps)

協議Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT

3G SDI 2.97 2.97 2.97 2.97

SDI SD/HD 0.27/1.485 0.27/1.485 0.27/1.485 -

ASI 0.27 0.27 0.27 -

基本( 專用) 0.6-3.75 0.6-8.5 0.6–6.5 2.488–11.3(1)

CEI-6G/SR/LR - 4.976–6.375 4.976–6.375 4.976–6.375

CPRI 0.6144, 1.2288, 2.4576,

3.072

0.6144, 1.2288, 2.4576,

3.072

0.6144, 1.2288, 2.4576,

3.072

3.072

10G 以太網(XAUI) 3.125 3.125 3.125 3.125

10G 以太網(XFI, SFI) - - - 10.3125

40G,100G 以太網- - - 10.3125

GbE 1.25 1.25 1.25 1.25( 基于LVDS)

光纖通道- 1.0625, 2.125, 4.25, 8.5 1.0625, 2.125, 4.25 4.25, 8.5, 10.51875(2)

GPON 1.244 上行鏈路,

2.488 下行鏈路

1.244 上行鏈路,

2.488 下行鏈路

1.244 上行鏈路,

2.488 下行鏈路

2.488 下行鏈路

G.709 OTU-2 - - - 10.7

支持FEC 的OTN 10GbE - - - 11.1,11.3

HiGig+ 3.75 3.75 3.75 3.75

HyperTransport 3.0 - 0.4, 2.4, 2.8, 3.2 0.4, 2.4, 2.8, 3.2 2.8, 3.2

Altera 公司 采用帶有收發器的全系列40-nm FPGA 和ASIC 實現創新設計

13

注釋:

(1) 10G 基本( 專用)

(2) 10G 光纖通道

(3) 包括SFI-4.2 和SFI-5.1

(4) 10G SONET/SDH OC-192/STM-64

結論

?? 提高帶寬和數據速率需要更多、更快的收發器。各種標準、優異的背板信號完整性和協議要求推動了數字器件的收發器創新發展。為滿足不同市場和應用的各類需求,數字器件必須在密度和特性上達到最佳組合,同時滿足性能、功耗和成本目標。Altera 的40-nm 收發器FPGA 和ASIC 技術創新以及重新使用已有技術滿足了這些需求,提供了最全面的收發器定制邏輯系列產品。

?? 采用了相同的成熟收發器體系結構來開發Altera 所有的40-nm 收發器FPGA 和ASIC,這種體系結構適合寬帶串行接口應用。在每一器件中,針對目標應用優化了集成收發器模塊。Arria II GX FPGA 是低功耗、高性價比FPGA 系列,大大簡化了3.75-Gbps 收發器解決方案的實現。Stratix IV GX FPGA 是高性能器件,具有530K LE 和高級收發器,提供較大的存儲器帶寬。Stratix IV GT FPGA 是唯一集成了11.3-Gbps 收發器的FPGA,適合40G 和100G 應用。HardCopy IV GX ASIC 是封裝和引腳與Stratix IV GX FPGA 相匹配的ASIC,有助于降低帶有嵌入式收發器ASIC 設計的風險和總成本。此外,所有Altera 的定制邏輯器件都具有效能優勢,包括統一全面的設計軟件,一組通用知識產權(IP) 內核,并提供各種參考設計和設計實例。

表5. Altera 的高速協議和數據速率( 每通道Gbps)

協議Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT

14

????? 版權? 2009 Altera 公司。保留所有版權。Altera、可編程解決方案公司、程式化Altera 標識、專用器件名稱和所有其他專有商標或者服務標記,除非特別聲明,均為Altera 公司在美國和其他國家的商標和服務標記。所有其他產品或者服務名稱的所有權屬于其各自持有人。Altera 產品受美國和其他國家多種專利、未決應用、掩模著作權和版權的保護。Altera 保證當前規范下的半導體產品性能與Altera 標準質保一致,但是保留對產品和服務在沒有事先通知時的變更權利。除非與Altera 公司的書面條款完全一致,否則Altera 不承擔由使用或者應用此處所述信息、產品或者服務導致的責任。Altera 建議客戶在決定購買產品或者服務,以及確信任何公開信息之前,閱讀Altera 最新版的器件規范說明。

101 Innovation Drive

San Jose, CA 95134

詳細信息

致謝

■ Bernhard Friebe,產品營銷經理, Altera 公司。

■ Rishi Chugh,產品營銷經理,低成本FPGA, Altera 公司。

■ Kevin Cackovic,戰略營銷高級經理,通信業務部, Altera 公司。

■ Martin Lee,戰略營銷高級經理,通信業務部, Altera 公司。

■ Martin Won,技術組資深成員,產品營銷, Altera 公司。

■ Mike Peng Li,博士,首席設計師/ 高級工程師,產品工程, Altera 公司。

■ Sergey Shumarayev,工程主管,模擬設計組, Altera 公司。

電子發燒友App

電子發燒友App

評論