利用串行RapidIO實(shí)現(xiàn)FPGA協(xié)處理

為了支持“三重播放”應(yīng)用,人們對高速通信和超快速計(jì)算的需求日益增大,這向系統(tǒng)開發(fā)師、算法開發(fā)師和硬件工程師等人員提出了新的挑戰(zhàn),要求他們將各種標(biāo)準(zhǔn)、組件和聯(lián)網(wǎng)設(shè)備融合成一個(gè)整體

?????? 同時(shí),開發(fā)人員不但要跟上日益提高的性能需求,還得注意保持成本低廉 有效利用基于串行RapidIO的FPGA作為DSP協(xié)處理器就能達(dá)到這些目的

有效利用基于串行RapidIO的FPGA作為DSP協(xié)處理器就能達(dá)到這些目的

由于三重播放應(yīng)用集合了話音、視頻和數(shù)據(jù)應(yīng)用,因此必須采用新算法來設(shè)定其開發(fā)和系統(tǒng)優(yōu)化策略的參數(shù) 其間,開發(fā)人員要解決以下問題:構(gòu)造可調(diào)整可擴(kuò)展的架構(gòu)、支持分布式處理、采用基于標(biāo)準(zhǔn)的設(shè)計(jì),以及針對性能和成本進(jìn)行優(yōu)化

其間,開發(fā)人員要解決以下問題:構(gòu)造可調(diào)整可擴(kuò)展的架構(gòu)、支持分布式處理、采用基于標(biāo)準(zhǔn)的設(shè)計(jì),以及針對性能和成本進(jìn)行優(yōu)化

仔細(xì)研究一下就會(huì)發(fā)現(xiàn),為滿足應(yīng)用需求而要、面對的這些挑戰(zhàn)主要涉及兩個(gè)主題:一是連接性,從本質(zhì)上說就是實(shí)現(xiàn)不同設(shè)備、板卡和系統(tǒng)之間的“快速”數(shù)據(jù)轉(zhuǎn)移;二是計(jì)算能力,指設(shè)備、板卡和系統(tǒng)中分別可用的處理資源

??????? 運(yùn)算平臺(tái)之間的連接

基于標(biāo)準(zhǔn)的設(shè)計(jì)通常比“自由發(fā)揮”的設(shè)計(jì)簡單得多,也是今天的典型設(shè)計(jì)模式 并行連接標(biāo)準(zhǔn)(PCI、PCI-X、EMIF等)雖能滿足當(dāng)前需求,但若考慮到可調(diào)整性和可擴(kuò)展性就有所不足了

并行連接標(biāo)準(zhǔn)(PCI、PCI-X、EMIF等)雖能滿足當(dāng)前需求,但若考慮到可調(diào)整性和可擴(kuò)展性就有所不足了 隨著分組處理技術(shù)的不斷進(jìn)步,連接標(biāo)準(zhǔn)的發(fā)展趨勢顯然傾向于高速串行連接

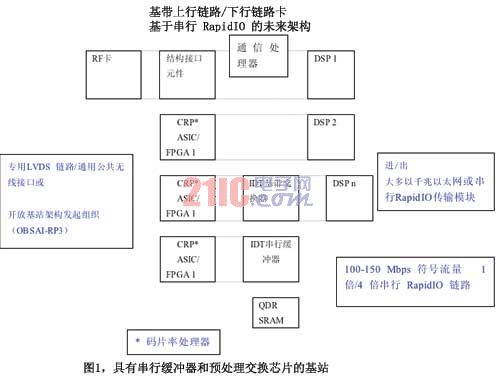

隨著分組處理技術(shù)的不斷進(jìn)步,連接標(biāo)準(zhǔn)的發(fā)展趨勢顯然傾向于高速串行連接 從圖1中就能看出這一趨勢

從圖1中就能看出這一趨勢

諸如PCIe和GbE/XAUI之類的高速串行標(biāo)準(zhǔn)在臺(tái)式機(jī)和網(wǎng)絡(luò)行業(yè)已有應(yīng)用 但無線通信設(shè)施中的數(shù)據(jù)處理系統(tǒng)對互連方面的要求又稍有不同,它要求:

但無線通信設(shè)施中的數(shù)據(jù)處理系統(tǒng)對互連方面的要求又稍有不同,它要求:

1. 管腳數(shù)少;

2. 需進(jìn)行底板以及芯片到芯片的連接;

3. 帶寬和速度可調(diào);

4. 具備DMA和消息傳遞功能;

5. 支持復(fù)雜可調(diào)整的拓?fù)洌?br />

6. 支持多點(diǎn)傳送;

7. 高度可靠;

8. 支持當(dāng)日時(shí)間(time of day)同步;

9. 可提供服務(wù)質(zhì)量(QoS)

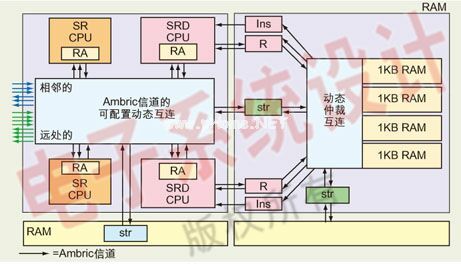

????????????????????????????? 圖1:向串行連接的發(fā)展趨勢

串行RapidIO (SRIO)協(xié)議標(biāo)準(zhǔn)可輕松滿足以上大部分要求,甚至超出這些要求的標(biāo)準(zhǔn) 因此,串行RapidIO已成為無線通信基礎(chǔ)設(shè)備中用于數(shù)據(jù)層(data plane)互連的主流連接技術(shù)

因此,串行RapidIO已成為無線通信基礎(chǔ)設(shè)備中用于數(shù)據(jù)層(data plane)互連的主流連接技術(shù) SRIO網(wǎng)絡(luò)建立在兩個(gè)“基本模塊”基礎(chǔ)之上:端點(diǎn)設(shè)備(Endpoint)和交換設(shè)備(Switch)

SRIO網(wǎng)絡(luò)建立在兩個(gè)“基本模塊”基礎(chǔ)之上:端點(diǎn)設(shè)備(Endpoint)和交換設(shè)備(Switch) 端點(diǎn)設(shè)備負(fù)責(zé)收發(fā)數(shù)據(jù)包,交換設(shè)備負(fù)責(zé)在端口之間傳遞數(shù)據(jù)包,但不負(fù)責(zé)數(shù)據(jù)包的解釋

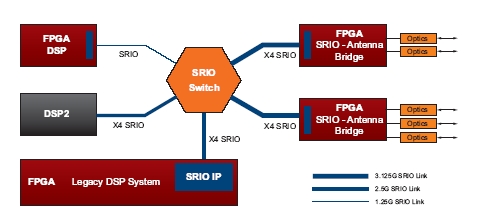

端點(diǎn)設(shè)備負(fù)責(zé)收發(fā)數(shù)據(jù)包,交換設(shè)備負(fù)責(zé)在端口之間傳遞數(shù)據(jù)包,但不負(fù)責(zé)數(shù)據(jù)包的解釋 圖2給出了SRIO網(wǎng)絡(luò)的構(gòu)建模塊

圖2給出了SRIO網(wǎng)絡(luò)的構(gòu)建模塊

???????????????????????????????????????? 圖2:SRIO網(wǎng)絡(luò)的構(gòu)建模塊

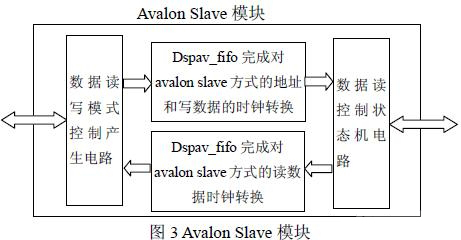

按規(guī)范定義,串行RapidIO有用3層架構(gòu),如圖3所示

??????????????????????????????????????????????????? 圖3:SRIO架構(gòu)

????? 其中包含:

??????? 物理層——負(fù)責(zé)描述器件級(jí)接口規(guī)范,例如分組傳輸機(jī)制、流量控制、電特性以及低級(jí)錯(cuò)誤管理

??????? 傳輸層——為在不同端點(diǎn)設(shè)備之間傳送分組提供路由信息 交換設(shè)備以基于器件的路由方式工作于傳輸層

交換設(shè)備以基于器件的路由方式工作于傳輸層

??????? 邏輯層——定義總體的協(xié)議和分組格式 每個(gè)分組最多包含256字節(jié)的載荷

每個(gè)分組最多包含256字節(jié)的載荷 事務(wù)通過Load、Store或DMA操作來訪問大小為34/50/66比特的地址空間

事務(wù)通過Load、Store或DMA操作來訪問大小為34/50/66比特的地址空間

SRIO有多種優(yōu)點(diǎn) 一個(gè)運(yùn)行于3.125 Gbps的4通道SRIO鏈路能在完全保持?jǐn)?shù)據(jù)完整性的前提下提供10 Gbps的流量

一個(gè)運(yùn)行于3.125 Gbps的4通道SRIO鏈路能在完全保持?jǐn)?shù)據(jù)完整性的前提下提供10 Gbps的流量 SRIO與微處理器總線類似,它在硬件中完成存儲(chǔ)器和器件尋址以及分組處理

SRIO與微處理器總線類似,它在硬件中完成存儲(chǔ)器和器件尋址以及分組處理 這不但大大降低了用于I/O處理的開銷,減小了延遲,也增大了其相對于其他總線接口的系統(tǒng)帶寬

這不但大大降低了用于I/O處理的開銷,減小了延遲,也增大了其相對于其他總線接口的系統(tǒng)帶寬 但與大多數(shù)其他總線接口不同的是,SRIO接口的引腳數(shù)很少,而且其基于高速串行鏈路的可調(diào)整帶寬可在1.25 - 3.125 Gbps范圍內(nèi)調(diào)整

但與大多數(shù)其他總線接口不同的是,SRIO接口的引腳數(shù)很少,而且其基于高速串行鏈路的可調(diào)整帶寬可在1.25 - 3.125 Gbps范圍內(nèi)調(diào)整 圖4為SRIO規(guī)范的圖解

圖4為SRIO規(guī)范的圖解

????????????????????????????????????????????? 圖4:SRIO規(guī)范

?????? 平臺(tái)中的運(yùn)算資源

有了可配置的處理資源,開發(fā)人員就可以用硬件實(shí)現(xiàn)他們的應(yīng)用,例如數(shù)據(jù)壓縮和加密算法 甚至過去只在軟件中實(shí)現(xiàn)的整套防火墻和保密應(yīng)用,如今都可以在硬件上實(shí)現(xiàn)

甚至過去只在軟件中實(shí)現(xiàn)的整套防火墻和保密應(yīng)用,如今都可以在硬件上實(shí)現(xiàn) 但這樣做需要具備共享帶寬和強(qiáng)大處理能力的大型并行生態(tài)系統(tǒng),也就是說,要求利用CPU、NPU、FPGA和/或ASIC進(jìn)行共享式或分布式處理

但這樣做需要具備共享帶寬和強(qiáng)大處理能力的大型并行生態(tài)系統(tǒng),也就是說,要求利用CPU、NPU、FPGA和/或ASIC進(jìn)行共享式或分布式處理 構(gòu)建此類系統(tǒng)時(shí),對運(yùn)算資源的一些要求包括:

構(gòu)建此類系統(tǒng)時(shí),對運(yùn)算資源的一些要求包括:

??????1. 支持復(fù)雜拓?fù)涞姆植际教幚砟芰Γ?

??????2. 高度可靠的直接對等通信能力;?

??????3. 多個(gè)異構(gòu)操作系統(tǒng);?

??????4. 通過多個(gè)異構(gòu)操作系統(tǒng)支持通信數(shù)據(jù)層;?

??????5. 具有廣泛生態(tài)系統(tǒng)支持的模塊化和可擴(kuò)展平臺(tái)

SRIO協(xié)議規(guī)范和架構(gòu)支持嵌入式和無線基礎(chǔ)設(shè)施領(lǐng)域中運(yùn)算設(shè)備的不同要求 有了SRIO,就可以實(shí)現(xiàn)系統(tǒng)結(jié)構(gòu)的獨(dú)立性,部署達(dá)到運(yùn)營商級(jí)可靠度、具備高級(jí)流量管理功能,并具有高性能和高吞吐量的可擴(kuò)展系統(tǒng)

有了SRIO,就可以實(shí)現(xiàn)系統(tǒng)結(jié)構(gòu)的獨(dú)立性,部署達(dá)到運(yùn)營商級(jí)可靠度、具備高級(jí)流量管理功能,并具有高性能和高吞吐量的可擴(kuò)展系統(tǒng) 此外,廣泛的供應(yīng)商生態(tài)系統(tǒng)也更方便設(shè)計(jì)師采用現(xiàn)貨元件構(gòu)造SRIO系統(tǒng)

此外,廣泛的供應(yīng)商生態(tài)系統(tǒng)也更方便設(shè)計(jì)師采用現(xiàn)貨元件構(gòu)造SRIO系統(tǒng) SRIO是一種基于分組的協(xié)議,它支持:

SRIO是一種基于分組的協(xié)議,它支持:

?????? 1. 采用分組操作(包括讀、寫和消息傳遞)實(shí)現(xiàn)數(shù)據(jù)搬移;?

??????2. I/O非一致性功能和緩存一致性功能;?

??????3. 通過支持?jǐn)?shù)據(jù)流傳送和SAR功能實(shí)現(xiàn)高效的互通和協(xié)議封裝;?

??????4. 通過支持?jǐn)?shù)百萬條數(shù)據(jù)流、256種流量類別和有損操作實(shí)現(xiàn)一種流量管理架構(gòu);?

??????5. 支持多事務(wù)請求流(包括配置QoS)的流量控制;?

??????6. 為減少帶寬分配、事務(wù)預(yù)定和死鎖避免等問題而支持優(yōu)先級(jí)劃分;?

??????7. 通過系統(tǒng)發(fā)現(xiàn)、配置和學(xué)習(xí)實(shí)現(xiàn)對標(biāo)準(zhǔn)拓?fù)?樹型和網(wǎng)格型)和任意拓?fù)?菊鏈)等多種硬件拓?fù)浞绞降闹С郑ㄖС侄鄠€(gè)主機(jī);?

??????8. 錯(cuò)誤管理和分類(可恢復(fù)、通知和嚴(yán)重)

??????串行RapidIO的IP方案

為了在通過邏輯(I/O)和傳輸層IP上的目標(biāo)接口和源接口收發(fā)用戶數(shù)據(jù)時(shí)支持完全兼容的最大載荷操作,Xilinx等廠商根據(jù)最新的RapidIO v1.3規(guī)范設(shè)計(jì)了其端點(diǎn)IP解決方案

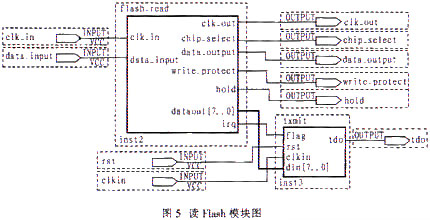

圖5所示是Xilinx的一套完整的SRIO端點(diǎn)IP方案,它包含以下組成部分:

??????1. LogiCORE RapidIO 邏輯 (I/O)和傳輸層IP;?

??????2. 緩沖層參考設(shè)計(jì);?

??????3. LogiCORE串行RapidIO物理層IP;?

??????4. 寄存器管理器參考設(shè)計(jì)

??????????? 圖5:Xilinx的 SRIO端點(diǎn)IP架構(gòu)

?????? IP架構(gòu)

Xilinx提供了緩沖層參考設(shè)計(jì)的源代碼,該設(shè)計(jì)可完成分組的自動(dòng)排隊(duì)和優(yōu)先級(jí)重新劃分 SRIO物理層IP可以實(shí)現(xiàn)鏈路訓(xùn)練和初始化、發(fā)現(xiàn)和管理以及錯(cuò)誤與重試恢復(fù)機(jī)制

SRIO物理層IP可以實(shí)現(xiàn)鏈路訓(xùn)練和初始化、發(fā)現(xiàn)和管理以及錯(cuò)誤與重試恢復(fù)機(jī)制 此外,在該物理層IP中還對高速收發(fā)器進(jìn)行了實(shí)例化,以便支持線速為1.25Gbps、2.5Gbps和3.125Gbps 的1通道和4通道SRIO總線連接

此外,在該物理層IP中還對高速收發(fā)器進(jìn)行了實(shí)例化,以便支持線速為1.25Gbps、2.5Gbps和3.125Gbps 的1通道和4通道SRIO總線連接

該方案中提供的寄存器管理器參考設(shè)計(jì)允許SRIO主設(shè)備對端點(diǎn)設(shè)備配置、鏈路狀態(tài)、控制和超時(shí)機(jī)制進(jìn)行配置和維護(hù) 另外,該寄存器管理器還提供了可讓用戶設(shè)計(jì)探測端點(diǎn)設(shè)備狀態(tài)的端口

另外,該寄存器管理器還提供了可讓用戶設(shè)計(jì)探測端點(diǎn)設(shè)備狀態(tài)的端口

LogiCORE則提供了完整的端點(diǎn)IP 該IP已通過業(yè)界領(lǐng)先SRIO器件廠商的測試

該IP已通過業(yè)界領(lǐng)先SRIO器件廠商的測試 用戶可通過Xilinx CoreGen GUI工具獲得LogiCORE

用戶可通過Xilinx CoreGen GUI工具獲得LogiCORE CoreGen工具可以幫助用戶配置波特率和端點(diǎn)

CoreGen工具可以幫助用戶配置波特率和端點(diǎn) LogiCORE支持流量控制、重傳抑制、門鈴和消息傳遞等擴(kuò)展特性

LogiCORE支持流量控制、重傳抑制、門鈴和消息傳遞等擴(kuò)展特性 因此,用戶可以創(chuàng)建一套專門針對應(yīng)用需求優(yōu)化了的靈活、可調(diào)整和定制化的SRIO端點(diǎn)IP

因此,用戶可以創(chuàng)建一套專門針對應(yīng)用需求優(yōu)化了的靈活、可調(diào)整和定制化的SRIO端點(diǎn)IP

利用Xilinx和其他廠商提供的大多數(shù)高性能FPGA中的各種資源,系統(tǒng)設(shè)計(jì)師就能輕松創(chuàng)建并部署其智能方案,以增強(qiáng)產(chǎn)品在上市時(shí)間、可調(diào)整性、可擴(kuò)展性、適應(yīng)未來發(fā)展等各方面的優(yōu)勢 下面給出了一些采用SRIO和DSP技術(shù)的系統(tǒng)設(shè)計(jì)實(shí)例

下面給出了一些采用SRIO和DSP技術(shù)的系統(tǒng)設(shè)計(jì)實(shí)例

??????? SRIO系統(tǒng)應(yīng)用實(shí)例

1.嵌入式系統(tǒng):像x86這樣的CPU結(jié)構(gòu)是針對那些無需進(jìn)行大量乘法運(yùn)算的一般應(yīng)用優(yōu)化過的 相比而言,DSP結(jié)構(gòu)則是針對包括濾波、FFT、矢量乘法和查找以及圖像或視頻分析等信號(hào)處理操作優(yōu)化過的

相比而言,DSP結(jié)構(gòu)則是針對包括濾波、FFT、矢量乘法和查找以及圖像或視頻分析等信號(hào)處理操作優(yōu)化過的

因此,同時(shí)采用CPU和DSP的嵌入式系統(tǒng)可以輕松利用通用處理器和信號(hào)處理器兩種結(jié)構(gòu)的優(yōu)勢 圖6給出了一個(gè)此類系統(tǒng)的例子,其中同時(shí)包含F(xiàn)PGA、CPU和DSP架構(gòu)

圖6給出了一個(gè)此類系統(tǒng)的例子,其中同時(shí)包含F(xiàn)PGA、CPU和DSP架構(gòu)

???????????? 圖6:基于CPU的高性能DSP子系統(tǒng)

在高端DSP中,串行RapidIO已成為主流數(shù)據(jù)互連方式 x86 CPU中主要的數(shù)據(jù)互連則采用PCI Express實(shí)現(xiàn)

x86 CPU中主要的數(shù)據(jù)互連則采用PCI Express實(shí)現(xiàn) 如圖6所示,對FPGA進(jìn)行一些簡單的配置,就能用它調(diào)整DSP應(yīng)用的規(guī)模,和/或橋接幾種完全不同的互連標(biāo)準(zhǔn)(如PCI Express 和串行RapidIO)

如圖6所示,對FPGA進(jìn)行一些簡單的配置,就能用它調(diào)整DSP應(yīng)用的規(guī)模,和/或橋接幾種完全不同的互連標(biāo)準(zhǔn)(如PCI Express 和串行RapidIO)

在該系統(tǒng)中,管理PCI Express系統(tǒng)的是Root Complex芯片組,SRIO系統(tǒng)則受一塊DSP管理 PCIe的32/64位地址空間(基地址)可自動(dòng)映射至34/66位SRIO地址空間(基地址)PCIe應(yīng)用程序通過內(nèi)存或I/O讀寫與Root Complex芯片組通信這些事務(wù)均可通過流寫入、原語和確認(rèn)讀/寫事務(wù)(SWRITEs

PCIe的32/64位地址空間(基地址)可自動(dòng)映射至34/66位SRIO地址空間(基地址)PCIe應(yīng)用程序通過內(nèi)存或I/O讀寫與Root Complex芯片組通信這些事務(wù)均可通過流寫入、原語和確認(rèn)讀/寫事務(wù)(SWRITEs ATOMIC

ATOMIC NREADs

NREADs NWRITE/NWRITE_Rs)等I/O操作輕松映射至SRIO空間

NWRITE/NWRITE_Rs)等I/O操作輕松映射至SRIO空間

在Xilinx的FPGA中設(shè)計(jì)此類橋接功能非常簡單,因?yàn)镻CI Express的后端接口和串行RapidIO端點(diǎn)的功能模塊是類似的分組隊(duì)列模塊隨后就可以實(shí)現(xiàn)從PCIe到SRIO或從SRIO向PCIe的轉(zhuǎn)換,從而在這兩個(gè)協(xié)議域之間建立數(shù)據(jù)流

2.DSP處理應(yīng)用:在那些DSP處理是主要架構(gòu)要求的應(yīng)用中,系統(tǒng)結(jié)構(gòu)可按圖7所示方式設(shè)計(jì)

?????????? 圖7:需要強(qiáng)大DSP處理能力的器件

???????? Xilinx Virtex-5 FPGA在該系統(tǒng)中就可用作其他DSP器件的協(xié)處理器如果用SRIO進(jìn)行數(shù)據(jù)互連,這整套DSP系統(tǒng)方案還可輕松實(shí)現(xiàn)調(diào)整這樣的方案具備可擴(kuò)展性,適應(yīng)未來的發(fā)展,而且還能以多種外形尺寸實(shí)現(xiàn)

當(dāng)需要強(qiáng)大DSP功能的應(yīng)用還需要進(jìn)行快速大量的復(fù)雜運(yùn)算或數(shù)據(jù)處理時(shí),可以將這些處理任務(wù)卸載至x86 CPU中去運(yùn)行Xilinx Virtex-5 FPGA允許對PCIe子系統(tǒng)和SRIO結(jié)構(gòu)進(jìn)行橋接,從而實(shí)現(xiàn)高效的功能卸載

3. 基帶處理系統(tǒng)

?????? 隨著3G網(wǎng)絡(luò)快速成熟,OEM廠商將會(huì)采用新的外形尺寸的器件和設(shè)備來減少容量和覆蓋方面的問題,使用SRIO并基于FPGA的DSP架構(gòu)正是應(yīng)對此類挑戰(zhàn)的絕佳方案傳統(tǒng)DSP系統(tǒng)也可重新調(diào)整為這種快速低功耗的基于FPGA的結(jié)構(gòu),以便充分利用FPGA的可調(diào)整性優(yōu)勢

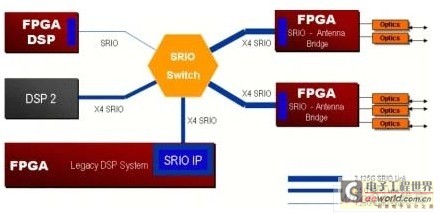

在此類系統(tǒng)中,如圖8所示,F(xiàn)PGA可以在滿足天線業(yè)務(wù)線速處理要求的同時(shí)通過SRIO為其他系統(tǒng)資源提供連接而由于串行RapidIO協(xié)議提供的速度和帶寬均很高,所以那些內(nèi)部固有低速并行連接的現(xiàn)存?zhèn)鹘y(tǒng)DSP應(yīng)用要移植到這類系統(tǒng)中也很簡單

??? 圖8:基帶處理

?????? 本文小結(jié)

?????? 串行RapidIO正在越來越多的新應(yīng)用中嶄露頭角,特別是在采用DSP的有線和無線應(yīng)用中在Xilinx器件中實(shí)現(xiàn)串行RapidIO主要有以下優(yōu)勢:?

???????1. Xilinx提供了完整的SRIO端點(diǎn)方案;?

???????2. 可利用同樣的軟、硬件結(jié)構(gòu),通過靈活的調(diào)整,實(shí)現(xiàn)不同類型的產(chǎn)品;?

???????3. 由于Xilinx器件采用了新型GTP收發(fā)機(jī)和65nm 技術(shù),因此功耗很低;?

???????4. 通過CoreGen GUI 可實(shí)現(xiàn)方便的可配置性和靈活性;?

???????5. 由于業(yè)界領(lǐng)先的廠商都有器件支持SRIO連接,因而硬件互通性有保證;?

???????6. 可通過使用PCIe和TEMAC等集成IO模塊實(shí)現(xiàn)系統(tǒng)集成,從而降低系統(tǒng)整體成本

電子發(fā)燒友App

電子發(fā)燒友App

評論