基于EDA仿真技術(shù)解決FPGA設(shè)計(jì)開(kāi)發(fā)中故障的方法

FPGA近年來(lái)在越來(lái)越多的領(lǐng)域中應(yīng)用,很多大通信系統(tǒng)(如通信基站等)都用其做核心數(shù)據(jù)的處理。但是過(guò)長(zhǎng)的編譯時(shí)間,在研發(fā)過(guò)程中使得解決故障的環(huán)節(jié)非常令人頭痛。本文介紹的就是一種用仿真方法解決故障從而減少研發(fā)過(guò)程中的編譯次數(shù),最終達(dá)到準(zhǔn)確定位故障、縮短解決故障時(shí)間的目的。文例所用到的軟件開(kāi)發(fā)平臺(tái)為Altera公司的Quartus II,仿真工具為ModelSim。本文針對(duì)FPGA實(shí)際開(kāi)發(fā)過(guò)程中,出現(xiàn)故障后定位困難、反復(fù)修改代碼編譯時(shí)間過(guò)長(zhǎng)、上板后故障解決無(wú)法確認(rèn)的問(wèn)題,提出了一種采用仿真的方法來(lái)定位、解決故障并驗(yàn)證故障解決方案。可以大大的節(jié)約開(kāi)發(fā)時(shí)間,提高開(kāi)發(fā)效率。

問(wèn)題的提出

系統(tǒng)開(kāi)發(fā)在上板調(diào)試過(guò)程中,有時(shí)候出現(xiàn)的bug是很極端的情況或很少出現(xiàn)的情況,而現(xiàn)在通常的做法是:在故障出現(xiàn)的時(shí)候通過(guò)SignalTap 把信號(hào)抓出來(lái)查找其問(wèn)題的所在、修改程序;在改完版本后,先要對(duì)整個(gè)工程進(jìn)行重新編譯,然后再上板跑版本進(jìn)行驗(yàn)證,看看故障是否解決。

這樣就會(huì)出現(xiàn)三個(gè)問(wèn)題:

①有時(shí)候故障很難定位,只知道哪個(gè)模塊出錯(cuò),很難定位到具體的信號(hào)上,給抓信號(hào)帶來(lái)麻煩。如果故障定位不準(zhǔn)確,漏抓了關(guān)鍵信號(hào),則需要重新在 SignalTap里添加信號(hào)、編譯版本并再次上板定位故障,浪費(fèi)時(shí)間。

②故障定位后,修改代碼還需要再編譯一次產(chǎn)生新版本的下載文件,修改后若還有問(wèn)題則要重復(fù)這一過(guò)程,這樣從故障定位到修改完成需要很多次編譯。

③上板重新進(jìn)行驗(yàn)證時(shí),如果這個(gè)bug的出現(xiàn)的幾率很小,短時(shí)間內(nèi)不再?gòu)?fù)現(xiàn),并不能說(shuō)明在極端情況下的故障真的被解決了。

舉例說(shuō)明:

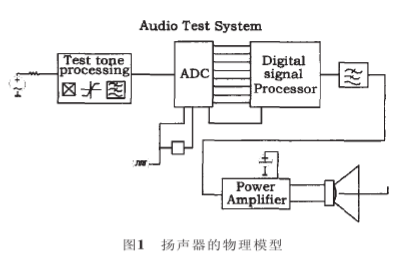

例如在一個(gè)基帶系統(tǒng)的FPGA邏輯版本中,輸出模塊調(diào)用了一個(gè)異步FIFO,某一時(shí)刻FIFO已空的情況下多讀了一個(gè)數(shù)據(jù),產(chǎn)生了bug,如圖 1所示。

圖1 SignalTap抓出的bug出現(xiàn)時(shí)的數(shù)據(jù)

該輸出模塊的功能是判斷FIFO中是否有大于4個(gè)數(shù)據(jù)可讀出,若大于則連續(xù)輸出4個(gè)數(shù)據(jù)作為一組。系統(tǒng)中采用異步FIFO的內(nèi)部讀數(shù)據(jù)指針來(lái)做判斷,而異步FIFO讀寫(xiě)數(shù)據(jù)需要跨時(shí)鐘域,需要至少2個(gè)時(shí)鐘周期的握手時(shí)間,導(dǎo)致數(shù)據(jù)指針不準(zhǔn)確。在判斷的時(shí)鐘沿,雖然顯示有超過(guò)4個(gè)的數(shù)據(jù)可讀,但是因?yàn)槲帐謺r(shí)間的延遲實(shí)際上FIFO中可能只有3個(gè)數(shù)據(jù)。

圖1中rdreq為FIFO的讀使能信號(hào),在4個(gè)時(shí)鐘周期內(nèi)有效,但是只讀出了3個(gè)數(shù)(數(shù)據(jù)0D2086C9F被讀了兩次),因?yàn)镕IFO在第 4個(gè)時(shí)鐘周期已經(jīng)讀空。這里應(yīng)該改成同步FIFO,由于同步FIFO數(shù)據(jù)的讀寫(xiě)只在一個(gè)時(shí)鐘域內(nèi)進(jìn)行,就沒(méi)有這個(gè)握手時(shí)間延遲的問(wèn)題了。

定位這個(gè)故障的時(shí)候我們可以很容易知道是哪個(gè)模塊出了問(wèn)題,但是具體是其內(nèi)部的哪個(gè)信號(hào)還需要下些功夫,如果出錯(cuò)信號(hào)隱藏的很深,很難一次就抓到需要的信號(hào);而且即使我們抓到了正確的信號(hào),如果故障在改完之后沒(méi)有解決,則還需要重新修改、再進(jìn)行編譯,耗費(fèi)時(shí)間;即使改過(guò)之后故障不再?gòu)?fù)現(xiàn),也有可能是因?yàn)閎ug出現(xiàn)的條件苛刻,無(wú)法證明故障真的解決了。

針對(duì)這三個(gè)問(wèn)題,筆者提出如下想法:

雖然定位具體的出錯(cuò)信號(hào)很困難,但是定位是哪個(gè)模塊出錯(cuò)很容易,在bug出現(xiàn)的時(shí)候我們可以抓出這個(gè)模塊的全部輸入信號(hào),考慮是否可以利用這些信號(hào)在仿真環(huán)境下重建bug出現(xiàn)的條件,利用仿真環(huán)境具體定位錯(cuò)誤信號(hào)的位置。

定位好錯(cuò)誤信號(hào)的具體位置后,修改代碼,再用相同的條件進(jìn)行仿真。這樣可以通過(guò)對(duì)修改前后輸出數(shù)據(jù)的對(duì)比,很直觀的驗(yàn)證修改是否成功,從而在修改成功后只需編譯一次即可,節(jié)省時(shí)間。

上板后bug不復(fù)現(xiàn)也可以排除是由于極端情況很難滿(mǎn)足造成的,去除了后顧之憂(yōu),徹底解決了故障。

仿真解決故障的方法

通過(guò)對(duì)這個(gè)異步FIFO問(wèn)題的解決,可以證明這種通過(guò)所抓信號(hào)建立bug存在條件,定位、清除bug的方法是可行的。步驟如下:

①將bug出現(xiàn)時(shí)SignalTap抓的信號(hào)保存成文檔文件

Quartus II 平臺(tái)用SignalTap抓到信號(hào)的界面如圖2所示。

圖2 SignalTap抓信號(hào)界面

在信號(hào)名稱(chēng)上單擊右鍵,選擇圖2所示Create SignalTap II List File選項(xiàng),生成如圖3格式界面。

圖3 SignalTap II List File界面

圖3中界面上半部分顯示的是list對(duì)信號(hào)個(gè)數(shù)及信號(hào)名的描述,下半部分是采樣點(diǎn)所對(duì)應(yīng)的信號(hào)值,帶h的表示是十六進(jìn)制數(shù)值。

將list file另存為文本格式文件即可,如圖4所示。

圖4 “另存為”選項(xiàng)界面

此后可以把這個(gè)文本文件中無(wú)用的描述刪掉,只留SignalTap抓出來(lái)的數(shù)據(jù)(空格、h等符號(hào)也要?jiǎng)h掉),另存為.dat文件供仿真使用。

有了故障出現(xiàn)時(shí)的輸入數(shù)據(jù),我們就可以在仿真環(huán)境下構(gòu)建故障出現(xiàn)的條件。

②利用.dat文件建立bug出現(xiàn)的條件

用verilog語(yǔ)言編寫(xiě)仿真文件(testbench),使用語(yǔ)句$readmemh或$readmemb將.dat文件中的數(shù)據(jù)存儲(chǔ)到一個(gè)設(shè)定的ram中,如:$readmemh(“s.dat”,ram)。

注意$readmemh讀取是按照十六進(jìn)制數(shù)據(jù)進(jìn)行(認(rèn)為.dat文件中的數(shù)據(jù)都是十六進(jìn)制數(shù)),會(huì)自動(dòng)將其轉(zhuǎn)換為4位二進(jìn)制數(shù)存入ram中,所以設(shè)定的ram位寬要是.dat文件中數(shù)據(jù)位寬的4倍;使用$readmemb時(shí),存儲(chǔ)SignalTap所抓信號(hào)時(shí),信號(hào)都要先設(shè)定為binary類(lèi)型,ram位寬就是.dat文件數(shù)據(jù)的位寬。ram的深度為.dat文件中數(shù)據(jù)的個(gè)數(shù)。

然后在程序里把ram中數(shù)據(jù)按照所對(duì)應(yīng)時(shí)鐘沿輸出到一個(gè)寄存器變量中,ram地址累加即可。

always@(posedge clk)

begin

data<=ram[addr];

addr<=addr+1'b1;

end

復(fù)現(xiàn)bug存在條件時(shí),需將模塊的輸入信號(hào)與ram中的數(shù)據(jù)位相對(duì)應(yīng),仿真文件調(diào)用模塊時(shí),將寄存器data對(duì)應(yīng)位作為輸入接入即可。

在仿真環(huán)境中復(fù)現(xiàn)bug波形如圖5所示。

圖5 ModelSim環(huán)境下復(fù)現(xiàn)的出錯(cuò)數(shù)據(jù)

把圖5和圖1進(jìn)行比較,可見(jiàn)通過(guò)這種方法我們?cè)诜抡姝h(huán)境下建立了bug出錯(cuò)時(shí)的環(huán)境,得到相同的輸出出錯(cuò)數(shù)據(jù)。

③修改程序后在仿真環(huán)境驗(yàn)證修改是否成功

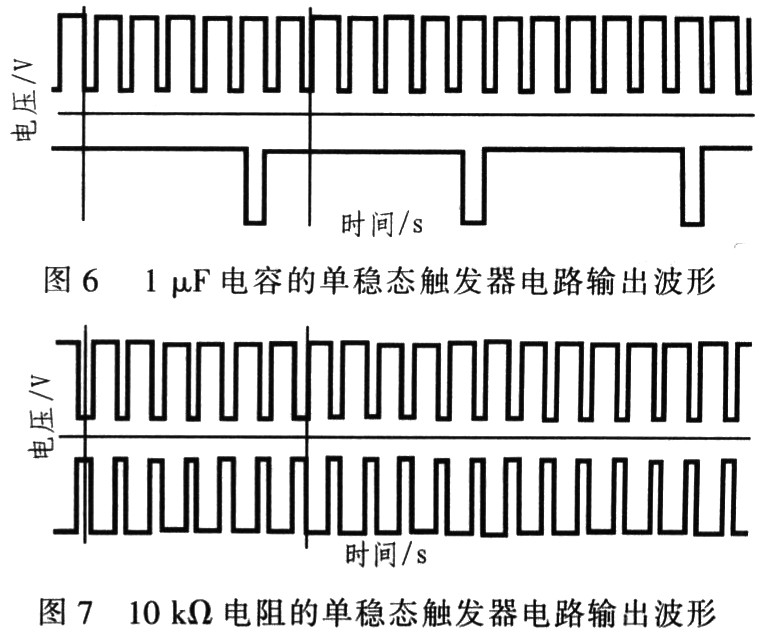

修改程序后,我們只要使用同樣的環(huán)境進(jìn)行仿真,并且有針對(duì)性的觀察bug是否解決。本例中出現(xiàn)bug的原因是使用了異步FIFO,改成同步 FIFO后,問(wèn)題應(yīng)該就會(huì)解決,我們可以通過(guò)仿真驗(yàn)證。修改程序后仿真的波形如圖6所示。

圖6 修改程序后相同條件下的輸出數(shù)據(jù)

由圖6可見(jiàn),修改后相同的條件FIFO讀出4個(gè)數(shù),說(shuō)明沒(méi)有讀空,符合要求,bug解決。圖7為版本編譯后上板使用SignalTap抓取的信號(hào)波形,以作比較。

圖7 修改程序后SignalTap抓的信號(hào)

比較后易見(jiàn),波形完全相同,說(shuō)明方法可行。

總結(jié)

文中描述的方法可針對(duì)各種的故障的解決。在故障出現(xiàn)時(shí),只需定位出錯(cuò)的模塊,這些模塊內(nèi)嵌一些子模塊也無(wú)妨;抓信號(hào)時(shí)將故障模塊的輸入輸出信號(hào)抓出即可;利用輸入信號(hào)重建故障環(huán)境,若仿真輸出信號(hào)和所抓輸出信號(hào)相同,說(shuō)明故障環(huán)境建立正確;用這個(gè)仿真平臺(tái)就可以具體定位是哪個(gè)子模塊、哪個(gè)信號(hào)出錯(cuò),而不需要在SignalTap中把這些信號(hào)抓出來(lái);并且在修改代碼后可以驗(yàn)證是否修改成功,節(jié)省時(shí)間,很明確的證明故障真的被解決了,事半功倍。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論