自適應濾波算法的研究始于20世紀50年代末,Widrow和Hoff等人最早提出最小均方算法(LMS)。算法由于結構簡單,計算量小,易于實時處理,因此在噪聲抵消,譜線增強,系統識別等方面得到了廣泛的應用。為了克服定步長LMS算法中收斂速度、收斂精度及跟蹤速度等對步長大小選取相互矛盾的缺點,人們提出了許多變步長LMS算法,但是,當輸入信號具有強相關性時,例如語音信號,LMS算法及NLMS算法的收斂速度將急劇下降。因此,本文對進入自適應濾波器的輸入信號首先進行解相關預處理,再對自適應濾波器進行歸一化LMS。

很多自適應濾波器是在通用DSP處理器上通過編寫軟件代碼實現。這種濾波器在系統實時性要求不高的情況下,能很好地滿足濾波要求,但在實時性要求較高的場合(如3G移動通信,網絡會議等),這種濾波器在處理速度和抗干擾性能等方面已不能滿足要求。而用FPGA硬件實現的數字濾波器就能很好的解決并行性和速度問題,而且其具有靈活的可配置特性和優良的抗干擾能力,因而自適應濾波器的FPGA實現成為近年來數字濾波器中研究的熱點。Altera公司開發的DSP Builder可以完成FPGA的DSP系統設計,它結合Matlab/Simulink提供的庫元件和強大的計算仿真能力,進行圖形建模和仿真,還可以完成從Simulink模塊文件向VHDL語言的自動轉換。

1 算法概述

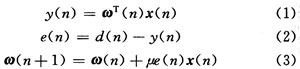

在標準LMS算法中,其迭代公式如下:

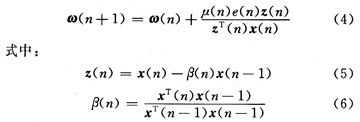

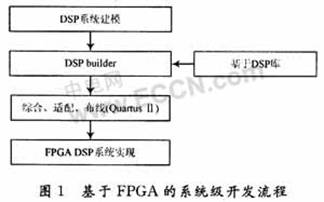

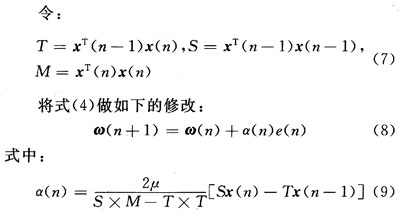

式中:ω(n)為自適應濾波器在時刻n的權矢量;x(n)為時刻n的輸入信號矢量;d(n)為參考信號;e(n)是誤差信號;μ是步長迭代因子,為了增加LMS算法的收斂速度,文獻[1-4]提出了不同的變步長算法代替定步長因子μ,但是很多變步長因子的計算量大,存在開方和指數運算,故在能滿足要求的情況下,歸一化LMS (NLMS)依然是一個很好的選擇,即用μn/[xT(n)x(n)]代替定步長因子μ為了控制失調,在更新公式中引入一個固定的收斂因子μn,這是因為所有的倒數都是基于平方誤差的瞬時值而不是均方誤差(MSE)。對于NLMS算法,當輸入信號具有強相關性時,LMS算法及NLMS算法的收斂速度將急劇下降。因此對進入自適應濾波器的輸入信號首先進行解相關預處理,再對自適應濾波器進行歸一化LMS,便得解相關歸一化LMS(DNLMS)即用式(4)代替式(3):

2 基于FPGA的系統開發流程

在早期PFGA的DSP系統設計過程中,DSP開發者直接使用VHDL或Verilog HDL語音進行開發。這種開發難度較大,開發效率較低,為了克服這些問題,出現了許多新的基于FPGA的DSP開發工具,如Altera公司的DSP Builder、Xilinx公司的System Generator等。圖1是Altera公司的FPGA系統級開發流程。

DSP Builder是Altera公司推出的一個面向DSP開發的系統級工具。它是作為Matlab/Simuli-nk的一個工具箱出現的。它從利用Matlab建立DSP電路模型開始。電路模型可方便地利用Simulink與DSPBuilder中提供的功能模塊和IP核進行設計。電路中的功能模塊和IP的技術參數、數據格式、數據類型和總線寬度等都能直接設置。電路模型建立后就能進行系統級的仿真。仿真通過后可以運行Signal Compiler,將模型轉化成RTL級的VHDL代碼和Tcl(工具命令語言)腳本語言。調用QuartusⅡ進行編譯,QuartusⅡ根據網表文件及設置的優化約束條件進行布線布局和優化設計的適配,最后生成編程文件和仿真文件。

3 系統建模與仿真

根據DNLMS算法的思想,結合FPGA硬件設計的特點。

NLMS算法主要包括延時模塊,乘法模塊,加法模塊,除法模塊等。為了讓整個系統看起來清晰,降低原理圖的復雜性,也便于多次應用,本文將幾個多次使用的模塊封裝成子模塊。下面將對各個子模塊作簡單的介紹。

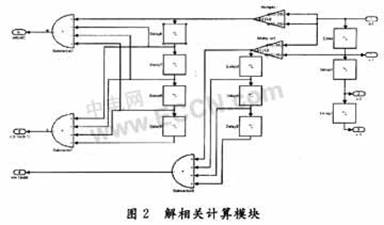

根據算法的要求,每次新的數據x(n)輸入,數據T,S,M都需要重新更新一次,計算量大,消耗的乘法塊多。為了解決這個問題。根據T,S,M的運算特點,每次更新只需要一個乘法塊和一次加法,就能完成8次乘法和一次加法的運算。具體子模塊如圖2所示。

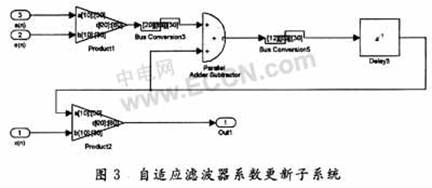

通過圖2的優化,對于8階濾波器,乘法塊的使用從24個減少到2個,計算速度將得到很大的提高。ω的迭代運算通過圖3實現。

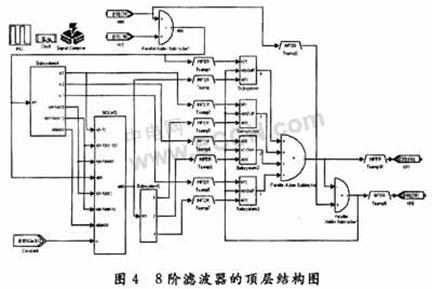

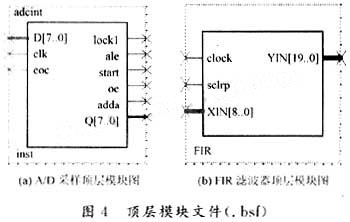

在頂層模塊的設計中,加入了PLL模塊和SignalComplier,根據各模塊仿真周期,在PLL模塊中設置好不同的周期,利用Simulink中的顏色標識采樣頻率的高低。頂層文件的設計如圖4所示。

在頂層結構圖中,子模塊8為方程(9)的實現過程。

4 計算機仿真

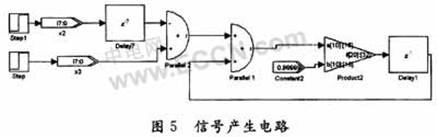

為了充分模擬相關性較強的信號,在輸入端加如下的信號源:

x(n)=0.99x(n-1)+v(n)

式中:v(n)為高斯白噪聲;x(n)的初始值為500,具體的產生電路如圖5所示。

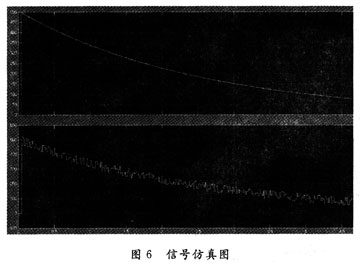

信號產生波形以及加噪后的仿真波形如圖6所示。

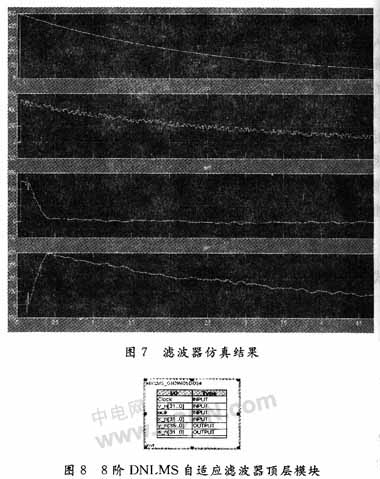

通過濾波器濾波的結果如圖7所示。

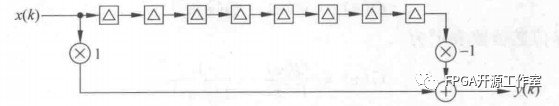

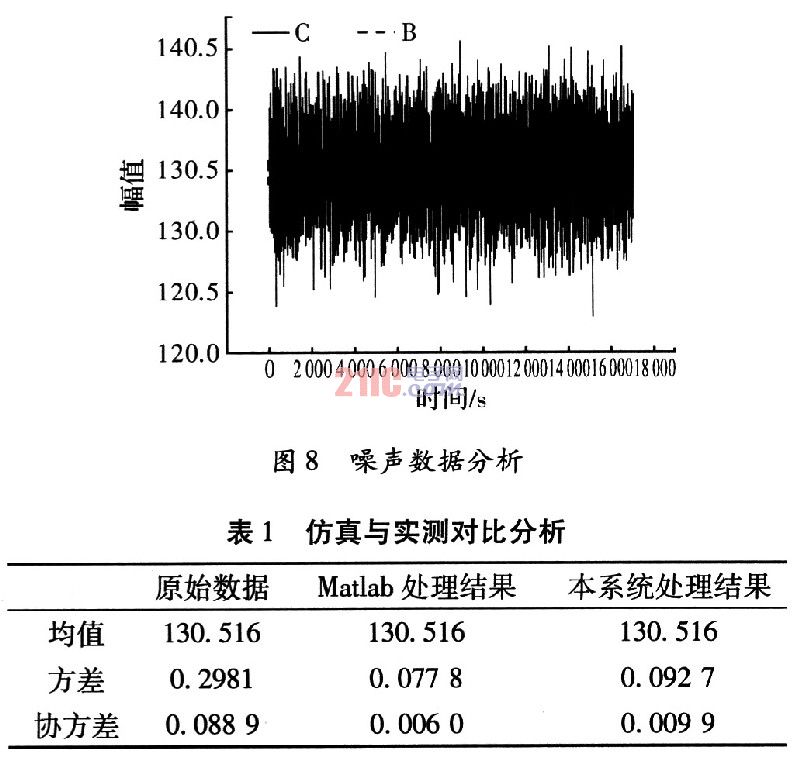

在圖7的信號依次為參考信號、加噪聲信號、誤差信號和濾波信號。濾波效果良好,對于強相關的信號,也有很好的濾波效果。通過QuartusⅡ編譯,濾器器的速度為35.24 MHz,編譯后生產如圖8所示的塊,它作為一個符號模塊可供更高級系統設計時調用,通過對該塊的修改和增加濾波器的階數,可以實現對語音的回聲消除。

5?結? 語

自適應濾波器的研究是近年來研究的熱門方向,在PFGA中實現高速的自適應濾波器的設計更是一個熱點,在此采用DSP Builder系統建模的方法,在FPGA中實現了歸一化LMS算法,實驗結果表明:用DSPBuilder設計的8階DNLMS算法比用底層的VHDL代碼設計效率更高,靈活性更大,速度更快。同樣比通用的DSP芯片設計的8階NLMS濾波器處理速度快了20多倍。如果將8階NLMS濾波器擴展到512階或者1 024階,可以很好地應用于自適應回聲消除等很多自適應濾波的領域。故有一定的參考價值。

DNLMS濾波器的FPGA實現

- 濾波器(174522)

- DNLMS(6068)

相關推薦

基于FPGA的IIR數字帶通濾波器的設計方案及實現

本方案利用FPGA實現了巴特沃茲IIR數字帶通濾波器,并給出較為詳細的方案設計過程。實驗結果證明了所設計的濾波器完全滿足預定設計要求,從而也證實了本方案的有效性、可行性。

2014-02-13 10:58:32 6684

6684

6684

6684梳狀濾波器以及積分梳狀濾波器的FPGA實現

sample rate convert 和 down sample rate convert 的FPGA實現打下基礎。 1 梳狀濾波器 圖1 梳狀濾波器結構 梳狀濾波器的兩端為1和-1的權值,具有簡單

2020-11-21 09:57:00 5220

5220

5220

5220

FPGA怎樣調用IP核實現FIR低通濾波器設計?

剛接觸FPGA,想用EP4CE6F17C8這個型號的altera芯片實現低通濾波器設計,我看能直接調用IP實現,但是網上的資料都是調用MATLAB生成濾波器所需的系數,還只是用于仿真,但是我想用

2017-08-04 19:25:28

fpga實現濾波器

本帖最后由 eehome 于 2013-1-5 10:03 編輯

fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點

2012-08-11 18:27:41

fpga實現濾波器

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

實現FPGA數字下變頻的多類濾波器分組級聯技術分析

實現FPGA數字下變頻的多類濾波器分組級聯技術分析1 引 言 本文針對以下高效算法做了總結,進行合理的分組級聯并引入流水線技術以便于在FPGA上實現。數字下變頻(DDC)就是通過混頻、抽取和濾波等

2009-10-23 10:26:53

CIC抽取濾波器MATLAB仿真和FPGA實現

CIC抽取濾波器MATLAB仿真和FPGA實現(1)設計理想濾波器目標:1、濾波器在有效頻段內紋波滿足設計要求。2、抽取或內插處理后在有效頻段內不產生混疊。3、濾波器實現簡單,需要資源較少。這個

2021-08-17 08:27:40

FTR濾波器_濾波器原理_有限脈沖響應濾波器_明德揚fpga

FIR濾波器工程說明本案例設計了一個15階的低通線性相位FIR濾波器,采用布萊克曼窗函數設計,截止頻率為500HZ,采樣頻率為2000HZ;實現全串行結構的濾波器;采用具有白噪聲特性的輸入信號,以及

2017-08-02 17:35:24

fir濾波器的設計和實現

對于fir濾波器,已經在前面的文章中記錄了仿制DIY&關于MATLAB中濾波器設計工具的使用心得記錄),其設計和實現都非常簡單。如果在嵌入式系統中可以滿足且有必要實時iir運算,那么

2021-12-22 08:29:40

一個基于FPGA的FIR濾波器的問題

最近在做一個FPGA的課程設計,遇到一個比較煩人的問題,希望大神們可以指點迷律。一個16階的FIR濾波器,采用分布式算法實現的,采樣率1M,fc=100K,頻率到了30K以上時就會出現那些尖刺,很

2018-02-25 19:25:50

低通濾波器的FPGA設計及仿真

主要任務:1.熟悉低通濾波器的原理及應用2.熟悉FPGA的硬件描述3.FPGA如何實現小數分頻器4.用MATLAB對低通濾波器的驗證預期成果或目標:FPGA對低通濾波器的Verilog(或VHDL

2013-04-04 22:16:11

基于51單片機和FPGA的程控濾波器的實現方案

以單片機和可編程邏輯器件(FPGA)為控制核心,設計了一個程控濾波器,實現了小信號程控放大、程控調整濾波器截止頻率和幅頻特性測試的功能。其中放大模塊由可變增益放大器AD603實現,最大增益60dB

2019-09-29 14:08:52

基于FPGA的DDC濾波器該怎么設計?

設計一般采用CIC、HB、FIR級聯的形式組成。同時,由于CIC濾波器的通帶性能實在太差,所以中間還要加上一級PFIR濾波器以平滑濾波器的通帶性能。

2019-09-20 06:13:11

基于FPGA的FIR濾波器設計與實現

本帖最后由 eehome 于 2013-1-5 09:50 編輯

基于FPGA的FIR濾波器設計與實現 文章研究基于FPGA、采用分布式算法實現FIR濾波器的原理和方法,用

2012-08-11 15:32:34

基于FPGA的IIR數字濾波器的設計和實現方法介紹

數字濾波器、DSP器件或可編程邏輯器件(如FPGA)實現。因為,用FPGA實現數字濾波器具有實時性強、靈活性高、處理速度快以及小批量生產成本低等優點,所以得到了較為廣泛的應用。本文以巴特沃思數字

2019-07-08 07:18:25

基于AccelDSP的自適應濾波器設計

【作者】:袁江南;湯碧玉;陳輝煌;【來源】:《廈門大學學報(自然科學版)》2010年02期【摘要】:給出了一種自適應濾波器的設計和FPGA的實現方法.簡要分析了最小均方誤差(LMS)、歸一化最小均方

2010-04-24 09:01:12

基于中檔FPGA的多相濾波器設計

的邏輯、需要較少的計算資源、更低的功耗,并減少了可能的飽和/溢出。可用如今新型的小規模、中檔的FPGA,如LatticeECP3 來實現這些濾波器。

2019-07-08 08:01:03

如何用FPGA來實現濾波器的設計

濾波器在FPGA中的實現用FPGA來實現濾波器的設計優點用FPGA來設計濾波器,不但設計簡單,而且成本小,可靠性好。且無需像傳統的設計芯片一樣進行測試。主要優點:設計簡潔。若設計有誤,則只需

2021-07-30 07:03:10

如何設計基于中檔FPGA多相濾波器?

使用了較少的邏輯、需要較少的計算資源、更低的功耗,并減少了可能的飽和/溢出。可用如今新型的小規模、中檔的FPGA,如LatticeECP3 來實現這些濾波器。

2019-10-22 06:55:44

如何采用FPGA實現多種類型的數字信號處理濾波器?

濾波器是任何信號處理系統的關鍵組成部分,隨著現代應用的日趨復雜,濾波器設計的復雜程度也日益提高。采用 FPGA 設計和實現的高性能濾波器的能力是模擬方法所望塵莫及的。另外,采用FPGA

2019-09-18 08:28:47

并行FIR濾波器Verilog設計

型、頻率取樣型、格型四種。其中最適合FPGA實現的是直接型。“直接”是指直接由卷積公式得到:由上圖可知,n階FIR濾波器就需要n個乘法器。如果設計的是線性相位FIR,則h(n)是對稱的,利用對稱性可以

2020-09-25 17:44:38

怎么用XC2V1000型FPGA實現FIR抽取濾波器的設計

本文以實現抽取率為2的具有線性相位的3階FIR抽取濾波器為例,介紹了一種用XC2V1000型FPGA實現FIR抽取濾波器的設計方法。

2021-05-07 06:02:47

求一本《數字濾波器的MATLAB與FPGA實現電子書》

大家好,想學點FPGA數字濾波,求一本電子書----------《數字濾波器的MATLAB與FPGA實現》,大家如果有這本電子書,請給我一份,謝謝!本人郵箱 361063571@qq.com

2017-08-09 14:17:06

求一本電子書----------《數字濾波器的MATLAB與FPGA實現》

大家好,想學點FPGA數字濾波,求一本電子書----------《數字濾波器的MATLAB與FPGA實現》,大家如果有這本電子書,請給我一份,謝謝!本人郵箱 xy163hxing@163.com

2016-02-12 19:27:56

零基礎學FPGA (二十九)濾波器開篇,線性相位FIR濾波器的FPGA實現

利用matlab設計一個線性相位FIR帶通濾波器,并在FPGA上實現。要求:1、濾波器指標:過渡帶帶寬分別為100~300HZ,500~700HZ,阻帶允許誤差為0.02,通帶允許誤差為0.01,采樣

2015-06-16 19:25:35

零基礎學FPGA(三十) IIR數字濾波器的FPGA實現筆記

現設計濾波器并不是很難和FIR濾波器一樣,我先把濾波器要求說明一下,然后再按照設計要求進行設計四、IIR濾波器的matlab設計與FPGA實現 要求設計一個IIR低通數字濾波器,要求:: 1、 設計成

2015-07-26 21:44:21

自適應LMS濾波器在FPGA中的實現

本文介紹了自適應濾波器的實現方法,給出了基于LMS 算法自適應濾波器在FPGA 中的實現,簡單介紹了這種實現方法的各個功能模塊,主要包括輸入信號的延時輸出模塊、控制模塊

2009-09-14 15:51:00 34

34

34

34基于FPGA對稱型FIR濾波器的設計與實現

基于FPGA對稱型FIR濾波器的設計與實現:在基于FPGA的對稱型FIR數字濾波器設計中,為了提高速度和運行效率,提出了使用線性I相位結構和加法樹乘法器的方法,并利用Altera公I司的FPG

2009-09-25 15:38:38 30

30

30

30基于FPGA的高精度浮點IIR濾波器設計

本文詳細討論了利用新版本FPGA 輔助設計軟件QuartusII6.0 中提供的浮點運算功能模塊實現IIR 濾波器的方法,與采用FPGA 的乘法模塊的同類設計相比,此濾波器設計結構簡單,容易擴

2009-12-19 15:44:27 38

38

38

38級聯梳狀積分濾波器的原理及FPGA實現

在軟件無線電的下變頻模塊中,級聯梳狀積分濾波器有著重要的應用,其主要作用是信號的抽取與低通濾波。文中總結了級聯梳狀積分抽取濾波器的理論要點,并介紹了采用FPGA

2010-01-06 15:16:45 31

31

31

31基于FPGA的程控濾波器設計與實現

設計一個由現場可編程門陣列(FPGA)控制的濾波器。該濾波器主要由3個模塊組成:前置放大、濾波電路、FPGA顯示與控制電路等利用FPGA作為放大器及程控濾波器電路中繼電器組的控制模

2010-07-17 18:00:09 45

45

45

45IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器

IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器

摘 要:本文介紹了一種采用級聯結構在FPGA上實現任意階IIR數字濾波器的方法。此

2008-01-16 09:45:39 2276

2276

2276

2276高效FIR濾波器的設計與仿真-基于FPGA

高效FIR濾波器的設計與仿真-基于FPGA

摘要:該文在介紹有限沖激響應(FIR)數字濾波器理論及常見實現方法的基礎上,提出了一種基于FPGA的高效實現方案。

2008-01-16 09:56:02 1456

1456

1456

1456如何用用FPGA實現FIR濾波器

如何用用FPGA實現FIR濾波器

你接到要求用FPGA實現FIR濾波器的任務時,也許會想起在學校里所學的FIR基礎知識,但是下一步該做什么呢?哪些參數是重

2009-03-30 12:25:45 4503

4503

4503

4503

CPLD基于FPGA實現FIR濾波器的研究

摘要: 針對在FPGA中實現FIR濾波器的關鍵--乘法運算的高效實現進行了研究,給了了將乘法化為查表的DA算法,并采用這一算法設計了FIR濾波器。通過FPGA仿零點驗證

2009-06-20 14:09:36 677

677

677

677

FIR帶通濾波器的FPGA實現

FIR帶通濾波器的FPGA實現

引 言??? 在FPGA應用中,比較廣泛而基礎的就是數字濾波器。根據其單位沖激響應函數的時域特性可分為無限沖擊響應(Infinite

2009-11-13 09:55:18 6564

6564

6564

6564

基于多速率DA的根升余弦濾波器的FPGA實現

基于多速率DA的根升余弦濾波器的FPGA實現

0 引 言 根升余弦成形濾波器是數字信號處理中的重要部件,它能對數字信號進行成形濾波,壓縮旁瓣,減少

2009-11-13 09:59:54 1518

1518

1518

1518

基于FPGA的數字濾波器的設計與實現

基于FPGA的數字濾波器的設計與實現

在信息信號處理過程中,如對信號的過濾、檢測、預測等,都要使用到濾波器,數字濾波器是數字信號處理中使用最廣泛的一

2010-01-07 10:45:35 3475

3475

3475

3475

FPGA的Kalman濾波器的設計

FPGA的Kalman濾波器的設計

摘要:針對電路設計中經常碰到數據的噪聲干擾現象,提出了一種Kalman濾波的FPGA實現方法。該方法采用了TI公司的高精度模數轉換

2010-04-13 13:32:46 2566

2566

2566

2566

自適應Notch濾波器的FPGA實現

摘要: 針對水下目標跟蹤定位系統中信號的特點, 采用自適應Notch 濾波器對接收信號進行檢測, 使系統在低信噪 比的情況下仍能保證較高的正確檢測率。提出了用FPGA 實現Notch 濾波器的硬件電路方案, 用DDS 技術解決了 Notch 濾波器的正交參考源的輸入問題, 簡化

2011-02-17 16:00:14 69

69

69

69CIC抽取濾波器的改進及其FPGA的實現

為補償傳統CIC濾波器的通帶衰減,提出一種改進型的CIC抽取濾波器,即在SCIC濾波器之后級聯一個二階多項式內插濾波器。基于硬件實現的要求,給出改進型CIC濾波器的FPGA高效實現原理圖。仿真結果表明改進的CIC濾波器具有更好的通阻帶特性。

2011-03-15 14:06:35 52

52

52

52基于W78E58與FPGA的程控濾波器設計

基于 W78E58 單片機和FPGA 模塊, 利用MAX262 芯片, 實現了具有程控濾波器, 包括信號幅頻特性測試、濾波參數設置及顯示輸出等功能的數字濾波器設計。

2011-08-04 15:49:55 54

54

54

54基于MATLAB和FPGA的CIC濾波器的設計

基于多速率信號處理原理,設計了用于下變頻的CIC抽取濾波器,由于CIC濾波器結構只用到加法器和延遲器,沒有乘法器,很適合用FPGA來實現,所以本文分析了CIC濾波器的原理,性能及影

2011-08-26 15:12:11 160

160

160

160高階音頻均衡濾波器的FPGA實現

文中設計的均衡濾波器充分利用FPGA內部資源、時間換取空間的方法,在EP1C3系列的FPGA內實現1 024階FIR數字均衡濾波器,并通過重載系數,可實現多種頻率響應的均衡特性、簡易數字均衡濾波

2011-10-19 15:23:48 38

38

38

38基于FPGA實現高插入CIC濾波器

為了產生調制信號的碼元速率能在大范圍內實時可變,采用插值濾波技術 多級積分梳狀濾波器。在分析多級濾波器的結構和特性的基礎上,闡述了一種利用剪除理論實現多級濾波器的高效

2011-12-26 18:33:08 25

25

25

25基于FPGA設計的FIR濾波器的實現與對比

描述了基于FPGA的FIR濾波器設計。根據FIR的原理及嚴格線性相位濾波器具有偶對稱的性質給出了FIR濾波器的4種結構,即直接乘加結構、乘法器復用結構、乘累加結構、DA算法。在本文中給

2012-11-09 17:32:37 121

121

121

121基于FPGA的DDC中CIC濾波器的設計

文中基于多速率數字信號處理原理,設計了用于數字下變頻技術的CIC抽取濾波器。通過分析CIC濾波器的原理及性能參數,利用MATLAB設計了符合系統要求的CIC濾波器,并通過FPGA實現了CI

2013-04-15 19:29:28 71

71

71

71基于FPGA的32階FIR濾波器的設計與實現

研究了一種采用FPGA實現32階FIR濾波器硬件電路方案;討論了窗函數的選擇、濾波器的結構以及系數量化問題;研究了FIR濾波器的FPGA實現,各模塊的設計以及如何優化硬件資源,提高運行

2017-11-10 16:41:57 15

15

15

15數字下變頻中抽取濾波器的設計及FPGA實現

ISE 12.3在Xilinx xc5vsx95t-2ff1136 FPGA上實現了一種下采樣率為64的抽取濾波器。Modelsim仿真結果表明,該抽取濾波器設計是有效的,達到了設計指標。

2017-11-17 09:01:55 5303

5303

5303

5303基于單圖像向導濾波器的整數FPGA設計結構

的使用,同時以整數數據處理方式實現了向導濾波器中方差和變換系數的計算,并且通過參數調整,可以方便地實現不同大小圖像的不同尺寸窗口的向導濾波。在Altera公司Cyclone系列FPGA芯片上進行了綜合,實驗結果表明,向導濾波整數FPGA結構的處理結果與

2017-11-22 15:43:12 12

12

12

12FIR濾波器的FPGA設計與實現

,結合MATLAB軟件提供的專用數字濾波器設計工具包FDATOOL,以及QuartusⅡ軟件提供的FIR核實現快速、便捷的設計FIR濾波器的幾個具體實驗,得出結論證實了熟練使用FDATOOL工具和FIR核比直接編寫代碼設計FIR濾波器更加方便、快捷,但編寫代碼具有靈活性更強的優勢。

2017-12-21 14:53:14 14

14

14

14FPGA的FIR抽取濾波器設計教程

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2018-04-28 11:50:00 1073

1073

1073

1073

基于FPGA的可調FIR濾波器在實際通信系統中的實現方法設計

基于靈活自適應的空口波形技術FOFDM(Filtered OFDM)是現代通信技術的研究熱點,設計并實現可調FIR濾波器是實現該技術的核心工作之一。本文設計的基于FPGA的可調節FIR濾波器系數

2018-07-23 17:21:00 2372

2372

2372

2372

如何使用FPGA實現FIR抽取濾波器的設計

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2020-09-25 10:44:00 3

3

3

3怎么樣使用FPGA設計ADC數字抽取濾波器

針對Σ△ADC輸出端存在的高頻噪聲問題,設計了一種 Sinc數字抽取濾波器,實現了Σ-△調制器輸出信號的高頻濾波。分析了Sinc濾波器的結構原理,基于 Spartan6FPGA進行濾波器的設計與實現

2020-08-26 17:12:00 14

14

14

14使用FPGA實現自適應卡爾曼濾波器的設計論文說明

在視頻圖像獲取過程中“由于噪聲對圖像序列的降質”需要設計實時噪聲濾波器。討論了視頻圖像的卡爾曼濾波問題及自適應卡爾曼濾波算法“并討論了自適應卡爾曼濾波算法的簡化”以利于硬件實現自適應卡爾曼濾波器“并進行了簡化算法仿真”完成基于FPGA實現的實時自適應卡爾曼濾波器的設計。

2021-01-22 14:29:29 22

22

22

22使用FPGA實現自適應卡爾曼濾波器的設計論文說明

在視頻圖像獲取過程中“由于噪聲對圖像序列的降質”需要設計實時噪聲濾波器。討論了視頻圖像的卡爾曼濾波問題及自適應卡爾曼濾波算法“并討論了自適應卡爾曼濾波算法的簡化”以利于硬件實現自適應卡爾曼濾波器“并進行了簡化算法仿真”完成基于FPGA實現的實時自適應卡爾曼濾波器的設計。

2021-01-22 14:29:29 13

13

13

13如何使用FPGA實現分布式算法的高階FIR濾波器

提出一種新的高階FIR濾波器的FPGA實現方法。該方法運用多相分解結構對高階FIR濾波器進行降階處理,采用改進的分布式算法來實現降階后的FIR濾波器。設計了一系列階數從8到1 024的FIR濾波器

2021-03-23 15:44:54 30

30

30

30串行FIR濾波器MATLAB與FPGA實現

本文介紹了設計濾波器的FPGA實現步驟,并結合杜勇老師的書籍中的串行FIR濾波器部分進行一步步實現硬件設計,對書中的架構做了簡單的優化,并進行了仿真驗證。

2023-05-24 10:56:34 552

552

552

552

并行FIR濾波器MATLAB與FPGA實現

本文介紹了設計濾波器的FPGA實現步驟,并結合杜勇老師的書籍中的并行FIR濾波器部分進行一步步實現硬件設計,對書中的架構做了復現以及解讀,并進行了仿真驗證。

2023-05-24 10:57:36 653

653

653

653

電子發燒友App

電子發燒友App

評論