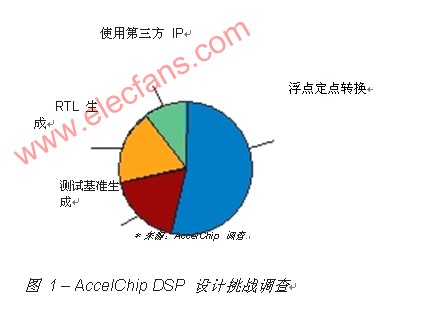

AccelChip 公司(最近已被賽靈思公司收購)最近所做的一次調查顯示,53% 的回答者認為浮點定點轉換是在 FPGA 上實現算法時最困難的地方(圖 1)。

生成定點模型

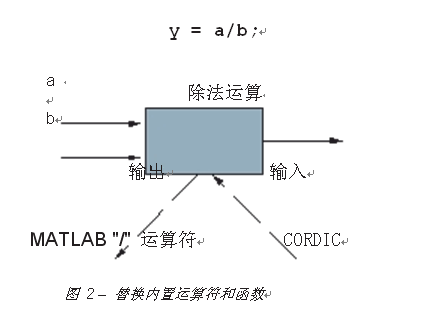

如果未將高級函數和運算符替換為硬件精確的宏架構,浮點 MATLAB 算法的定點表示將不會真正反映最終硬件的響應(圖 2)。

根據數據數值,計算輸出之間將存在巨大分歧。

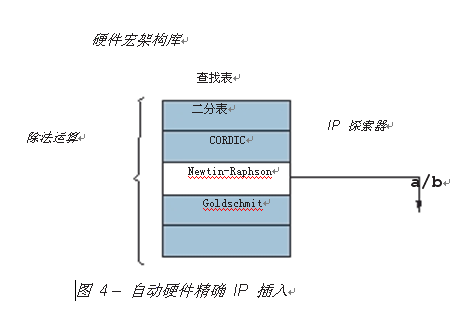

在定點生成過程中,AccelDSP? Synthesis 綜合工具的 IP Explorer? 技術將自動使用硬件精確的表達式替換高級 MATLAB 函數和運算符(圖 4)。此步驟是透明的,且不需要對 MATLAB 代碼進行修改。您可以使用綜合指示來重新定義初始宏架構和微架構選擇。

圖形輔助式自動量化

與定點 DSP 處理器不同, FPGA 結構允許使用可變定點字長。通過解除對變量的固定 16 位或 24 位邊界限制,您可以執行需要位數增長的算術計算而不會引起額外的數值誤差。

這對于像雷達、導航和制導系統等要求較高數值精度的應用來說是一個巨大的優點。

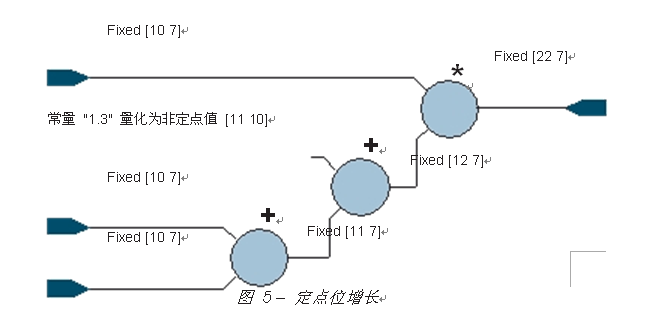

在大多數情況下,位增長率定律 (bit growth rules) 是簡單直接和易于理解的。例如,一次加法的結果增長一位,而一次乘法的結果則增長到等于輸入字長度的總長度(圖 5)。然而,要在實際設計中確定變量的這些屬性,將是一個高度反復的過程。允許未檢查的位數增長現象發生,在硬件中代價是昂貴的,通常也是不必要的。如果您技術功底深厚,您可以采用各種技巧來盡可能地減小字長而同時保持數值精度。

通過自動量化而獲得的初始定點模型提供了一個良好的起點,但一般需要對該模型進行細化改進。

MATLAB 提供了一種開發算法數學模型的高效環境,這種算法通常只需使用一組較少的仿真矢量就可完成。

該過程高度反復,且緊密耦合至數據作用 (data effect) 的分析。為了最大程度地縮短這一反復循環時間,AccelDSP Synthesis 綜合工具提供了一種加速定點仿真流程。

分析定點數據作用

MATLAB 提供了一種開發算法數學模型的高效環境,這種算法通常只需使用一組較少的仿真矢量就可完成。但是,當把該算法應用到定點硬件時,您將需要增加數據集,以精確地確定真實世界的環境響應。MATLAB 是一種解釋型仿真器,可能無法為這些較大的、CPU 強度較高的定點仿真提供必需的性能。因此,開發者常常轉向 C/C++。

加速定點仿真

AccelDSP Synthesis 綜合工具的 M2C-Accelerator 自動生成一個硬件精確的定點 C++ 模型和測試基準,以加快定點仿真。

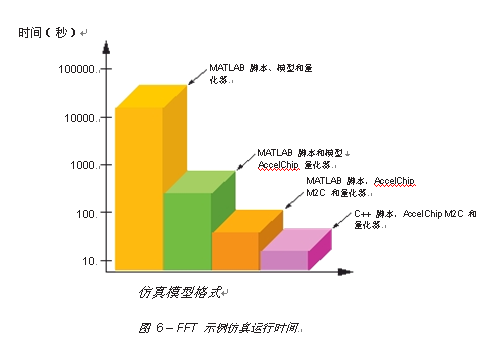

消除手動記錄步驟節省了開發時間,大程度地減小了誤差的引入。由于 C++ 是編譯式的,因此可提供高達 1000 倍的仿真性能優勢(圖 6)。這種性能水平通常是那些要求理解定點數據作用的大型矢量集所必需的。

觀測定點位增長

一個設計必須從整體上考慮,以有效地將浮點算法轉換為定點模型。

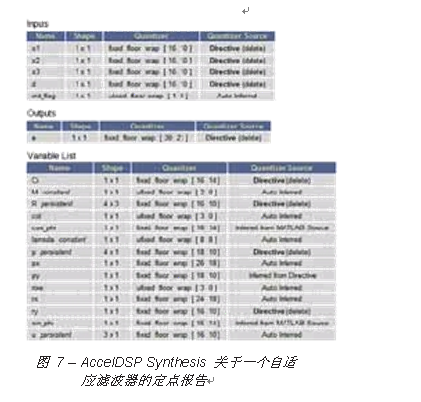

如果從早期開始就一直未對數據路徑進行檢查,位增長可能會快速增長而產生過度的硬件,而過度約束位增長則可能造成無法接受的數值精度損失。獲得對位增長進展情況較好觀測性的一種通用技巧是向一個電子表格中輸入變量。AccelDSP Synthesis 綜合工具通過生成一個表格化、格式化的定點報告(圖 7)而提供了此類級別的觀測性。

上溢出和下溢出

關于輸入數據動態范圍的不良假設可能會引起由于變量的最高有效位 (MSB) 上溢出和最低有效位 (LSB) 下溢出而導致較大的定點誤差的問題。您需要在觀測和糾正更細微的定點誤差之前先解決這些誤差。

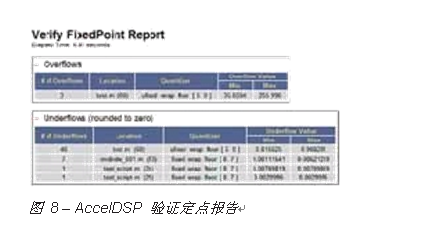

上溢出和下溢出報告,是 MATLAB

定點數據類型的固有屬性,但不是 C/C++ 所固有的,且常常在模型重寫過程中被省掉。但是,由 M2C-Accelerator 生成的 C++ 模型中包含了反映在仿真期間發生的所有上溢出和下溢出的量化例程。當這些情況發生時,它們將被匯總在“驗證定點報告”中(圖 8)。

定點可視化

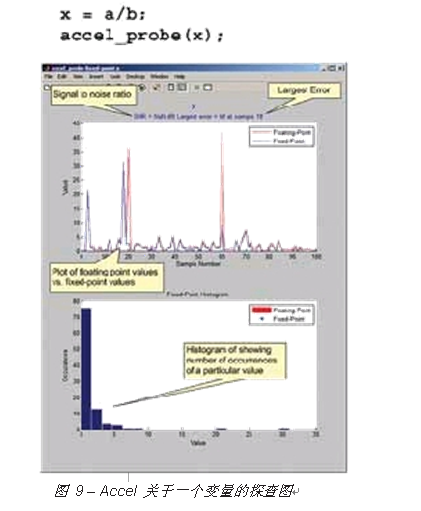

根據一組給定的數據集確定一個算法的合適定點響應,通常不是一種精確的科學行為。您常常不得不在數值精度方面做出一些折衷,以提高硬件效率。這一過程高度反復,且緊密耦合至繪圖中所示定點效應的可視分析。但是,在一個輸出信號上觀測到不可接受的 SNR,并不總是表示那里錯誤地指定了一個量化值。對此,必須進行進一步的分析。

為了幫助進行這一過程,AccelDSP Synthesis 綜合工具的 AccelProbe 工具以圖形方式對一個給定仿真期間的任何變量的浮點和定點值進行了比較(圖 9)。如果您使用的是 AccelProbe,您會迅速體會到特定變量的貢獻使最終結果的誤差累積的過程。您可以通過在 MATLAB 源碼中增加語句 “accel_probe(variable_name)”,來“探查”一個變量。

“定點歷史”圖可以讓您感知一個變量在仿真期間可能遇到的頻繁程度。如果一個值很少出現,則需要用以在動態范圍內的高端或低端存儲該值的附加硬件可能具有很小的值。

結論

當創建一個 DSP 算法的數學模型時,MATLAB 是天然之選,且出于硬件考慮,可以無阻礙地使用。將一個算法轉換為在 FPGA 上實現的定點模型是一個復雜的、可從 AccelDSP Synthesis 綜合工具提供的自動化、加速和可視化功能中大大受益的過程。

生成定點模型

如果未將高級函數和運算符替換為硬件精確的宏架構,浮點 MATLAB 算法的定點表示將不會真正反映最終硬件的響應(圖 2)。

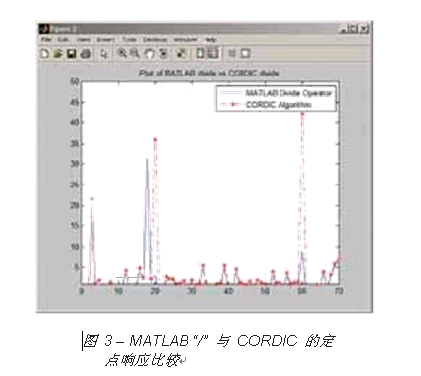

圖 3 對此進行了突出顯示,該圖使用一組量化為 8 位有符號二進制補碼的隨機輸入矢量,對 MATLAB 除法運算符與工具硬件 CORDIC 除法算法的定點響應進行了比較。

根據數據數值,計算輸出之間將存在巨大分歧。

在定點生成過程中,AccelDSP? Synthesis 綜合工具的 IP Explorer? 技術將自動使用硬件精確的表達式替換高級 MATLAB 函數和運算符(圖 4)。此步驟是透明的,且不需要對 MATLAB 代碼進行修改。您可以使用綜合指示來重新定義初始宏架構和微架構選擇。

圖形輔助式自動量化

與定點 DSP 處理器不同, FPGA 結構允許使用可變定點字長。通過解除對變量的固定 16 位或 24 位邊界限制,您可以執行需要位數增長的算術計算而不會引起額外的數值誤差。

這對于像雷達、導航和制導系統等要求較高數值精度的應用來說是一個巨大的優點。

在大多數情況下,位增長率定律 (bit growth rules) 是簡單直接和易于理解的。例如,一次加法的結果增長一位,而一次乘法的結果則增長到等于輸入字長度的總長度(圖 5)。然而,要在實際設計中確定變量的這些屬性,將是一個高度反復的過程。允許未檢查的位數增長現象發生,在硬件中代價是昂貴的,通常也是不必要的。如果您技術功底深厚,您可以采用各種技巧來盡可能地減小字長而同時保持數值精度。

? ?? ?

? ?? ?

通過自動量化而獲得的初始定點模型提供了一個良好的起點,但一般需要對該模型進行細化改進。

MATLAB 提供了一種開發算法數學模型的高效環境,這種算法通常只需使用一組較少的仿真矢量就可完成。

該過程高度反復,且緊密耦合至數據作用 (data effect) 的分析。為了最大程度地縮短這一反復循環時間,AccelDSP Synthesis 綜合工具提供了一種加速定點仿真流程。

分析定點數據作用

MATLAB 提供了一種開發算法數學模型的高效環境,這種算法通常只需使用一組較少的仿真矢量就可完成。但是,當把該算法應用到定點硬件時,您將需要增加數據集,以精確地確定真實世界的環境響應。MATLAB 是一種解釋型仿真器,可能無法為這些較大的、CPU 強度較高的定點仿真提供必需的性能。因此,開發者常常轉向 C/C++。

加速定點仿真

AccelDSP Synthesis 綜合工具的 M2C-Accelerator 自動生成一個硬件精確的定點 C++ 模型和測試基準,以加快定點仿真。

消除手動記錄步驟節省了開發時間,大程度地減小了誤差的引入。由于 C++ 是編譯式的,因此可提供高達 1000 倍的仿真性能優勢(圖 6)。這種性能水平通常是那些要求理解定點數據作用的大型矢量集所必需的。

觀測定點位增長

一個設計必須從整體上考慮,以有效地將浮點算法轉換為定點模型。

如果從早期開始就一直未對數據路徑進行檢查,位增長可能會快速增長而產生過度的硬件,而過度約束位增長則可能造成無法接受的數值精度損失。獲得對位增長進展情況較好觀測性的一種通用技巧是向一個電子表格中輸入變量。AccelDSP Synthesis 綜合工具通過生成一個表格化、格式化的定點報告(圖 7)而提供了此類級別的觀測性。

上溢出和下溢出

關于輸入數據動態范圍的不良假設可能會引起由于變量的最高有效位 (MSB) 上溢出和最低有效位 (LSB) 下溢出而導致較大的定點誤差的問題。您需要在觀測和糾正更細微的定點誤差之前先解決這些誤差。

上溢出和下溢出報告,是 MATLAB

定點數據類型的固有屬性,但不是 C/C++ 所固有的,且常常在模型重寫過程中被省掉。但是,由 M2C-Accelerator 生成的 C++ 模型中包含了反映在仿真期間發生的所有上溢出和下溢出的量化例程。當這些情況發生時,它們將被匯總在“驗證定點報告”中(圖 8)。

定點可視化

根據一組給定的數據集確定一個算法的合適定點響應,通常不是一種精確的科學行為。您常常不得不在數值精度方面做出一些折衷,以提高硬件效率。這一過程高度反復,且緊密耦合至繪圖中所示定點效應的可視分析。但是,在一個輸出信號上觀測到不可接受的 SNR,并不總是表示那里錯誤地指定了一個量化值。對此,必須進行進一步的分析。

為了幫助進行這一過程,AccelDSP Synthesis 綜合工具的 AccelProbe 工具以圖形方式對一個給定仿真期間的任何變量的浮點和定點值進行了比較(圖 9)。如果您使用的是 AccelProbe,您會迅速體會到特定變量的貢獻使最終結果的誤差累積的過程。您可以通過在 MATLAB 源碼中增加語句 “accel_probe(variable_name)”,來“探查”一個變量。

“定點歷史”圖可以讓您感知一個變量在仿真期間可能遇到的頻繁程度。如果一個值很少出現,則需要用以在動態范圍內的高端或低端存儲該值的附加硬件可能具有很小的值。

結論

當創建一個 DSP 算法的數學模型時,MATLAB 是天然之選,且出于硬件考慮,可以無阻礙地使用。將一個算法轉換為在 FPGA 上實現的定點模型是一個復雜的、可從 AccelDSP Synthesis 綜合工具提供的自動化、加速和可視化功能中大大受益的過程。

電子發燒友App

電子發燒友App

評論