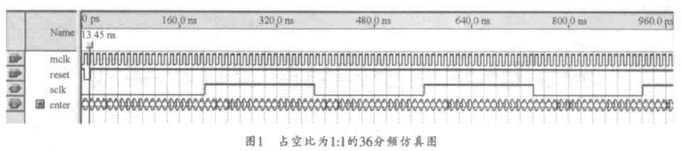

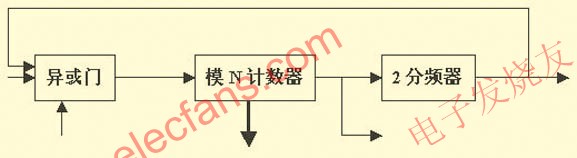

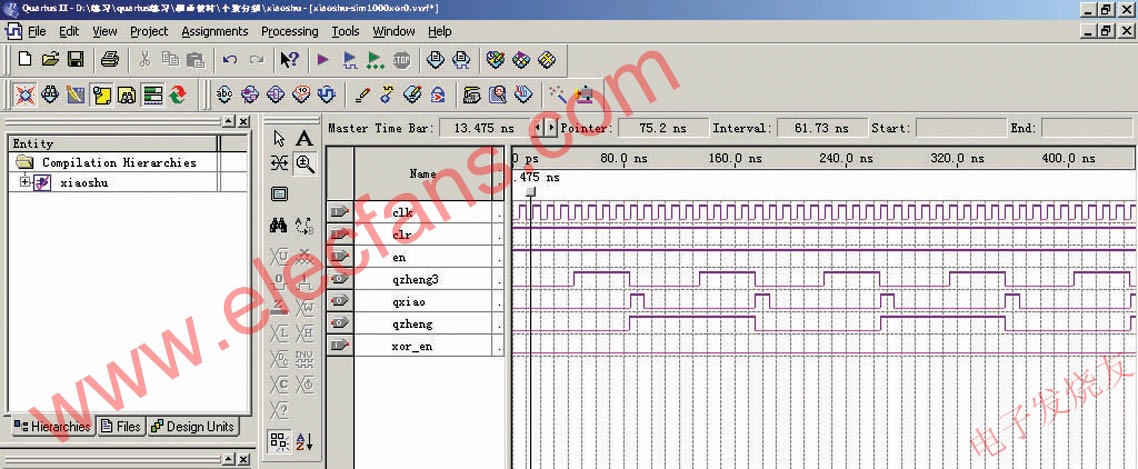

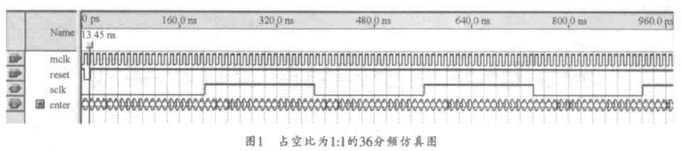

本文首先介紹了各種分頻器的實現原理,并在FPGA開發平臺上通過VHDL文本輸入和原理圖輸入相結合的方式,編程給出了仿真結果。最后通過對各種分頻的分析,利用層次化設計思想,綜合設計出了一種基于FPGA的通用數控分頻器,通過對可控端口的調節就能夠實現不同倍數及占空比的分頻器。

2015-05-07 09:43:16 4685

4685

初學FPGA,聽說分頻貌似挺重要,是必備的基礎技能。小白的我今天就從奇偶分頻開始我的FPGA學習成長之路偶數分頻很簡單的哈,打字蠻累的,直接上代碼/*************6分頻

2016-03-30 11:35:51

`基于FPGA+的任意小數分頻器的設計基于FPGA的多種分頻設計與實現基于FPGA的小數分頻器的實用Verilog 實現基于FPGA 的通用分頻用Verilog+HDL實現基于FPGA的通用分頻

2012-02-03 15:02:31

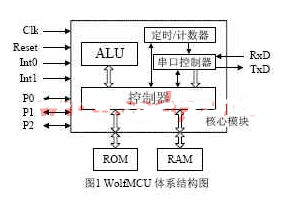

設計RISC微處理器需要遵循哪些原則?基于FPGA技術用VHDL語言實現的8位RISC微處理器

2021-04-13 06:11:51

的設計早期就能查驗設計系統的功能可行性,隨時可對設計進行仿真模擬。3.大規模設計一些大型的 FPGA 設計項目必須有多人甚至多個開發組共同并行工作才能實現。VHDL 語句的行為描述能力和程序結構決定了它具有

2018-09-07 09:04:45

VHDL與FPGA設計

2012-08-17 09:44:37

請教大家怎么用VHDL語言實現減法運算?在FPGA設計時又該怎么操作呢?

2012-05-17 20:07:12

數字示波器的FPGA實現, VHDL語言,測試通過(僅供參考)

2009-11-06 19:53:52

所示。圖22 八種編碼波形總結1) 運用VHDL編寫以上八種編碼是可行的。2) 經過觀察各模塊的仿真波形,符合各個編碼的特性。3) 通過整體程序的調試仿真,并在FPGA上實現了波形的鍵選。

2015-01-29 14:11:42

摘要:為了實現對非相干雷達的接收相參處理,基于數字穩定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語言,設計了一種基于FPGA的DSU硬件實現方法。實驗結果表明

2019-06-28 08:27:33

從零開始計數。以此循環下去。這種方法可以實現任意的偶數分頻。第二,奇數倍分頻:奇數倍分頻常常在論壇上有人問起,實際上,奇數倍分頻有兩種實現方法:首先,完全可以通過計數器來實現,如進行三分頻,通過待分頻時鐘

2019-06-14 06:30:00

各位朋友,大家好!我剛學習FPGA,選擇的是VHDL語言,試著編寫了一個二分頻和四分頻的程序,二分頻成功了,但四分頻卻有問題,代碼如下:library ieee;use

2012-11-27 22:03:47

Altera的PLL,Xilinx的DLL)來進行時鐘的分頻、倍頻以及相移設計,但是,對于時鐘要求不太嚴格的設計,通過自主設計進行時鐘分頻的實現方法仍然非常流行。首先這種方法可以節省鎖相環資源,再者

2014-06-19 16:15:28

【摘要】:介紹了基于FPGA的任意分頻系數的分頻器的設計,該分頻器能實現分頻系數和占空比均可以調節的3類分頻:整數分頻、小數分頻和分數分頻。所有分頻均通過VHDL語言進行了編譯并且給出了仿真圖。本

2010-04-26 16:09:01

不知道有沒有大神做過:基于FPGA的圖像邊緣檢測系統設計,用VHDL語言實現

2018-05-10 00:22:07

字電路中會經常用到多種不同頻率的時鐘脈沖,一般采用由一個固定的晶振時鐘頻率來產生所需要的不同頻率的時鐘脈沖的方法進行時鐘分頻。

2019-10-08 10:08:10

,一般情況下,速度指標是首要的,在滿足速度要求的前提下,盡可能實現面積優化。因此,本文結合在設計超聲探傷數據采集卡過程中的CPLD編程經驗,提出串行設計、防止不必要鎖存器的產生、使用狀態機簡化電路描述、資源共享,利用E2PROM芯片節省片內資源等方法對VHDL電路進行優化。

2019-06-18 07:45:03

你好,我是西安大略大學的研究生。我目前正在使用Virtex5 XUPV5 -LX110T FPGA開發板。我使用DCM在VHDL中編寫了一個簡單的時鐘分頻器,我使用IMPACT對代碼進行了編程。我

2020-06-12 14:23:23

利用現場可編程門陣列(FPGA)和VHDL 語言實現了PCM碼的解調,這樣在不改變硬件電路的情況下,能夠適應PCM碼傳輸速率和幀結構變化,從而正確解調數據。

2021-05-07 06:58:37

本文介紹利用VHDL語言實現 FPGA與單片機的串口異步通信電路。

2021-04-29 06:34:57

從零開始計數。以此循環下去。這種方法可以實現任意的偶數分頻。第二,奇數倍分頻:奇數倍分頻常常在論壇上有人問起,實際上,奇數倍分頻有兩種實現方法:首先,完全可以通過計數器來實現,如進行三分頻,通過待分頻時鐘

2019-07-09 09:11:47

介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進行直接數字頻率合成的VHDL源程序。

2021-04-30 06:29:00

大家好, 我想多鬧鐘。實際上我使用50Mhz時鐘頻率,我想把它作為100Mhz時鐘頻率。沒有PLL,DCM,是否有任何其他可能性來實現使用vhdl編程邏輯? 我知道,如何將時鐘分頻如80Mhz時鐘

2020-04-07 13:25:33

AC-Link音頻編/解碼原理是什么?怎么實現AC-Link數字音頻VHDL編/解碼的FPGA設計?

2021-05-10 06:46:20

本文介紹直流電機進行位置控制的方法,給出位置控制模塊的設計和實現,使用 VHDL語言進行編程完成了FPGA對直流電機的各種控制。

2021-05-10 06:19:17

怎么設計一款基于FPGA的多種分頻設計?

2021-05-08 07:06:43

學校要求的課程設計基于VHDL實現任意小數分頻

2014-04-24 09:09:31

剛接觸FPGA 想用FPGA實現422通訊 求大牛給一個實現UART的VHDL的程序

2013-12-05 20:40:39

有關VHDL分頻的問題,最終輸出不對,程序什么的都有,程序的作用是對時鐘先進行10分頻,再進行20分頻,最終級聯實現200分頻,程序如附件

2016-10-27 12:56:08

求助幫忙用vhdl實現一段fpga框圖,(價錢可商議),急用!!!!求助幫忙用vhdl實現幾個fpga框圖,(價錢可商議),急用!!!!已經有現成的vhdl程序編碼主要是想完成資料里面已經有的框圖出來,,寫材料需要用的~~~有意者請聯系我的QQ:444741540 或者***~~越快越好~~~~

2013-03-29 18:04:41

使用VHDL語言怎樣實現數控半整數分頻器,就當輸入為3時,就實現3.5分頻,當輸入為4時,就實現4.5分頻,同時要求占空比為50%。

2014-12-02 18:28:57

傳統交通燈控制器多數由單片機或PLC 實現。本論文介紹一種用FPGA 實現交通燈控制器的設計方法。關鍵詞:FPGA; VHDL; MAXPLUSll; 交通燈控制器Abstract:Traffic light controller is usually

2009-06-12 11:12:52 90

90 FPGA/VHDL技術是近年來計算機與電子技術領域的又一場革命。本書以AAltera公司的FPGA/CPLD為主詳細介紹了FPGA、CPLD為主詳細介紹了FPGA的相關知識,MAX+PLUSⅡ開發環境和VHDL語言基礎,并

2009-07-11 15:06:42 58

58

介紹了用VHDL 語言在硬件芯片上實現浮點加/ 減法、浮點乘法運算的方法,并以Altera

公司的FLEX10K系列產品為硬件平臺,以Maxplus II 為軟件工具,實現了6 點實序列浮點加/ 減法

2009-07-28 14:06:13 85

85 在復雜數字邏輯電路設計中,經常會用到多個不同的時鐘信號。介紹一種通用的分頻器,可實現2~256 之間的任意奇數、偶數、半整數分頻。首先簡要介紹了FPGA 器件的特點和應用范

2009-11-01 14:39:19 78

78 本文介紹了一種能夠完成半整數和各種占空比的奇/偶數和的通用的分頻器設計,并給出了本設計在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中實現后的測試數據和設計硬件的測

2009-12-19 16:25:09 65

65 基于FPGA 的等占空比任意整數分頻器的設計

給出了一種基于FPGA 的等占空比任意整數分頻電路的設計方法。首先簡要介紹了FPGA 器件的特點和應用范圍, 接著討論了一

2010-02-22 14:22:32 39

39 簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和1.5的分頻器的設計為例,介紹了在MaxPlusII開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過

2010-07-17 17:55:57 36

36 摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸

2006-03-13 19:36:44 869

869

用VHDL語言實現3分頻電路

標簽/分類:

眾所周知,分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相

2007-08-21 15:28:16 5527

5527 容錯系統中的自校驗技術及實現方法

闡述了自校驗技術在容錯系統中的作用,給出了自校驗網絡實現原理及實現方法,指出用VHDL語言結合FPGA/CPLD是實現大規模自校

2009-03-28 16:23:21 603

603

【摘 要】 通過設計實例詳細介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優越性。

2009-05-10 19:47:30 1111

1111

基于多種EDA工具的FPGA設計

介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配置下載等具體內容。并以實

2009-05-14 18:38:38 854

854

摘要:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配置下載等具體內容。并以實際操作介紹了

2009-06-20 11:42:45 522

522

摘要:介紹了為PET(正電子發射斷層掃描儀)的前端電子學模塊提供時間基準而設計的一種新型高頻時鐘扇出電路。該電路利用FPGA芯片來實現對高頻時鐘的分頻

2009-06-20 12:41:04 1238

1238

摘 要: 本文通過在QuartursⅡ開發平臺下,一種能夠實現等占空比、非等占空比整數分頻及半整數分頻的通用分頻器的FPGA設計與實現,介紹了利用VHDL硬件描

2009-06-20 12:43:07 562

562

摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸

2009-06-20 12:45:00 627

627

摘要:介紹了一種用VHDL設計USB2.0功能控制器的方法,詳術了其原理和設計思想,并在FPGA上予以實現。

關鍵詞:USB VHDL FPGA

在視

2009-06-20 13:26:46 1474

1474

摘 要: 闡述了自校驗技術在容錯系統中的作用,給出了自校驗網絡實現原理及實現方法,指出用VHDL語言結合FPGA/CPLD是實現大規模自校驗網絡的有效途徑。

2009-06-20 15:46:43 529

529

用VHDL語言實現3分頻電路(占空比為2比1)

分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖

2009-06-22 07:46:33 7831

7831 數字電壓表的VHDL設計與實現

介紹數字電壓表的組成及工作原理,論述了基于VHDL語言和FPGA芯片的數字系統的設計思想和實現過程。 關鍵詞:數字電壓表;VHDL語

2009-10-12 19:14:32 1628

1628

基于CPLD/FPGA的多功能分頻器的設計與實現

引言

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求

2009-11-23 10:39:48 1139

1139

多種EDA工具的FPGA設計方案

概述:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配

2010-05-25 17:56:59 670

670

針對目前國內SDH系統中還沒有一個專門的E1分接復用芯征,本文介紹一種用高級硬件描述語言VHDL及狀態轉移圖完成該發接復用器的設計的新型設計方法及其FPGA實現。并給出了

2010-08-27 09:42:32 2704

2704

本文采用VHDL描述語言,充分利用Xilinx公司Spartan II FPGA的系統資源,設計實現了一種非對稱同步FIFO,它不僅提供數據緩沖,而且能進行數據總線寬度的轉換。

2011-01-13 11:33:43 1744

1744 利用FPGA實現時分多址的方法有很多種,但大多數方法都對FPGA芯片資源的占用非常巨大。針對這一問題,提出一種改進型方法來實現時分多址。通過使用FPGA芯片內部的雙口隨機訪問存儲器(雙口RAM),利用同一塊RAM采用兩套時鐘線,地址線和數據線,例化雙口RAM的

2011-01-15 15:41:26 29

29 本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種結構類型的fir數字濾波器的fpga實現、不同結構

2011-11-04 15:50:12 0

0 本文給出了分頻技術通用模型。并結合最新的一些分頻技術,提出了一種基于FPGA全新的分頻系統的設計方法,簡單的介紹了設計的思路、原理及其算法,并對該方案的性能進行了分析,

2011-11-08 18:03:32 137

137 提出了一種基于FPGA的小數分頻實現方法,介紹了現有分頻方法的局限性,提出一種新的基于兩級計數器的分頻實現方法,給出了該設計方法的設計原理以及實現框圖

2011-11-09 09:36:22 121

121 給出了一種基于FPGA的分頻電路的設計方法.根據FPGA器件的特點和應用范圍,提出了基于Verilog的分頻方法.該方法時于在FPGA硬件平臺上設計常用的任意偶數分頻、奇數分頻、半整數分頻

2011-11-09 09:49:33 355

355 介紹了一種基于FPGA的雙模前置小數分頻器的分頻原理及電路設計,并用VHDL編程實現分頻器的仿真.

2011-11-29 16:43:06 48

48 為了實現對非相干雷達的接收相參處理,基于數字穩定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語言,設計了一種基于FPGA的DSU硬件實現方法。實驗結果表明基于FPGA的

2012-06-26 15:48:36 27

27 altera FPGA/CPLD高級篇(VHDL源代碼)

2012-11-13 14:40:38 134

134 文中著重介紹了一種基于FPGA利用VHDL硬件描述語言的數字秒表設計方法,在設計過程中使用基于VHDL的EDA工具ModelSim對各個模塊仿真驗證,并給出了完整的源程序和仿真結果。

2012-12-25 11:19:24 6071

6071 本書比較全面地闡述了fpga在數字信號處理中的應用問題。本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種

2015-12-23 11:07:46 44

44 Xilinx FPGA工程例子源碼:FM收音機的解碼及控制器VHDL語言實現

2016-06-07 14:13:43 11

11 Xilinx FPGA工程例子源碼:VHDL實現對圖像的采集和壓縮

2016-06-07 14:54:57 6

6 用 Verilog實現基于FPGA 的通用分頻器的設計時鐘分頻包括奇數和偶數分頻

2016-07-14 11:32:47 45

45 vhdl語法介紹FPGA設計實例nios ii設計實例北航版本

2016-07-14 17:34:13 74

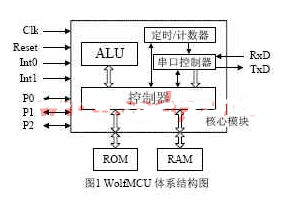

74 目前許多FPGA的邏輯資源(LE)都已超過1萬門,使得片上可編程系統SOPC已經成為可能。算術邏輯單元ALU應用廣泛,是片上可編程系統不可或缺的一部分。利用VHDL語言在FPGA芯片上設計ALU的研究較少,文中選用FPGA來設計32位算術邏輯單元ALU,通過VHDL語言實現ALU的功能。

2018-07-22 11:22:00 6949

6949

設計背景: 分頻在 fpga的設計中一直都擔任著很重要的角色,而說到分頻,我相信很多人都已經想到了利用計算器來計算達到想要的時鐘頻率,但問題是僅僅利用計數器來分頻,只可以實現偶數分頻,而如果我需要

2018-06-13 11:21:48 12390

12390

不太嚴格的設計,通過自主設計進行時鐘分頻的實現方法仍然非常流行。首先這種方法可以節省鎖相環資源,再者,這種方式只消耗不多的邏輯單元就可以達到對時鐘操作的目的。

2019-08-07 08:00:00 9033

9033

本文檔的主要內容詳細介紹的是FPGA視頻教程之FPGA和CPLD與VHDL基礎知識的詳細資料說明。主要的目的是:1.VHDL入門,2.設計單元,3.體系結構建模基礎,4.VHDL邏輯綜合,5.層次

2019-03-20 14:35:19 9

9 基于提升框架的小波變換方法,利用FPGA 可編程特性可實現多種小波變換。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近幾年提出的一種小波變換方法,用它的框架結構能有效地計算DWT。對于較長的濾波器,LS 的操作次數比濾波器組的操作方式減少將近一半,更適合硬件實現。

2019-08-18 09:47:57 1918

1918

基于提升框架的小波變換方法,利用FPGA 可編程特性可實現多種小波變換。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近幾年提出的一種小波變換方法,用它的框架結構能有

2019-08-25 11:01:31 5747

5747

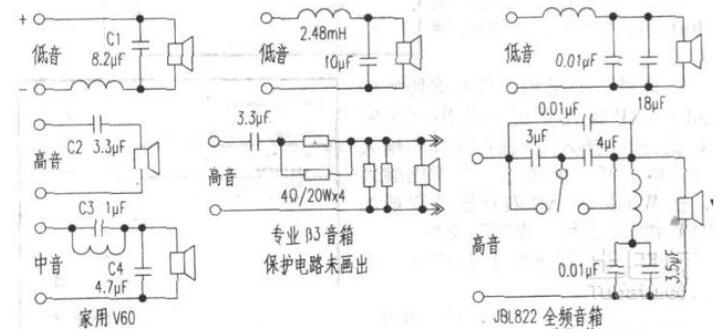

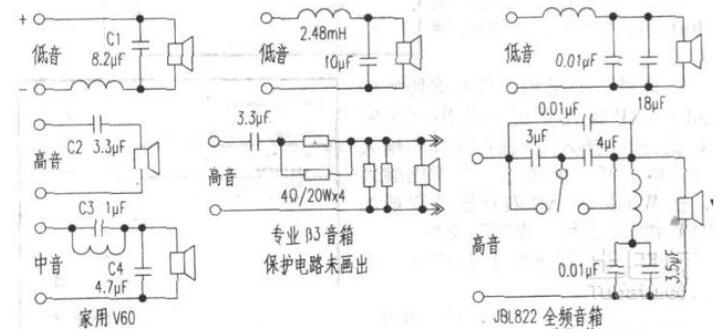

本文主要闡述看音箱分頻器的維修方法及音箱分頻器接喇叭的方法。

2020-03-28 11:09:59 14938

14938

在數字系統設計中,根據不同的設計需要,經常會遇到偶數分頻、奇數分頻、半整數分頻等,有的還要求等占空比。在基于cpld(復雜可編程邏輯器件)的數字系統設計中,很容易實現由計數器或其級聯構成各種形式的偶數分頻及非等占空比的奇數分頻,但對等占空比的奇數分頻及半整數分頻的實現較為困難。

2020-06-26 09:36:00 825

825

通常情況下,時鐘的分頻在FPGA設計中占有重要的地位,在此就簡單列出分頻電路設計的思考思路。

2020-07-10 17:18:03 2192

2192 基于以上討論,可以看出ASIP+FPGA設計模式可以從很大程度上解決引言中提到的兩個難題。為了進行更深入的研究,我們對該設計模式進行了嘗試,用VHDL硬件描述語言在FPGA上實現了一個8位微處理器

2020-07-28 17:44:49 562

562

介紹了單片機與FPGA 異步串行通信的實現方法,給出了系統結構原理框圖及其部分VHDL 程序,并定義了發送器和接收器的端口信號。

2020-09-29 16:20:00 8

8 本文檔的主要內容詳細介紹的是使用FPGA實現自動售貨機的VHDL程序與仿真資料。

2020-12-21 17:10:00 23

23 本文檔的主要內容詳細介紹的是使用FPGA實現自動售貨機的VHDL程序與仿真資料免費下載。

2020-12-22 17:07:00 15

15 本文檔的主要內容詳細介紹的是使用FPGA VHDL實現電子點餐項目設計的參考實例資料合集包括了:電子點餐接收端,電子點餐protel格式電路圖,電子點餐發送端,電路圖和PCB原理圖免費下載。

2020-12-23 16:47:39 18

18 本文檔的主要內容詳細介紹的是使用FPGA實現ADC0809的VHDL控制程序免費下載。

2021-01-18 17:17:00 17

17 本文檔的主要內容詳細介紹的是使用FPGA實現LCD控制的VHDL程序與仿真資料免費下載。

2021-01-18 17:19:08 10

10 本文檔的主要內容詳細介紹的是使用FPGA實現LED控制的VHDL程序與仿真資料免費下載。

2021-01-18 17:32:46 12

12 FPGA Express將VHDL描述轉換并優化為內部門級等效格式。然后針對給定的FPGA技術編譯此格式。

2021-01-21 16:02:09 7

7 簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和1.5的分頻器的設計為例,介紹了在MaxPlusII開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過程和方法。該設計具有結構簡單、實現方便、便于系統升級的特點。

2021-03-16 09:45:53 10

10 簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為25和15的分頻器的設計為例,介紹了在 Maxplus開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過程和方法該設計具有結構簡單、實現方便、便于系統升級的特點。

2021-04-12 16:29:05 11

11 一種基于FPGA的分頻器的實現說明。

2021-05-25 16:57:08 16

16 FPGA分頻器是一種常用于數字信號處理、通信系統、雷達系統等領域的電路,其作用是將信號分成多個頻段。

2023-05-22 14:29:44 1032

1032

基于FPGA的高頻時鐘的分頻和分頻設計

2023-08-16 11:42:47 0

0

電子發燒友App

電子發燒友App

評論