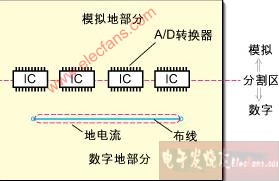

混合信號PCB的分區設計原則

混合信號電路PCB的設計很復雜,元器件的布局、布線以及電源和地線的處理

2009-03-25 11:40:23 785

785

3W原則在PCB設計中為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持大部分電場不互相干擾,這就是3W規則。3W原則是指多個高速信號線長距離走線的時候,其間距...

2022-01-26 06:50:22

FPGA引腳信號指配有什么原則?

2021-04-30 07:04:56

小弟剛買的FPGA核心板,打算自己畫底板的說。買的核心板沒有給引腳配置,只給了原理圖,原理圖上雖然標明了FPGA的引腳,可是……這個東西怎么看呀?它不像是買的開發板那種,什么A11,W8這種,而是IO,DIFFO_T13P這種。我是該找賣家要一份,還是說要自己看,慢慢去對它的引腳呢?

2017-06-12 08:27:50

FPGA中幾個基本的重要的時序分析參數介紹(fmax\tsu\th\tco\tpd)今天無聊,翻開書偶看到介紹時序部分的東西,覺得其中幾個參數縮寫所代表的含義應該記住,故寫如下文章……FPGA中

2012-04-09 09:41:41

FPGA入門知識介紹近幾年來,由于現場可編程門陣列(FPGA)的使用非常靈活,又可以無限次的編程,已受到越來越多的電子編程者的喜愛,很多朋友都想學習一些FPGA入門知識準備進行這個行業,現在關于

2014-08-16 10:32:45

和說明,其實這也是FPGA的I/O引腳靈活的體現,對于一般的信號,FPGA的I/O可以隨意的連接。(特權同學,版權所有)圖3.42 核心板引出的兩個插座電路 `

2015-05-06 11:31:16

FPGA如何對引腳進行分塊?是由VCC的電壓不同進行自行設計分塊?還是每個塊的引腳都是固定的?在進行DDR3與FPGA的硬件連接時,由FPGA的芯片手冊得采用SSTL_15電壓標準,即VDDQ

2021-11-29 16:10:48

分配fpga管腳時該怎么選擇,引腳有什么屬性需要考慮,quartus2中引腳有幾個屬性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-06-17 08:55:43

(12)FPGA時鐘設計原則1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘設計原則5)結語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 07:08:36

想把FPGA(Altera Cyclone IV)的擴展IO引腳作為輸入直接采集信號,請問除了電壓外,對輸入電流有要求嗎,最大能夠承受多大的電流而不至于燒壞開發板?

2019-03-26 09:31:07

今天給大俠帶來FPGA設計基本原則及思想,話不多說,上貨。FPGA設計基本原則及思想一、硬件設計基本原則1、速度與面積平衡和互換原則:一個設計如果時序余量較大,所能跑的頻率遠高于設計要求,能可以通過

2020-10-11 12:26:42

/O信號分配 可提供最多的多功能引腳、I/O標準、端接方案和差分對的FPGA在信號分配方面也具有最復雜的設計指導原則。盡管Altera的FPGA器件沒有設計指導原則(因為它實現起來比較容易),但賽靈思

2020-09-07 11:01:46

FPGA設計的指導原則有哪些FPGA設計需注意的方方面面

2021-04-08 07:01:34

FPGA設計的電路速度指什么?? 比如設計電路速度為200MHz,是指每秒鐘可以吞吐200M個數據嗎?? 我的想法是比如FPGA的系統時鐘為50MHz,輸出是通過寄存器寄存后再輸出的,只有在每個時鐘

2023-04-23 14:58:18

時序仿真的重要性是什么傳統的FPGA驗證方法是什么FPGA設計的驗證技術及應用原則是什么

2021-05-08 09:05:32

FPGA配置引腳說明使用EMCCLK引腳,全速加載程序FPGA加載時序

2021-02-03 06:47:35

FPGA高速收發器設計原則高速FPGA設計收發器選擇需要考慮的因素

2021-04-09 06:53:02

FPGA中的引腳門,那些有著特殊用途的引腳,都有哪些能用作普通IO

2012-10-27 15:34:42

我用fpga來控制220v的較大功率步進電機,使用的電機控制驅動模塊有三組信號 脈沖 方向 使能。這三組正級直連fpga 3.3v輸出信號后通過升壓后得到的5v控制信號,負極統一單獨接地(沒走

2017-09-15 17:46:04

信號完整性處理的8個基本原則

2021-01-14 07:19:08

/cpld的設計和優化技巧。在討論fpga/cpld設計指導原則的基礎上,介紹了altera器件的高級應用;引領讀者學習邏輯鎖定設計工具,詳細討論了時序約束與靜態時序分析方法;結合實例討論如何進行設計優化

2020-05-14 14:50:30

設計DSP系統時,我用C6000系列。DSP引腳的要上拉,或者下拉的原則是怎樣的?我經常在設計時為某一管腳是否要設置上/下拉電阻而猶豫不定。

2019-09-04 02:27:00

`3W原則在PCB設計中為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持大部分電場不互相干擾,這就是3W規則。3W原則是指多個高速信號線長距離走線的時候,其間距應該遵循

2020-09-27 16:49:19

一、芯片介紹1.原理圖2.引腳功能介紹引腳功能AIN0-AIN3模擬信號輸入端A0-A2引腳地址端VDD,VSS電源端SDA,SCLiic總線的數據線,時鐘線OSC內部時鐘輸入端,外部時鐘輸入端

2022-01-20 07:35:09

;MOSI,DC呢?難道是MISO?命令選擇怎么用的用IIC的話,D0->SCL,D1->SDA,那DC、CS、引腳是不要連嗎?DC:是指什么引腳?MISO?那片選呢?沒有怎么用?有誰用過OLED的,請指教

2018-10-18 09:02:22

越來越力不從心。 以FPGA為代表的可編程邏輯器件以其工作穩定、速度快、靈活的可編程能力等特點,獲得了越來越廣泛應用。本文提出了一種基于FPGA的振動信號采集處理系統;該系統具有實時性高,糾錯能力強等

2019-07-01 06:11:15

剛開始學習fpga,對引腳分配的問題不是很理解,求高手給予幫助 例如fpga的線路板上23引腳接clk ,28引腳是空余的 ,那么在編程的時候我可以用 28引腳接clk 嗎?

2013-01-06 15:24:21

,ROM,CAM 等常用單元模塊。 一般的 FPGA 系統規劃的簡化流程 4. 同步設計原則異步電路 電路的邏輯核心是用組合邏輯電路實現。比如異步的 FIFO/RAM 讀寫信號,地址譯碼等電路。電路

2020-01-01 08:00:00

dB時能測到雷達信號,使雷達的有效作用距離提高。本文主要介紹基于DSP和FPGA技術的低信噪比情況下雷達信號的檢測。

2019-07-04 06:55:39

利用高速FPGA設計PCB的要點及相關指導原則有哪些?

2021-04-25 08:17:55

大家好,我剛開始學習FPGA并試圖弄清楚哪些FPGA引腳可以分配我的數據信號。我正在使用FPGA Spartan 6封裝TQG114器件LX9。查看產品規格,有102個可用的用戶I / O.這是

2019-04-23 06:55:23

我有一塊fpga板子,其情況如下:

板子在設計時預留有備用引腳,這些備用引腳所在的IOBANK的電壓值為3.3V。

我現在想要一個在fpga里有一個邏輯一直為1的輸入信號,這個信號通過備用引腳中的一

2023-04-23 14:55:18

信號)哪個引腳用于此目標以及哪些引腳用于從osiloscobe看到此信號。 (我知道ADC / DAC使用但我沒有看到任何ucf文件)2-)FPGA存儲數據的容量是多少?例如,我想實時存儲這個模擬信號

2019-05-22 13:15:46

嗨, 有誰知道如何理解時鐘信號引腳?我需要知道返回FPGA并從FPGA出來的引腳(除了去往目標器件的差分數據引腳)。典型的應用是DAC到FPGA接口,我必須向DAC提供時鐘信號。我不確定哪些引腳向

2019-09-03 10:06:23

1. 面積與速度的平衡與互換這里的面積指一個設計消耗FPGA/CPLD的邏輯資源的數量,對于FPGA可以用消耗的FF(觸發器)和LUT(查找表)來衡量,更一般的衡量方式可以用設計所占的等價邏輯門數

2020-09-18 10:32:44

嵌入式操作系統介紹及選型原則

2012-08-20 15:27:58

本文在討論DDS的基礎上,介紹利用FPGA設計的基于DDS的信號發生器。

2021-05-06 09:54:10

`手機Layout中信號布線原則介紹 ,整個文檔內容如下,非常不錯的資料,在這里跟大家分享了[hide] [/hide]`

2011-12-20 11:21:38

燈具(LED)照明產品配光曲線測試 ,IES配光曲線測試項目介紹LED燈具IES配光曲線測試有哪些測試項目,IES費用多少;哪里可以做LED燈具IES配光曲線測試,請見下面:燈具(LED)照明產品配

2019-10-23 18:49:33

烙鐵咀(頭)配咀型的通用原則

2018-07-16 16:15:01

FPGA代碼最常使用的功能模塊是哪個呢?是狀態機、乘法器、加法器、計數器?答案就是計數器!幾乎我們的每個設計都要用到計數器,用來計算接受或發送了多少個數據,用來衡量用了多少時間,用來做選擇信號等等

2015-05-14 22:01:11

請問哈FPGA的輸入輸出信號跟端口引腳一定是一一對應的吧?

2019-04-16 04:46:22

本文介紹基于FPGA 和DDFS 技術,應用Altera 公司的FPGA 開發工具DSP Builder 設計數字移相信號發生器,該數字移相信號發生器的頻率、相位、幅度均可預置,分辨率高,精確可調。且可分

2009-12-18 11:59:54 44

44 FPGA設計思想與技巧:這一部分主要介紹FPGA/CPLD設計的指導性原則,如FPGA 設計的基本原則、基本設計:思想、基本操作技巧、常用模塊等。FPGA/CPLD設計的基本原則、思想、技巧和常用模

2010-01-11 09:00:37 34

34 FPGA設計的指導原則:這里“面積”指一個設計消耗FPGA/CPLD 的邏輯資源的數量,對于FPGA 可以用所消耗的觸發器(FF)和查找表(LUT)來衡量,更一般的衡量方式可以用設計所占用的等

2010-01-11 09:01:35 107

107 基于FPGA的DDS信號源設計與實現

利用DDS和 FPGA 技術設計一種信號發生器.介紹了該信號發生器的工作原理、 設計思路及實現方法.在 FPGA 器件上實現了基于 DDS技

2010-02-11 08:48:05 223

223 基于FPGA的各種雷達信號產生方法,介紹了在FPGA中實現直接數字頻率合成器(DDS)以及提高輸出信號質量的方法,編程實現了頻率捷變、線性調頻以及相位編碼等雷達信號的產生。仿真

2010-11-29 18:02:49 31

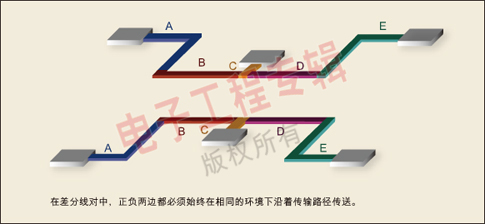

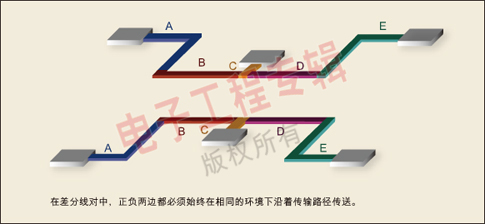

31 差分信號走線原則

差分線對的工作原理是使接收到的信號等于兩個互補并且彼此互為參考的信號之間的差值,因此可以極大地降低信

2008-05-09 10:00:36 38812

38812

FPGA高速收發器設計原則

高速收發器(SERDES)的運用范圍十分廣泛, 包括通訊、計算機、工業和儲存,以及必須在芯片與

2009-04-07 22:26:14 986

986 FPGA芯片選擇策略和原則

由于FPGA具備設計靈活、可以重復編程的優點,因此在電子產品設計領域得到了越來越廣泛的應用。在工程項目或者產品設計

2010-02-09 09:13:29 3080

3080 本文介紹了一種模目信號設計方法,利用FPGA產生時序及控制,DSP實時計算所需要的回波,從而實現對雷達目標回波的模擬,這樣可以在沒有陣面數據的情況下,使信號處理分系統調試能

2011-07-05 09:46:27 1111

1111

本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種結構類型的fir數字濾波器的fpga實現、不同結構

2011-11-04 15:50:12 0

0 介紹了PCB Layout零件布局走線的一般原則,數字信號走線盡量放置在數字信號布線區域內等知識

2012-06-25 11:25:17 5347

5347 在調試FPGA電路時要遵循必須的原則和技巧,才能降低調試時間,防止誤操作損壞電路。通常情況下,參考以下步驟執行 FPGA硬件系統的調試。 1、在焊接硬件電路前,首先要測試電路板

2013-01-16 11:59:58 4665

4665 基于FPGA數字信號處理,本文主要探討了基于FPGA數字信號處理的實現

2015-10-30 10:39:38 30

30 本書比較全面地闡述了fpga在數字信號處理中的應用問題。本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種

2015-12-23 11:07:46 44

44 FPGA的基本設計原則,基本設計思想,基本操作技巧,常用模塊。如果大家有意識的用這些原則方法指導日后的的工作,那么會達到事半功倍

2016-02-18 11:53:39 1

1 現在的FPGA向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。

2016-07-27 20:24:00 6740

6740 FPGA學習資料教程之Xilinx-FPGA-引腳功能詳細介紹

2016-09-01 15:27:27 0

0 引腳和區域約束也就是LOC約束(location)。定義了模塊端口和FPGA上的引腳的對應關系。 那么我們應該怎么寫呢?

2018-07-14 02:49:00 10273

10273 在調試FPGA電路時要遵循必須的原則和技巧,才能降低調試時間,防止誤操作損壞電路。通常情況下,能夠參考以下步驟執行 FPGA硬件系統的調試。

2017-02-11 16:18:59 663

663

現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳指配信號的指導方針有助于設計師根據最多到最少的約束信號指配原則提前考慮信號指配,并減少反復的次數。

2017-05-18 10:51:54 29124

29124

FPGA設計的基本原則 面積與速度折衷原則 面積和速度是ASIC芯片設計中一對相互制約、影響成本和性能的指標,貫穿FPGA設計的始終。在FPGA設計中,面積是指一個設計消耗的FPGA內 部邏輯資源

2017-11-25 03:57:01 802

802

本文檔內容介紹了MagicSOPC主板FPGA-IO引腳分配表,供參閱

2018-03-15 15:50:59 6

6 本文檔內容介紹了基于fpga實現信號發生器,供參考

2018-04-20 15:23:35 65

65 高性能DCDC設計的關鍵之電源熱設計(二)熱設計的原則和參數介紹

2020-05-29 09:14:00 2542

2542

在普通印制電路板的布線中由于信號是低速信號,所以在3W原則的基本布線規則下按照信號的流向將其連接起來,一般都不會出現問題。但是如果信號是100M以上的速度時,布線就很有講究了。由于最近布過速度高達300M的DDR信號,所以仔細說明一下DDR信號的布線原則和技巧。

2019-03-24 10:00:06 6908

6908

本文介紹了光耦的適用原則以及光耦的具體應用。

2019-08-12 09:08:58 3906

3906 FPGA的引腳交換

2020-01-20 17:53:00 2843

2843 復位信號設計的原則是盡量不包含不需要的復位信號,如果需要,考慮使用局部復位和同步復位。

2019-10-27 10:09:53 1735

1735

來源:羅姆半導體社區? 3W原則 在PCB設計中為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持大部分電場不互相干擾,這就是3W規則。 3W原則是指多個高速信號

2022-12-26 09:35:56 841

841 很多工程師在使用Xilinx開發板時都注意到了一個問題,就是開發板中將LVDS的時鐘輸入(1.8V電平)連接到了VCCO=2.5V或者3.3V的Bank上,于是產生了關于FPGA引腳與LVDS(以及

2020-10-10 09:25:37 10410

10410

一、面積與速度的平衡互換原則 這里的面積指的是 FPGA 的芯片資源,包括邏輯資源和 I/O 資源等;這里的速度指的是 FPGA 工作的最高頻率(和 DSP 或者 ARM 不同,FPGA 設計的工作

2023-02-03 15:30:30 389

389 本文檔的主要內容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現優化設計。

2021-01-13 17:00:59 25

25 這一部分主要介紹 FPGA/CPLD設計的指導性原則,如FPGA設計的基本原則、基本設計思想、基本操作技巧、常用模塊等。 FPGA/CPLD設計的基木原則、思想、技巧和常用模塊是一個非常大

2021-01-20 15:17:09 26

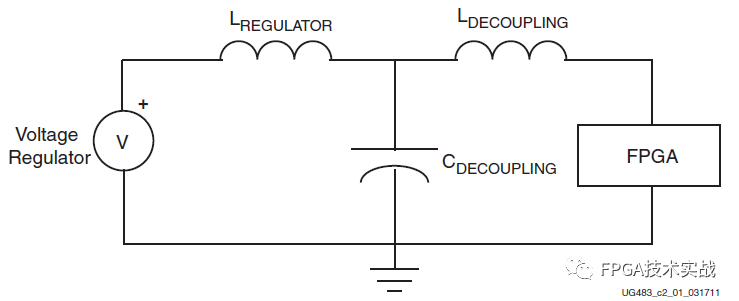

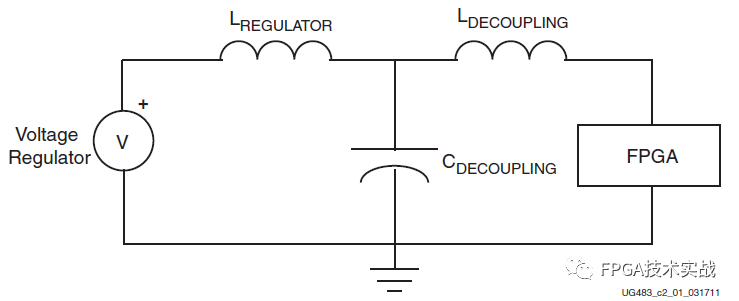

26 引言:我們繼續介紹FPGA PCB設計相關知識,本章介紹7系列FPGA的配電系統(PDS),包括去耦電容器的選擇、放置和PCB幾何結構,并為每個7系列FPGA提供了一種簡單的去耦方法。另外,還介紹

2021-03-12 14:42:45 3505

3505

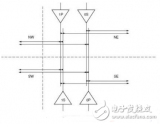

FPGA System Planner解決了設計一個或多個工程師時遇到的挑戰PCB板上的更多大引腳數FPGA。

2021-03-16 16:56:15 24

24 (12)FPGA時鐘設計原則1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘設計原則5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 異步電路的邏輯核心是用組合邏輯電路實現,比如異步的FIFO/RAM讀寫信號,地址譯碼等電路。電路的主要信號、輸出信號等并不依賴于任何一個時鐘性信號,不是由時鐘信號驅動FF產生的。

2023-01-05 09:58:50 298

298 FPGA設計中幾乎不可避免地會用到復位信號,無論是同步復位還是異步復位。我們需要清楚的是復位信號對時序收斂、資源利用率以及布線擁塞都有很大的影響。

2023-03-30 09:55:34 806

806 現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳指配信號的指導方針有助于設計師根據最多到最少的約束信號指配原則提前考慮信號指配,并減少反復的次數。

2023-05-04 17:38:53 597

597 今天給大家介紹一些PCB布局的思路和原則

2023-05-17 10:00:03 763

763

速度-面積互換原則是貫穿FPGA設計的重要原則:速度是指工程穩定運行所能達到的最高時鐘頻率,通常決定了FPGA內部寄存器的運行時序;面積是指工程運行所消耗的資源數量,通常包括觸發器

2023-06-09 09:36:37 798

798

之前的文章介紹了FPGA在線調試的方法,包括選定抓取信號,防止信號被優化的方法等等。

2023-06-20 10:38:48 3333

3333

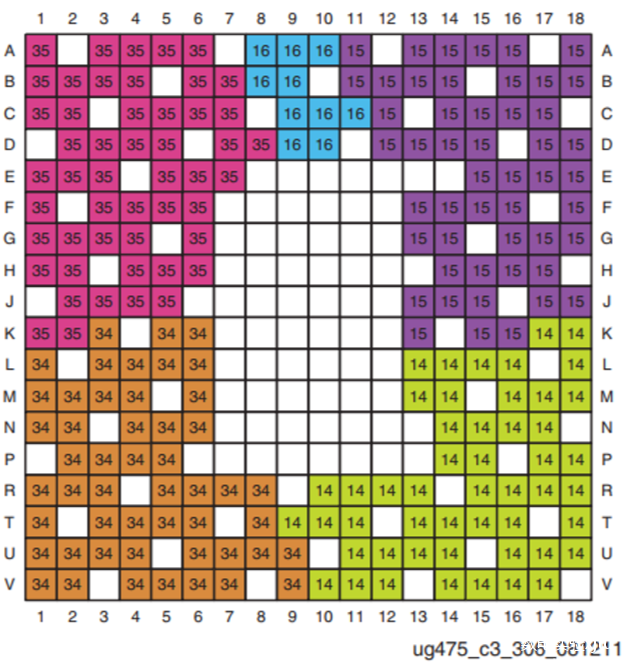

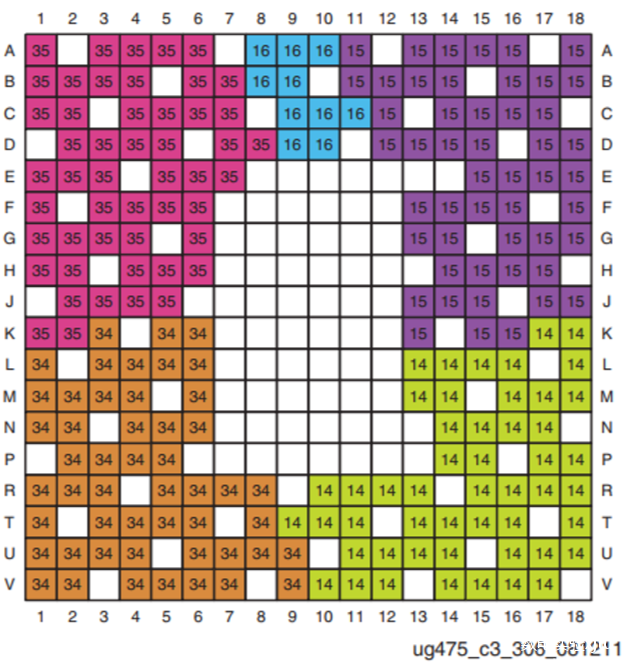

FPGA的引腳排布在芯片背面,以EGO1板載芯片XC7A35T-1CSG324C 為例,下圖中每個小格代表一個引腳,共有18行18列,共324個引腳。

2023-09-17 15:09:15 1781

1781

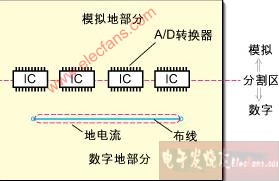

電子發燒友網站提供《數混合信號器件的一般接地原則.pdf》資料免費下載

2023-11-29 10:45:30 1

1

電子發燒友App

電子發燒友App

評論