1 概述

PSTN短消息終端SoC是為固定電話網短消息業(yè)務而設計的一種數(shù)字終端處理芯片。片上集成了微控制器、RAM、FSK/DTMF調制解調器、 LCD接口、鍵盤掃描、數(shù)據(jù)存儲器擴展頁面尋址接口以及線路狀態(tài)控制接口;可以完成FSK和DTMF格式的短消息上傳、下傳,CID(Calling IdenTIty Delivery,主叫識別信息傳送)號碼的接收,振鈴信號檢測,話機狀態(tài)控制等功能[1],提供了PSTN短消息終端的單芯片解決方案。其中,使用了 DW8051_core IP核作為SoC的微控制器核心。

SoC(System on chip,片上系統(tǒng))不僅指它的硬件平臺,還包括運行在其上的軟件成分。如果系統(tǒng)采用全硬件設計的方案,優(yōu)點是速度快、效率高,但是研制周期長,從而成本也高;用軟件實現(xiàn)則更為靈活,研制周期短。缺點是速度慢,效率比較低。因此,SoC設計必須在硬件與軟件功能劃分上有一個合理的權衡,并進行協(xié)同設計 [2]。

2 SoC系統(tǒng)任務的軟硬件功能劃分

系統(tǒng)任務按功能可以分為通信、人機交互、Flash存儲器管理和外設管理四部分。通信的物理層功能即DTMF/FSK信號的調制解調,涉及插值、加權、相關等DSP運算。考慮到通信的實時性要求和所使用8位微控制器的數(shù)據(jù)處理能力,這些運算由專門設計的Modem硬件邏輯實現(xiàn);而在數(shù)據(jù)鏈路層,比如建立和釋放與服務器的連接、超時控制、接收FSK數(shù)據(jù)幀、拆包、差錯控制、提取返回消息層的信息和相應標志位的建立等,都交給微處理器由軟件實現(xiàn)。人機交互中的鍵盤掃描要不斷判斷是否有按鍵動作發(fā)生,用軟件實現(xiàn)效率低,這里也用專門的硬件邏輯實現(xiàn)。其他人機交互功能,如菜單操作、短信編輯等,則都由軟件實現(xiàn)。Flash存儲器管理和外設管理在硬件提供了接口寄存器的情況下,由軟件實現(xiàn)。

把實時性強、運算量大和重復性強的功能交給硬件去實現(xiàn),然后在滿足系統(tǒng)性能要求的情況下,把盡可能多的任務留給片上的微控制器用軟件實現(xiàn)。這樣降低了SoC的硬件復雜度以及制造成本,同時系統(tǒng)也可以獲得最大的靈活性。

3 SoC的軟硬件協(xié)同設計

3.1 對微控制器核的配置和擴展

DW8051_core是Synopsys公司提供的一個與8051指令兼容的8位微控制器IP核。它采用4個時鐘周期為1個指令周期的模式,在時鐘周期相同的情況下,處理能力是標準8051的3倍。DW8051_core訪問程序存儲器和數(shù)據(jù)存儲器的MEM地址總線是16位總線,避免了傳統(tǒng) 8051結構中數(shù)據(jù)總線和地址總線低位的時分復用問題。

由于DW8051_core是一個IP軟核(soft core),所以可以對它進行配置和擴展。在綜合(synthesis)的時候,通過對參數(shù)文件的設置,可以選擇配置內部RAM是128字節(jié)還是256字節(jié);可以選擇是否使用定時/計數(shù)器2,使用1個串口還是2個串口等。用戶還可以按照DW8051_core手冊的要求使用硬件描述語言編寫硬件邏輯,擴展 SFR總線和中斷系統(tǒng)(最多可以擴展到13級中斷)[3]。

在SoC設計中,只使用到了微控制器核的1個硬件定時器(Timer0),1個外部中斷(Interrupt0),1個串行口(UART),并沒有使用DW8051_core的全部功能。那些冗余的功能只會增加系統(tǒng)的硬件負擔,所以按照最精簡的原則配置DW8051_core:使用內部128字節(jié)RAM,不使用定時/計數(shù)器2,不使用內部ROM,只使用1個串口,不擴展中斷。在DW8051_parameter.vhd文件中,作如下的參數(shù)設定 [3]可以完成上述配置:

package DW8051_parameter is

constant ram_256 : integer := 0;

constant timer2 : integer := 0;

constant rom_addr_size : integer := 0;

constant serial : integer := 0;

constant extd_intr : integer := 0;

end DW8051_parameter;

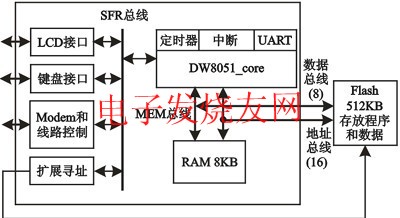

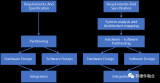

SoC中的FSK/DTMF調制解調器、LCD接口、鍵盤掃描、數(shù)據(jù)存儲器擴展頁面尋址接口以及線路狀態(tài)控制接口等,都作為片內外設連接在 DW8051_core所特有的SFR內部總線上。8 KB的片上RAM和片外512 KB的Flash存儲器AM29LV040都連接在DW8051_core的MEM總線上,如圖1所示。

圖1 經過擴展的DW8051_core SFR總線以及SoC系統(tǒng)結構

3.2 外設在SFR總線上的地址映射

DW8051_core通過SFR地址總線sfr_addr[0:7],SFR讀信號sfr_rd,SFR寫信號sfr_wr,SFR數(shù)據(jù)輸出總線sfr_data_out[0:7],數(shù)據(jù)輸入總線sfr_data_in[0:7]來訪問映射到SFR總線上的片上外設。每一個外設都通過SFR地址映射成SFR總線上的一個寄存器,如圖2所示。

對這些擴展SFR寄存器的訪問和對普通寄存器的訪問在形式上并沒有區(qū)別。當應用程序使用Keil的C51編譯器時,修改reg51.h文件可以讓編譯器確認用戶所擴展的SFR寄存器。對擴展SFR外設地址的分配可以根據(jù)設計需要而不同,但是只能使用DW8051_core沒有保留和占用的地址,否則會發(fā)生沖突。在reg51.h文件中添加以下語句讓編譯器確認擴展的寄存器:

sfr SEND_MODEM_DATA = 0xf1;/* 擴展,發(fā)送Modem數(shù)據(jù),只寫 */

sfr READ_FSK_DECODE = 0xf1;/* 擴展,讀FSK解調數(shù)據(jù),只讀 */

sfr READ_DTMF_DECODE = 0xf2;/* 擴展,讀DTMF解調數(shù)據(jù),只讀 */

sfr MODEM_STATUS = 0xf3;/* 擴展,Modem狀態(tài),只讀 */

sfr MODEM_CTRL = 0xf2;/* 擴展,Modem控制,只寫 */

sfr KEYPAD_VALUE = 0xf4;/* 擴展,讀鍵盤值,只讀 */

sfr FLASH_PAGE = 0xf5; /* 擴展,頁面尋址,只寫 */

sfr LCD_DATA = 0xf6; /* 擴展,LCD數(shù)據(jù),讀寫 */

sfr LCD_CTRL = 0xf7; /* 擴展,LCD控制,只寫 */

sfr CIRCUIT_STATUS = 0xff; /* 擴展,線路狀態(tài),只讀 */

sfr CIRCUIT_CTRL = 0xff; /* 擴展,線路控制,只寫 */

為了節(jié)約SFR總線地址資源,一些擴展的SFR寄存器在硬件上設計為只能寫、不可讀,另外一些被設計為只能讀、不可寫。這樣,二者可以復用同一個SFR總線地址,比如MODEM_CTRL和READ_DTMF_DECODE寄存器;但是這樣在需要先將那些“只寫”寄存器的內容讀出,運算后再進行寫回操作的時候就很不方便。這里采用了鏡像變量的方法,為每一個“只寫”寄存器建立一個全局變量,每次寫寄存器操作后,都對這個全局變量進行同樣的寫操作,時刻保持變量值和寄存器的內容一致,在需要讀出的時候就使用此全局變量。MODEM_CTRL寄存器的bit0控制Modem是DTMF還是FSK模式。下面以對這一位的操作為例說明。

建立它的鏡像全局變量:

unsigned char xdata modem_ctrl_mirror;

定義控制位:

#define MODEM_B0_MODE0x01// 1-DTMF, 0-FSK

圖2 片上外設在SFR總線上的物理連接

設置Modem為FSK模式:

void Modem_SetMode_FSK() {

MODEM_CTRL = modem_ctrl_mirror & (~MODEM_B0_MODE);

modem_ctrl_mirror = modem_ctrl_mirror & (~MODEM_B0_MODE);

}

在初始化程序中對這些“只寫”寄存器及其鏡像全局變量進行賦值。

void DevicesInit() {

MODEM_CTRL = MODEM_CTRL_INI;

modem_ctrl_mirror = MODEM_CTRL_INI;

}

3.3 存儲空間的劃分和映射

在物理上,把8KB的片內RAM分為兩部分,0000H~1BFFH(共7 KB)映射到數(shù)據(jù)空間,1C00H~1FFFH(共1 KB)映射到程序空間,并覆蓋Flash中程序空間的1C00H~1FFFH區(qū)域;把512 KB的Flash存儲器也分成兩部分,00000H~0FFFFH(共64 KB)映射到程序空間,剩下的10000H~7FFFFH(共448 KB)都映射到數(shù)據(jù)空間。

對微控制器核來說,可以尋址64 KB的程序空間和64 KB的數(shù)據(jù)存儲空間。對整個SoC而言,因為Flash中的程序空間有1 KB被RAM程序空間覆蓋掉,所以邏輯上它的程序空間依然是64 KB,但數(shù)據(jù)空間變?yōu)? KB+448 KB,共455 KB。微控制器核通過擴展的SFR寄存器FLASH_PAGE按32 KB×16頁的頁面方式訪問Flash存儲器,其中包括程序空間和數(shù)據(jù)空間,如圖3所示。

圖3 程序空間和數(shù)據(jù)空間的劃分和映射

在對Flash存儲器件進行寫操作后的某一段時間內(從幾十μs~幾百μs),對它進行讀操作是不能讀出一個確切值的,這是Flash存儲器件的一個特性。本設計中程序和數(shù)據(jù)存放在同一個AM29LV040 Flash存儲器中。在對Flash存儲器進行寫操作時,要不斷地從其中讀出進行寫操作的程序指令,然后對它本身進行寫操作。微控制器核在20 MHz的時鐘頻率下,指令周期大約是200 ns,即每隔200 ns左右,SoC就要從Flash存儲器中讀取一條指令。這顯然和上述的Flash存儲器特性發(fā)生了沖突。

通過對編譯環(huán)境的設定,可以把進行寫Flash操作的函數(shù)unsigned char WriteData_FLASH (unsigned char * dest, unsigned char *scr, unsigned int len) 和Flash扇區(qū)擦除函數(shù)unsigned char EraseSector_FLASH (unsigned char sector_index)定位到程序空間的1C00H~1FFFH,并備份到數(shù)據(jù)空間的0EC00H~0EFFFH。在應用程序的設備初始化函數(shù) void DevicesInit()中,調用加載函數(shù)void LoadFLASHOpToRAM(),把對Flash進行寫或者擦除操作的這1KB的程序代碼從Flash加載到RAM的程序空間。以后凡是涉及到對 Flash的寫或者擦除操作,都由硬件邏輯切換總線到RAM去執(zhí)行這一段程序代碼。這樣,以不大的RAM開銷,解決了不能同時對Flash進行讀和寫操作的矛盾。函數(shù)void LoadFLASHOpToRAM()的代碼如下:

#define PROG_RAM_DATA0xEC00

#define PROG_RAM_DATA_PAGE9

staTIc unsigned char xdata RAM_prog\[1024\] _at_ 0x1C00;

void LoadFLASHOpToRAM(){

unsigned char xdata * p;

FLASH_PAGE = PROG_RAM_DATA_PAGE;

p = (unsigned char xdata *)PROG_RAM_DATA;

memcpy(RAM_prog,p,1024);

}

4 總結

本文詳細講述了在基于微控制器IP核PSTN短消息終端SoC設計中軟硬件協(xié)同設計的方法。在合理劃分硬件和軟件任務的基礎上,使設計更好地達到了系統(tǒng)性能的要求。

電子發(fā)燒友App

電子發(fā)燒友App

評論