?

現場可編程門陣列(FPGA)技術因其提供的設計靈活性,已為系統設計人員廣泛采用。非晶硅反熔絲FPGA技術尤其有用,它可以提供一種高電路密度與低功耗,以及非易失性編程和高可靠性的組合。為了充分發揮其可靠性,FPGA廠商需要考慮反熔絲的崩潰(wear-out)機制,并通過一種設計、測試、軟件工具和編程控制的組合來避免崩潰。

非晶硅反熔絲的最基本要素是利用非晶硅作為一種電介質將兩個電極分開(圖1)。在一般情況下,這種電介質可表現出GΩ級的阻抗,可有效地隔離電極。不過,在施加一個合適的編程電壓和電流時,非晶硅的一個區域會形成一個連接電極的傳導通道(<100Ω)。

?

已編程反熔絲在其工作范圍內的表現像一個穩定、可靠的線性電阻器,而且在器件的壽命期間始終可以保持其低阻值。不過,如果已編程反熔絲單元遭損壞,它會呈現一種非線性行為,其電阻就會變得不穩定。一個損壞的已編程反熔絲的阻值可能出現從上百到上萬歐姆的變化,當巨大的電流通過它時,還可能從根本上改變其使用壽命期限。

如果所使用的器件包含損壞的反熔絲單元,就可能造成這種不穩定的現場故障。如果反熔絲是用來連接一個高或低邏輯門,那么,損壞的反熔絲仍然會使其門保持在適當的邏輯電平。不過,線路電阻和負載電容具有CMOS邏輯電路的信號傳播和切換速度的功能。那么,在一個高速電路中,損壞的反熔絲的不穩定阻值可能引起電路時序的變化。延遲的變化可能從幾納秒到幾微秒,從而導致難以診斷的現場故障。

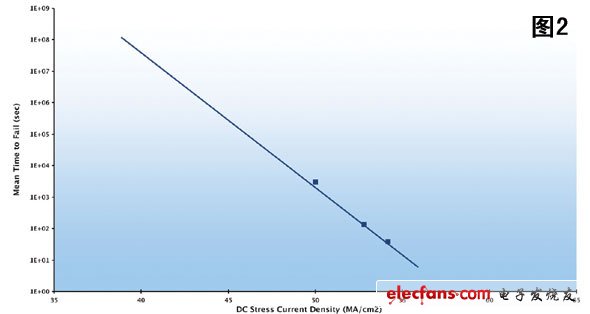

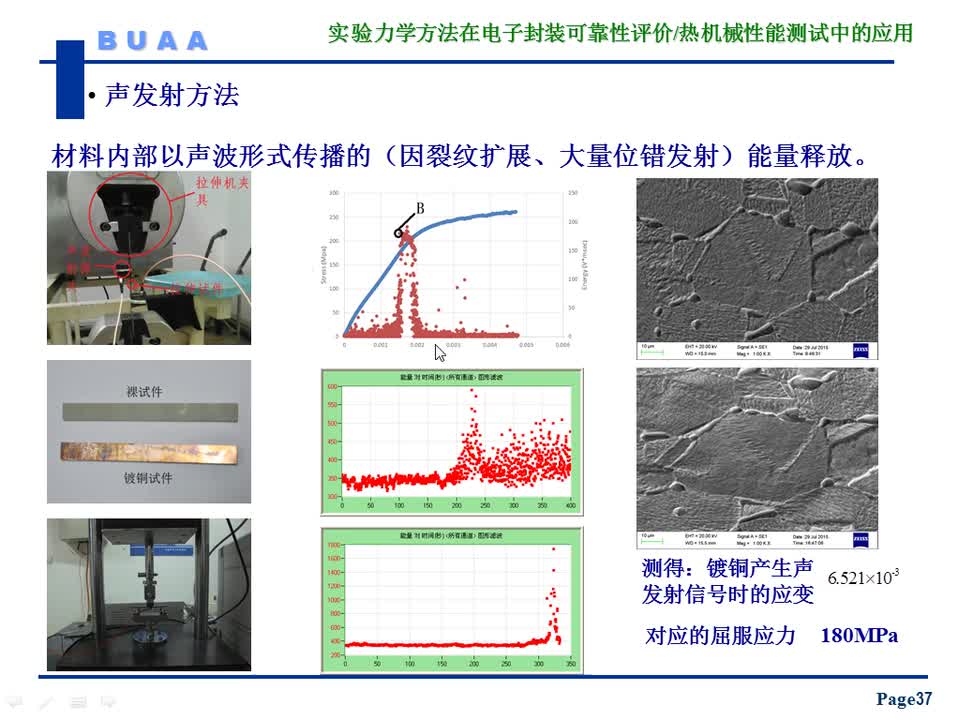

流經反熔絲的過大的工作電流是引起損壞的常見原因。圖2所示已編程反熔絲單元的平均故障時間是直流電流密度的函數,即用實際電流除以反熔絲傳導路徑的截面積。該路徑的截面積是編程電流與編程算法,以及編程脈沖的高度、寬度和極性的函數,通常為幾百平方納米。從直流數據顯示,增加電流密度流經已編程反熔絲可顯著加速故障的出現。這種巨大的依賴性也意味著減少工作電流可以顯著延長已編程反熔絲的壽命。

?

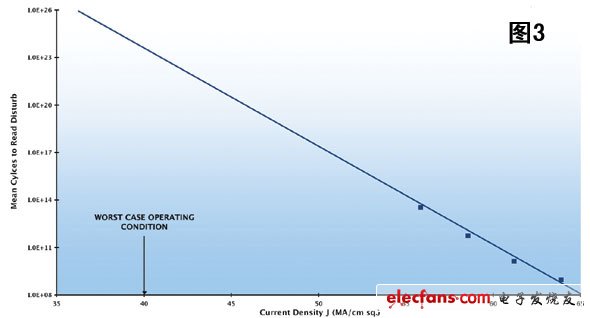

在FPGA的正常工作條件下,不會出現這樣的直流電流。通常,一個設計中的已編程反熔絲需要將一個CMOS驅動電路連接到一個容性網絡。在這種情況下,只有交流容性電流流過已編程反熔絲。作為開關頻率、負載電容、反熔絲電阻和驅動器輸出的函數的峰值交流電流,可能對已編程反熔絲造成影響,并導致在使用壽命期限內出現故障。圖3所示為在作為電流密度函數的故障發生之前,反熔絲所能保持的時鐘周期數,從而顯示出對直流電流同樣的巨大的依賴性。

控制工作條件,可以充分提高器件的可靠性。除此以外,邏輯設計、設計布線、反熔絲程序排序和測試期間的各種因素都可能影響可靠性。在以下步驟當中適當地小心就可以減少損壞已編程反熔絲的可能性:

● 設計——在邏輯設計期間,遵循一些簡單的規則可能有助于通過避免風險處境保證可靠性。防止正常工作過程中反熔絲單元的編程疏忽,例如,避免把反熔絲直接連接到任何外部信號或電源總線上。電源和接地總線的外部信號或瞬變噪聲可能在沒有編程的和正在編程的反熔絲之間產生過高的電壓。

● 制造測試——須在晶圓級對沒有編程的反熔絲進行全面測試,以保證它們的編程電壓不會過低,并使它們仍然保持其高阻值的非編程狀態。在最后測試過程中透過類似的檢查,可保證沒有編程的反熔絲不會在封裝期間受到損壞。晶圓級測試和最后測試應該驗證編程電路可以通過適當的電壓和電流。最后檢查會在編程之前,在編程器里進行,以保證反熔絲不會在最終測試之后損壞。

● 設計布線——設計布線是在創建最后的電路網絡,可以依次確定每個已編程反熔絲的有效的下游電容。若電容保持在設置閾值以下將會限制流經已編程反熔絲的峰值交流電流,因此,設計布線軟件可以通過限制下游電容來減少在大電流條件下工作的反熔絲單元的數目。對于不同速度的應用,可以選擇容性線路更短的布線,或對大的網絡進行緩沖來創建更小的容性網絡。減少工作在大電流條件下的反熔絲單元的數目可以增加已編程元件的可靠性。

● 反熔絲排序——對已編程反熔絲的狀態的控制是一個經常被忽略的步驟。隨著器件的編程,網絡開始形成。施加到一個網絡上的編程脈沖可以對連接到另一個網絡的任何反熔絲進行容性編程。所以,反熔絲可能出現損壞,從而導致生產甚至是可靠性方面的問題。時序控制器軟件應該可以防止這些情況的發生,并找出一種替代的時序。

● 編程——編程電流的控制對保證反熔絲的可靠性非常關鍵。可靠性比是由流經一個已編程反熔絲的最差情況下的峰值交流工作電流與用于編程算法的編程電流之間的比率決定的 :

設置這個比率需要充分理解編程算法和建立在反熔絲導電細絲(conductive filament)上的電流的影響。

為了使這個比率得以保持,在對每個反熔絲進行編程時,編程器應該控制其輸出的電流。如果每個脈沖期間的編程電流低于設置最小值,元件的編程就會失敗。同樣,編程電流應該再一次以較低的電壓進行測量,以保證已編程反熔絲的IV特性,并使編程路徑符合規范。當測量的電流之一超出了該規范的限制時,盡管元件可能發揮適當的作用,但可能使反熔絲連接變得不可靠。通過編程期間對元件的抑制,編程器就可以防止可能出現的現場故障。

?

將非晶硅FPGA技術與ASIC集成在一起作為嵌入式應用的開發人員,應該保證他們的設計和工具最大限度地減少對已編程反熔絲單元的壓力和因此而降低可靠性的可能性。反熔絲技術廠商正在繼續努力使人們了解和減少其技術的故障機制。那些與其技術廠商進行密切合作的ASIC設計人員可以利用這種理解創建內部設計規則,以優化基于反熔絲的設計的運行壽命。

使用現有FPGA元件的開發人員可以期待,這些可靠性原則已經融入了反熔絲技術廠商提供的器件設計、布局及布線和編程工具當中。

電子發燒友App

電子發燒友App

評論