本文首先闡述了FPGA的原理了,其次分析了FPGA比CPU和GPU快的原理,最后闡述了CPU與GPU的區(qū)別。

2018-05-31 09:00:29 15956

15956

DSP與FPGA設(shè)計(jì)的跟蹤伺服運(yùn)動(dòng)控制技術(shù)

摘 要: 在分析光電跟蹤伺服系統(tǒng)特點(diǎn)的基礎(chǔ)上,以TI公司DSP芯片TMS320F2812作為主控制芯片,采用FPGA進(jìn)行邏

2010-05-15 18:22:52 1418

1418

核心提示: 隨著FPGA技術(shù)的不斷發(fā)展和創(chuàng)新,使RISC處理器與FPGA集成、兩種系統(tǒng)的融合與優(yōu)化、FPGA與ARM核結(jié)合實(shí)現(xiàn)功能互補(bǔ)成為新一代FPGA的發(fā)展趨勢。 如今,FPGA技術(shù)正處在高速發(fā)展時(shí)

2012-08-26 10:38:24 2384

2384 DSP這幾年有點(diǎn)背,逐漸遠(yuǎn)離主流 話題 ,所以有人就有了這樣的問題:DSP會(huì)被FPGA取代嗎? 網(wǎng)友一:獨(dú)立的DSP不會(huì)被FPGA替代,但是會(huì)被增強(qiáng)了信號處理功能的 ARM 處理器替代。現(xiàn)在基本已

2022-11-29 10:25:02 4007

4007

近幾年,搭乘新興市場(智能工業(yè)、物聯(lián)網(wǎng)等)和先進(jìn)半導(dǎo)體技術(shù)快速發(fā)展先機(jī),FPGA憑借其性能優(yōu)勢不斷入侵并蠶食著DSP市場,以Altera和Xilinx主導(dǎo)的PLD廠商在各領(lǐng)域攻城拔寨勢如破竹,喜訊

2013-12-27 14:47:49 9229

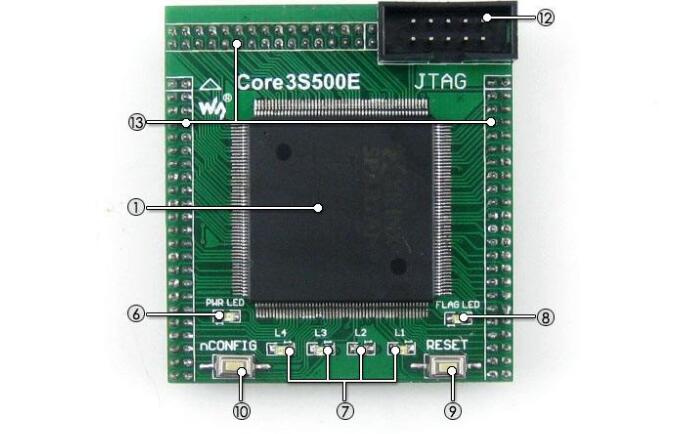

9229 V5 FPGA XC5VSX95T-1FF1136I。包含24路模擬量50Msps輸入,1路DA模擬量50Msps輸出,用于軟件無線電系統(tǒng),基帶信號處理,無線仿真平臺(tái)等。 2、技術(shù)指標(biāo) 2.1

2014-06-24 14:01:53

它們之間的關(guān)系CPU是最基本的存在,因?yàn)槟承┰颍?b class="flag-6" style="color: red">CPU的外部又包裹了部分附加功能,和CPU一起共同構(gòu)成MCU、DSP、SOC等這些芯片,因此它們都是從CPU的基礎(chǔ)上擴(kuò)展而來,基本關(guān)系我們可以

2021-11-03 08:03:45

DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計(jì),從而能夠提高算法效率,同時(shí)其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級,適合于實(shí)時(shí)視頻圖像處理,電機(jī)控制,數(shù)據(jù)采集。單DSP核心的系統(tǒng)

2016-09-24 10:41:18

和效率在數(shù)字信號處理這塊基本無人能出其右)FPGA呢相對來說可以運(yùn)用的面比較廣泛(不過也是近期的事情。其實(shí)FPGA很早就有。只是當(dāng)初設(shè)計(jì)領(lǐng)域都是通信方面的。現(xiàn)在有集成CPU和DSP以及公司提供的軟核的強(qiáng)力支持,設(shè)計(jì)面越來越廣)

2017-04-21 14:23:27

硬件DSP:是ASIC,如同CPU/GPU一樣,適合量產(chǎn),降低成本,缺點(diǎn)是(硬件)設(shè)計(jì)一旦確定,便不易于修改。FPGA :通過HDL 快速設(shè)計(jì),但成本較高,用于ASIC的prototype設(shè)計(jì)。與DSP比較軟件-編程語言DSP:DSP寫...

2021-07-28 09:06:55

操作; (8)支持流水線操作,使取指、譯碼和執(zhí)行等操作可以重疊執(zhí)行。 當(dāng)然,與通用微處理器相比,DSP

2008-06-19 15:26:55

和DSP走向融合。DSP和FPGA都在利用自身的優(yōu)勢開發(fā)新的產(chǎn)品,以滿足新應(yīng)用的需求。在一些復(fù)雜的應(yīng)用中,由于需要兼顧硬件連接、處理效率、軟件兼容性和開發(fā)難度等各方面因素,FPGA加DSP和其他

2019-06-27 07:06:16

1 引言在信息技術(shù)高速發(fā)展的今天,電子系統(tǒng)數(shù)字化已經(jīng)成為有目共睹的趨勢,從傳統(tǒng)應(yīng)用中小規(guī)模芯片構(gòu)造電路系統(tǒng)到廣泛地應(yīng)用單片機(jī),到今天DSP及FPGA在系統(tǒng)設(shè)計(jì)中的應(yīng)用,電子設(shè)計(jì)技術(shù)已邁入了一個(gè)全新

2021-10-29 08:55:40

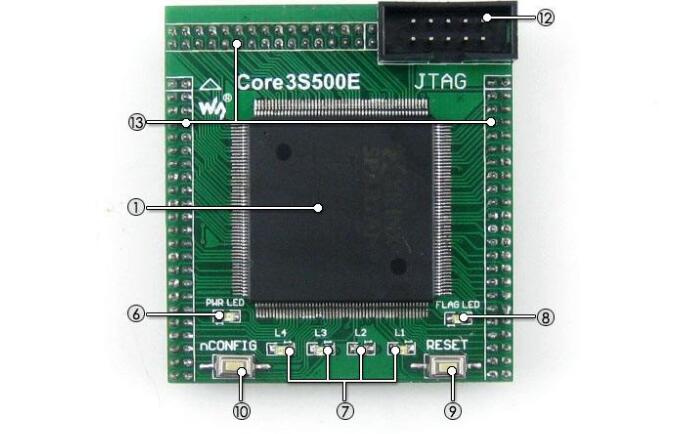

本人剛?cè)腴TFPGA,不知道如何實(shí)現(xiàn)FPGA+DSP,FPGA+ARM接口設(shè)計(jì),網(wǎng)上查詢有的說FPGA+DSP可以通過EMIF,IP核實(shí)現(xiàn),FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

Programmable Chip)的出現(xiàn),相當(dāng)多的FPGA里面都集成了DSP或者CPU,目前國際巨頭的FPGA都可以完成這樣的工作,它們不但可以集成自己的軟核,而且可以集成目前流行的PowerPC、ARM等硬核。這樣

2014-08-01 14:12:39

的描述語言Verilog-AMS等。(課程推薦:FPGA培訓(xùn))DSP使用C,匯編語言編程。(課程推薦:C6000 DSP培訓(xùn))4、功能角度FPGA普遍用于實(shí)現(xiàn)數(shù)字電路模塊,基本上能實(shí)現(xiàn)所有的數(shù)字電路

2019-05-07 01:28:40

難以與FPGA芯片抗衡。這里又引出了FPGA這個(gè)技術(shù),說到這個(gè),或許FPGA才是DSP的真正敵人。有人說融合,那么,FPGA與DSP兩個(gè)小伙伴,會(huì)走向哪里? 融合之路——FPGA與DSP,會(huì)走向哪里

2014-01-09 17:52:31

FPGA與ARM、DSP的區(qū)別在嵌入式開發(fā)領(lǐng)域,ARM是一款非常受歡迎的微處理器,其市場覆蓋率極高,DSP和FPGA則是作為嵌入式開發(fā)的協(xié)處理器,協(xié)助微處理器更好的實(shí)現(xiàn)產(chǎn)品功能。那三者的技術(shù)特點(diǎn)以及

2014-06-26 14:23:43

在嵌入式開發(fā)領(lǐng)域,ARM是一款非常受歡迎的微處理器,其市場覆蓋率極高,DSP和FPGA則是作為嵌入式開發(fā)的協(xié)處理器,協(xié)助微處理器更好的實(shí)現(xiàn)產(chǎn)品功能。那三者的技術(shù)特點(diǎn)以及區(qū)別是什么呢?下文就此問題略

2013-05-06 15:56:02

以現(xiàn)在的技術(shù)來看,FPGA是最高端的,因?yàn)?b class="flag-6" style="color: red">FPGA可以用軟件方式實(shí)現(xiàn)DSP和MCU。其實(shí)FPGA內(nèi)部是由大規(guī)模的獨(dú)立邏輯門構(gòu)成的,編程就是在做連線關(guān)系。而MCU和DSP都是數(shù)字電路,只要是數(shù)字電路

2018-08-30 09:13:25

FPGA怎么實(shí)現(xiàn):實(shí)時(shí)兩路視頻數(shù)據(jù)的融合,即實(shí)時(shí)模糊兩路圖像交接處的縫隙?

2016-02-23 13:54:54

詳見報(bào)到通知)五、培訓(xùn)對象課程適合于使用Xilinx FPGA器件進(jìn)行DSP領(lǐng)域科研和產(chǎn)品開發(fā)的具有中等水平的工程技術(shù)人員,也適合于相關(guān)專業(yè)領(lǐng)域具有相當(dāng)水平的教師和研究生。參加學(xué)習(xí)的學(xué)員應(yīng)該具有

2009-07-21 09:22:42

Q1:FPGA設(shè)計(jì)與DSP設(shè)計(jì)相比,最大的不同之處在哪里? A1:這個(gè)問題要從多個(gè)角度看。它們都用于某個(gè)功能的硬件電路實(shí)現(xiàn),但是它們的側(cè)重點(diǎn)有所不同。這里涵蓋的說一下。 1) 內(nèi)部資源

2019-06-27 06:22:39

VHDl,Verilog,還有數(shù)模混合的描述語言Verilog-AMS等。DSP使用C,匯編語言編程。3) 功能角度FPGA普遍用于實(shí)現(xiàn)數(shù)字電路模塊,基本上能實(shí)現(xiàn)所有的數(shù)字電路,傳統(tǒng)的數(shù)字功能模塊

2019-04-10 08:00:00

實(shí)時(shí)處理,就是同一時(shí)間內(nèi)能完成多個(gè)任務(wù),而且不會(huì)互相影響。DSP主要是用來計(jì)算的,比如進(jìn)行加密解密、調(diào)制解調(diào)等,優(yōu)勢是強(qiáng)大的數(shù)據(jù)處理能力和較高的運(yùn)行速度;FPGA可以用VHDL或verilog HDL來編程

2021-09-08 17:49:20

ARM、DSP、FPGA的技術(shù)特點(diǎn)和區(qū)別ARM(Advanced RISC Machines)是微處理器行業(yè)的一家知名企業(yè),設(shè)計(jì)了大量高性能、廉價(jià)、耗能低的RISC處理器、相關(guān)技術(shù)及軟 件。ARM

2013-03-14 16:12:07

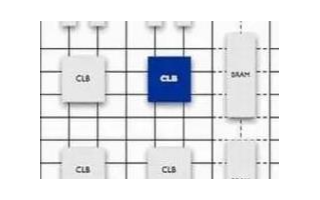

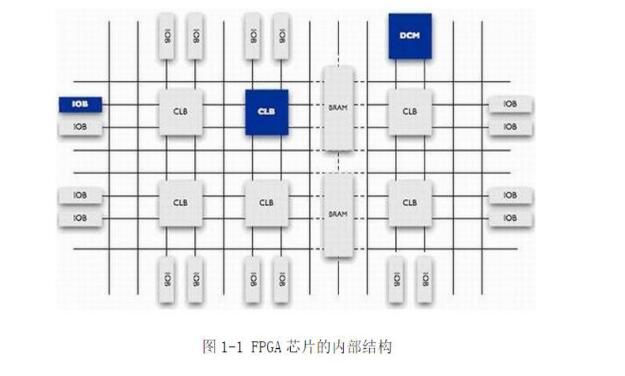

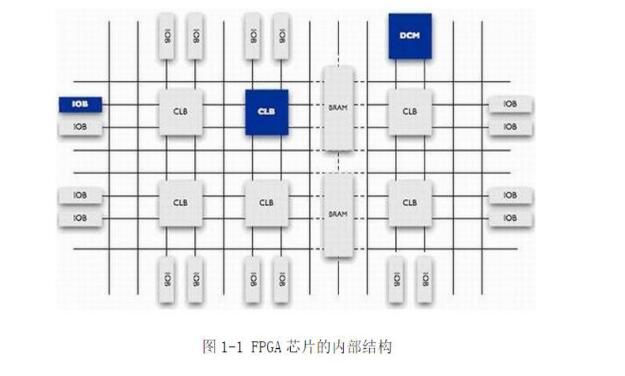

內(nèi)操作的多個(gè)硬件地址產(chǎn)生器;(7)可以并行執(zhí)行多個(gè)操作;(8)支持流水線操作,使取指、譯碼和執(zhí)行等操作可以重疊執(zhí)行。當(dāng)然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。FPGA是英文Field

2017-11-16 10:57:02

,其市場覆蓋率極高,DSP和FPGA則是作為嵌入式開發(fā)的協(xié)處理器,協(xié)助微處理器更好的實(shí)現(xiàn)產(chǎn)品功能。那三者的技術(shù)特點(diǎn)以及區(qū)別是什么呢?下文就此問題略做總結(jié)。ARM(Advanced RISC

2018-11-19 11:07:49

ARM、DSP、FPGA的技術(shù)特點(diǎn)和區(qū)別是什么?ARM(Advanced RISC Machines)是微處理器行業(yè)的一家知名企業(yè),設(shè)計(jì)了大量高性能、廉價(jià)、耗能低的RISC處理器、相關(guān)技術(shù)及軟件。ARM架構(gòu)是面向低預(yù)算市場設(shè)計(jì)的第一款RISC微處理器,基本是32位單片機(jī)的行業(yè)標(biāo)準(zhǔn),它...

2021-07-19 06:36:22

,其中包含完整系統(tǒng)并有嵌入軟件的全部內(nèi)容。同時(shí)它又是一種技術(shù),用以實(shí)現(xiàn)從確定系統(tǒng)功能開始,到軟/硬件劃分,并完成設(shè)計(jì)的整個(gè)過程。 ARM、MCU、DSP、FPGA、SOC的比較 1、采用架構(gòu)

2017-04-13 08:55:14

HDLC一般只能用于個(gè)別路數(shù)的低速信號處理。FPGA采用硬件技術(shù)處理信號,又可以通過軟件反復(fù)編程使用,能夠兼顧速度和靈活性,并能并行處理多路信號,實(shí)時(shí)性能能夠預(yù)測和仿真。DSP采用軟件技術(shù)處理信號,也可以

2011-03-17 10:23:56

,MCU主要是工業(yè)控制領(lǐng)域,DSP用途也比較廣。比如說DSP可以實(shí)現(xiàn)MP3解碼,電機(jī)控制等。它的特點(diǎn)是處理速度比較快。 CPU(Central Processing Unit,中央處理器)發(fā)展出來三個(gè)

2017-06-29 11:37:24

專業(yè)從事PCB抄板服務(wù),能讓技術(shù)完美的融合。【解密專家+V信:icpojie】 技術(shù)變革需要技術(shù)融合的支撐 技術(shù)融合就是將不相同的技術(shù)或者是裝置等融入一個(gè)系統(tǒng)里面,形成一個(gè)整體。其中“數(shù)字融合”、“三網(wǎng)

2017-06-21 15:45:19

及路線圖詳見報(bào)到通知)五、培訓(xùn)對象課程適合于使用Xilinx FPGA器件進(jìn)行DSP領(lǐng)域科研和產(chǎn)品開發(fā)的具有中等水平的工程技術(shù)人員,也適合于相關(guān)專業(yè)領(lǐng)域具有相當(dāng)水平的教師和研究生。參加學(xué)習(xí)的學(xué)員應(yīng)該具有

2009-07-21 09:20:11

VHDl,Verilog,還有數(shù)模混合的描述語言Verilog-AMS等。DSP使用C,匯編語言編程。3) 功能角度FPGA普遍用于實(shí)現(xiàn)數(shù)字電路模塊,基本上能實(shí)現(xiàn)所有的數(shù)字電路,傳統(tǒng)的數(shù)字功能模塊

2019-08-11 08:00:00

VHDl,Verilog,還有數(shù)模混合的描述語言Verilog-AMS等。(課程推薦:FPGA培訓(xùn))

??DSP使用C,匯編語言編程。(課程推薦:C6000 DSP培訓(xùn))

4、功能角度

FPGA普遍用于

2023-06-01 11:03:14

語言Verilog-AMS等。(課程推薦:FPGA培訓(xùn)) DSP使用C,匯編語言編程。(課程推薦:C6000 DSP培訓(xùn)) 4、功能角度 FPGA普遍用于實(shí)現(xiàn)數(shù)字電路模塊,基本上能實(shí)現(xiàn)所有的數(shù)字電路,傳統(tǒng)

2016-12-23 16:56:04

dB時(shí)能測到雷達(dá)信號,使雷達(dá)的有效作用距離提高。本文主要介紹基于DSP和FPGA技術(shù)的低信噪比情況下雷達(dá)信號的檢測。

2019-07-04 06:55:39

dB時(shí)能測到雷達(dá)信號,使雷達(dá)的有效作用間隔進(jìn)步。本文主要先容基于DSP和FPGA技術(shù)的低信噪比情況下雷達(dá)信號的檢測。1 設(shè)計(jì)思想 本技術(shù)的設(shè)計(jì)思想主要是通過對接收到的雷達(dá)信號進(jìn)行高速A/D采樣,然后

2018-08-15 09:43:14

1 引言 隨著信息技術(shù)革命的深入和計(jì)算機(jī)技術(shù)的飛速發(fā)展,低速、低可靠性的單片機(jī)以及小規(guī)模的集成電路已經(jīng)越來越不能滿足需要,正逐漸被DSP與可編程邏輯器件(如FPGA、CPLD)所取代。一方面

2019-07-12 08:32:59

以降低系統(tǒng)速度為代價(jià)。從FPGA發(fā)展趨勢和DSP運(yùn)算要求看,系統(tǒng)速度指標(biāo)的意義比面積指標(biāo)更趨重要,需要我們進(jìn)一步深入研究提高芯片的最高工作速度的設(shè)計(jì)策略。我們需要討論一下基于FPGA的DSP系統(tǒng)設(shè)計(jì)中的流水線技術(shù)主要應(yīng)用在哪些方面?

2019-08-02 06:03:48

本文介紹基于Android的多傳感器信息融合技術(shù)在氣溶膠自動(dòng)化檢測中的應(yīng)用。

2021-05-11 06:22:08

dB時(shí)能測到雷達(dá)信號,使雷達(dá)的有效作用距離提高。有哪些方法能檢測低信噪比雷達(dá)信號 ? 可以利用DSP和FPGA技術(shù)嗎?

2019-08-05 07:30:20

無法滿足目前市場的需求,必須選用支持業(yè)務(wù)應(yīng)用靈活的系統(tǒng)架構(gòu),易于企業(yè)管理維護(hù)的管理平臺(tái)軟件來運(yùn)行和操作,不同的行業(yè)其應(yīng)用軟件也有著較大的區(qū)別。安防軟件正在得到更多的業(yè)內(nèi)人士的認(rèn)可,未來的道路將是走向融合

2013-07-30 09:57:48

控制密集型,許多人都用dsp高算法,用fpga 作外圍控制電路。去年xilinx在北京介紹FPGA和DSP融合的時(shí)候,大有席卷DSP和FPGA市場之勢。但后來在實(shí)際中發(fā)現(xiàn)其阻力也是不小的,關(guān)鍵是很難搭配

2018-10-10 18:02:03

雖說FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),但有什么方法去證明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)是存在的呢?

2021-04-08 06:54:33

ARM、DSP及FPGA的技術(shù)特點(diǎn)和區(qū)別

2019-10-12 07:13:50

在20?A以下。因此,Cypress PSoC4 BLE提供了5種功耗模式,包括動(dòng)態(tài)、睡眠、深度睡眠、休眠和停止。最低休眠功耗低至60nA。 無線技術(shù)終將會(huì)走向融合。 就目前來看,物聯(lián)網(wǎng)中的設(shè)備

2016-06-29 11:19:34

與技術(shù)走向;5、最資深工程師等200多位嘉賓與會(huì),準(zhǔn)握未來顯示運(yùn)營趨勢 報(bào)名鏈接:http://www.nxhydt.com/topic/seminar/201509security

2015-08-18 16:50:28

我需要在視頻切換時(shí),進(jìn)行淡入淡出的切換效果,具體算法很簡單,就是yuv數(shù)據(jù)按照一定比例融合。對于1080數(shù)據(jù),像素非常多,每像素都要運(yùn)算,總運(yùn)算量是每秒千萬級別的,導(dǎo)致vpss所在的m3的cpu

2019-08-26 08:44:23

我做的一個(gè)基于DSP的系統(tǒng)中,DSP做主處理器,控制著整個(gè)系統(tǒng),包括信號處理,整體調(diào)度等;選擇了一塊Xilinx的FPGA做FIFO UART和系統(tǒng)的邏輯控制和譯碼。DSP的時(shí)鐘輸入為15MHz

2023-06-19 06:43:17

、技術(shù)指標(biāo)以xilinx 公司K7系列FPGA XC7K325T-1FFG900和TI公司的TMS320C6657為主芯片。FPGA外接1組DDR3 ,共128MX32bit容量。DSP外接一組

2018-06-01 17:48:37

和航空航天等嵌入式應(yīng)用領(lǐng)域,目前的市場需求是:以更低成本、更低功耗、更小尺寸處理日益復(fù)雜的功能。這些市場需求正推動(dòng)著FPGA、CPU、DSP等不同技術(shù)走向融合。 對FPGA技術(shù)來說,早期研發(fā)在5年前就已開始

2011-07-21 10:52:00

作者:Reg ZatrepalekHardent 公司 DSP/FGPA 設(shè)計(jì)專家rzatrepalek@hardent.com本文以實(shí)踐為基礎(chǔ),對 DSP和 FPGA 技術(shù)進(jìn)行了簡要回顧,并詳細(xì)

2018-08-15 09:46:21

FPGA實(shí)現(xiàn)DSP應(yīng)用

摘要:具有系統(tǒng)級性能的FPGA在半導(dǎo)體工藝的線寬達(dá)到深亞微米后更進(jìn)一步按信號處理的要求改進(jìn)器件結(jié)構(gòu)和性能,不僅可實(shí)現(xiàn)VLSI DSP,且具有系統(tǒng)

2010-04-01 15:39:54 14

14 FPGA的DSP應(yīng)用

近年來由于多媒體技術(shù)和無線通信的發(fā)展,對DSP應(yīng)用的要求不斷地增長,但是這些應(yīng)用對信號處理要求高,需要采用處理速度高的硬件來實(shí)現(xiàn)DSP,所以,隨著CMOS工藝的

2010-04-07 14:25:58 16

16 本文首先簡單介紹某小型基于DSP和FPGA的導(dǎo)航計(jì)算機(jī)系統(tǒng),然后根據(jù)其子系統(tǒng)輸出的有效信息設(shè)計(jì)可行的信息融合算法;針對其子系統(tǒng)有效輸出結(jié)果的時(shí)間不同步性,結(jié)合系統(tǒng)實(shí)際情

2010-08-06 17:01:05 21

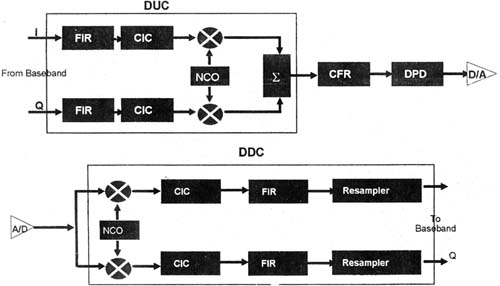

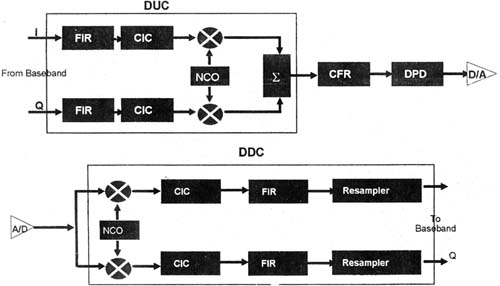

21 FPGA和DSP組合在無線基站中的應(yīng)用

在自動(dòng)控制產(chǎn)品中,CPD+DSP+MCU的構(gòu)架是目前最為流行的成熟方案,而在通訊產(chǎn)品中,大量使用FPGA設(shè)計(jì),合理使用FPGA

2009-10-12 11:20:11 975

975

基于DSP和FPGA技術(shù)的低信噪比雷達(dá)信號檢測

我國目前的海事雷達(dá)大多為進(jìn)口雷達(dá),有效探測距離小,在信噪比降為3 dB時(shí)已經(jīng)無法識別信號。隨著微電子技術(shù)的迅猛發(fā)展,高速

2009-11-05 10:33:24 496

496

基于DSP和FPGA的通用圖像處理平臺(tái)設(shè)計(jì)

摘要:設(shè)計(jì)一種基于DSP和FPGA架構(gòu)的通用圖像處理平臺(tái),運(yùn)用FPGA實(shí)現(xiàn)微處理器接口設(shè)計(jì),并對圖像數(shù)據(jù)進(jìn)行簡單預(yù)處理,利用DSP

2010-02-01 11:10:21 1379

1379

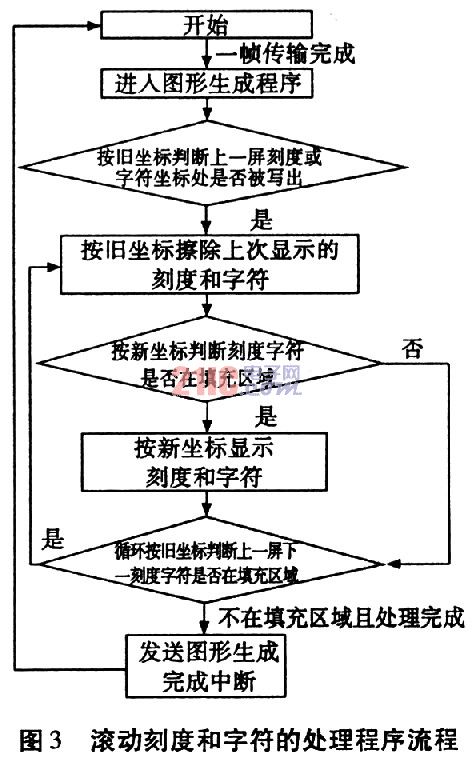

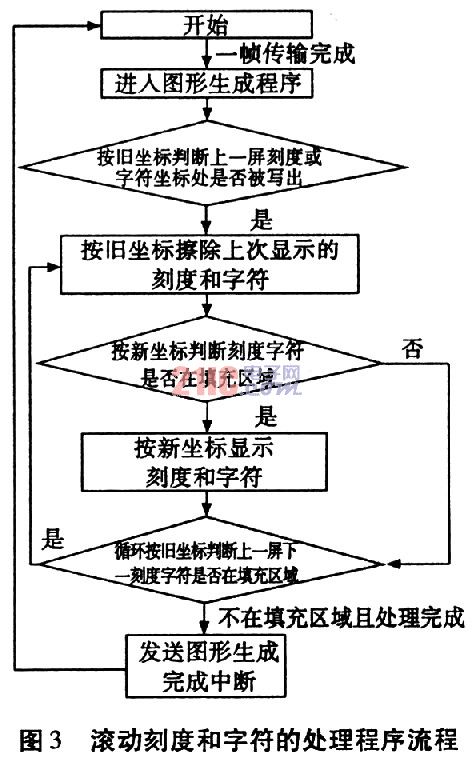

本文設(shè)計(jì)了基于DSP與FPGA的系統(tǒng)結(jié)構(gòu),采用了軟硬件填充的圖形處理方法,先由DSP軟件完成圖形輪廓生成,然后FPGA硬件圖形處理器根據(jù)圖形輪廓完成耗時(shí)的圖形填充,使系統(tǒng)在實(shí)時(shí)性

2010-07-01 11:02:38 988

988

ARM、DSP、FPGA的技術(shù)特點(diǎn)和區(qū)別

2010-09-03 21:41:26 2310

2310 摘要:為了實(shí)現(xiàn)高速HDLC通訊協(xié)議,設(shè)計(jì)了DSP+FPGA結(jié)構(gòu)的485通訊接口,接口包括DSP、FPGA、485轉(zhuǎn)換等硬件電路,以及DSP與FPGA之間的數(shù)據(jù)交換程序和FPGA內(nèi)部狀態(tài)機(jī);其中DSP用于實(shí)現(xiàn)數(shù)據(jù)控制,FPGA用于實(shí)現(xiàn)HDLC通訊協(xié)議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 基于現(xiàn)場可編程(FPGA)技術(shù)和硬件描述語言VHDL的設(shè)計(jì)和綜合,通過自頂向下的設(shè)計(jì)方法和模塊化設(shè)計(jì)思想,在Quartus II環(huán)境下能定制、仿真、下載驗(yàn)證和實(shí)現(xiàn)CPU功能。通過VHDL語言定制了運(yùn)算器ALU模塊和調(diào)用宏模塊定制了RAM模塊,介紹了基于FPGA的CPU設(shè)計(jì)方法,

2011-03-15 17:39:19 177

177 System Generator 工具由 MathWorks 與 Xilinx 合作開發(fā)而成,DSP 設(shè)計(jì)人員可使用 MATLAB 和Simulink 工具在 FPGA 內(nèi)進(jìn)行開發(fā)和仿真來完善 DSP 設(shè)計(jì)。 該工具為系統(tǒng)級 DSP 設(shè)計(jì)與 FPGA 硬件實(shí)現(xiàn)的融合起

2011-05-11 18:36:23 224

224 為滿足導(dǎo)航系統(tǒng)設(shè)計(jì)的小型化、實(shí)時(shí)性要求,本文提出了一種基于FPGA + DSP 的實(shí)現(xiàn)方案。該方案的設(shè)計(jì)思路是:將FPGA 映射到DSP EMIF 的一段地址空間,并用FPGA 來完成多通道信號的采集; DSP 根

2011-09-13 14:32:08 77

77 對FPGA技術(shù)來說,早期研發(fā)在5年前就已開始嘗試采用多核和硬件協(xié)處理加速技術(shù)朝系統(tǒng)并行化方向發(fā)展。在實(shí)際設(shè)計(jì)中,FPGA已經(jīng)成為CPU的硬件協(xié)加速器,很多芯片廠商采用了硬核或軟核CPU+FPGA的

2011-09-23 15:30:06 770

770 Alter FPGA的設(shè)計(jì)流程以及DSP設(shè)計(jì).

2012-03-16 15:52:07 127

127 對FPGA這種特殊芯片產(chǎn)品的認(rèn)識開始于10年前對Altera公司的認(rèn)識。Altera公司獨(dú)特的嚴(yán)謹(jǐn)氣質(zhì)與FPGA這種芯片非常契合。多年來跟蹤報(bào)道Altera在FPGA技術(shù)上的不斷創(chuàng)新,加之后來有機(jī)會(huì)結(jié)識賽

2012-07-19 09:44:55 570

570 設(shè)計(jì)了一種基于DSP與FPGA的運(yùn)動(dòng)控制器。該控制器以DSP為控制核心,用FPGA構(gòu)建運(yùn)動(dòng)控制器與傳感器以及電機(jī)驅(qū)動(dòng)器的接口電路。充分發(fā)揮了DSP強(qiáng)大的運(yùn)算能力和FPGA的并行處理能力。具有

2012-10-26 15:21:51 93

93 DSP之cpu_timer教程,很好的DSP自學(xué)資料,快來學(xué)習(xí)吧。

2016-04-15 16:16:02 13

13 dsp fpga 電路 打標(biāo)機(jī)上用的主板

2016-06-27 15:24:08 7

7 隨著越來越多的應(yīng)用趨向于既具高速處理又兼具靈活性的系統(tǒng),CPU+FPGA的融合方案早年前就被付諸實(shí)踐,如今比比皆是。

2016-08-17 14:38:23 1366

1366 基于DSP和FPGA技術(shù)的細(xì)胞圖像采集系統(tǒng)設(shè)計(jì)

2016-08-26 12:57:52 15

15 基于FPGA的多幅圖像融合疊加的設(shè)計(jì)與實(shí)現(xiàn)

2016-08-30 15:10:14 11

11 FPGA與ARM、DSP的區(qū)別

2017-03-15 08:00:00 9

9 摘要 利用異步FIFO實(shí)現(xiàn)FPGA與DSP進(jìn)行數(shù)據(jù)通信的方案。FPGA在寫時(shí)鐘的控制下將數(shù)據(jù)寫入FIFO,再與DSP進(jìn)行握手后,DSP通過EMIFA接口將數(shù)據(jù)讀入。文中給出了異步FIFO的實(shí)現(xiàn)

2017-10-30 11:48:44 1

1 今天,FPGA越來越多地應(yīng)用在多種DSP中。我們預(yù)計(jì)這一趨勢在未來幾年會(huì)更加明顯。美國調(diào)查機(jī)構(gòu)Berkeley設(shè)計(jì)技術(shù)公司做了上述預(yù)測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 10:48:09 1

1 今天,FPGA越來越多地應(yīng)用在多種DSP中。我們預(yù)計(jì)這一趨勢在未來幾年會(huì)更加明顯。美國調(diào)查機(jī)構(gòu)Berkeley設(shè)計(jì)技術(shù)公司做了上述預(yù)測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 13:58:57 7

7 存儲(chǔ)以及疊加融合等技術(shù)在FPGA硬件平臺(tái)上實(shí)現(xiàn)。結(jié)果表明,該系統(tǒng)能達(dá)到預(yù)期效果,疊加融合畫面效果良好,能夠滿足工程應(yīng)用的需求。 視頻圖像疊加融合技術(shù)可以將兩路視頻圖像信號進(jìn)行疊加融合并輸出到一臺(tái)顯示器上進(jìn)行顯示。

2017-11-22 08:32:05 3912

3912

針對噴油器霧化粒徑測量系統(tǒng)實(shí)時(shí)數(shù)據(jù)處理的特點(diǎn),將FPGA技術(shù)與DSP技術(shù)相結(jié)合,研究一種基于FPGA和DSP的電控噴油器粒徑檢測系統(tǒng);為滿足動(dòng)態(tài)測量的要求,設(shè)計(jì)了應(yīng)用高性能的多路開關(guān)和超低輸入偏置電流運(yùn)放的多通道微電流高速采集板;詳細(xì)介紹了檢測系統(tǒng)中基于FPGA和DSP的軟硬件設(shè)計(jì)和工作原理。

2017-12-06 17:03:04 1728

1728

CPU+FPGA的并行處理是目前的發(fā)展趨勢這種處理方式將大行其道。

2018-01-02 15:54:07 15989

15989 FPGA仿真篇-使用腳本命令來加速仿真二 基于FPGA的HDMI高清顯示借口驅(qū)動(dòng) 基于FPGA灰度圖像高斯濾波算法的實(shí)現(xiàn) FPGA為什么比CPU和GPU快 基于Xilinx FPGA的視頻圖像采集

2018-02-20 20:49:00 1479

1479 本文首先分析了FPGA是否會(huì)取代DSP,其次介紹了FPAG結(jié)構(gòu)特點(diǎn)與優(yōu)勢及DSP的基本結(jié)構(gòu)和特征,最后闡述了FPGA與DSP兩者之間的區(qū)別。

2018-05-31 09:51:25 35711

35711

如下圖,FPGA作為協(xié)處理器,CPU把指令寫入內(nèi)存,FPGA從內(nèi)存讀取指令執(zhí)行,并把計(jì)算結(jié)果寫入內(nèi)存。這種模式的優(yōu)點(diǎn)是簡單易行,協(xié)處理器和CPU分離。瓶頸在于共享內(nèi)存,限制了性能,同時(shí)由于通過內(nèi)存

2018-06-20 15:17:10 12724

12724 FPGA是一種可編程的硅芯片,DSP是數(shù)字信號處理,當(dāng)系統(tǒng)設(shè)計(jì)人員在項(xiàng)目的架構(gòu)設(shè)計(jì)階段就面臨到底采用FPGA還是DSP的重要問題。本文將首先分別介紹FPGA和DSP的特點(diǎn),然后再從內(nèi)部資源、編程語言、功能多個(gè)角度解析兩者的不同。

2018-09-29 16:43:35 30755

30755 歷經(jīng)6年的超融合,未來將走向何方? 從2013年國內(nèi)超融合概念的出現(xiàn),到2016年超融合元年創(chuàng)業(yè)的高潮,再到如今的2019年落地到用戶的具體場景,在短短的六年內(nèi),超融合就實(shí)現(xiàn)了從新興技術(shù)到商業(yè)化落地

2019-01-24 12:45:02 534

534 目前數(shù)字電路系統(tǒng)設(shè)計(jì)領(lǐng)域公認(rèn)的基礎(chǔ)性技術(shù)分別是CPU、DSP和FPGA。其中FPGA技術(shù)發(fā)展迅速,正在逐漸融合CPU和DSP的功能。FPGA不僅可以解決電子系統(tǒng)小型化、低功耗、高可靠性等問題,而且其開發(fā)周期短、投入少,芯片價(jià)格又在不斷下降。

2020-07-14 14:09:48 723

723 型到大型的幾乎所有數(shù)字電路系統(tǒng),dsp主要完成復(fù)雜的數(shù)字信號處理,如fft,通常一個(gè)復(fù)雜系統(tǒng)可以由單片機(jī)、arm、fpga、dsp中的一種或幾種構(gòu)成,各有優(yōu)勢和不足。 dsp通常用于運(yùn)算密集型,fpga用于控制密集型,許多人都用dsp高算法,用fpga作外圍控制

2020-10-25 09:50:06 3085

3085 隨著AMD收購Xilinx一錘定音,加上幾年前英特爾將FPGA老二Altera收入囊中,FPGA狀元、榜眼相繼被豪強(qiáng)納入麾下,此際FPGA探花——lattice會(huì)“心有戚戚”嗎?Lattice的運(yùn)命又將走向何方?

2020-11-04 17:44:48 5647

5647 它們之間的關(guān)系CPU是最基本的存在,因?yàn)槟承┰颍?b class="flag-6" style="color: red">CPU的外部又包裹了部分附加功能,和CPU一起共同構(gòu)成MCU、DSP、SOC等這些芯片,因此它們都是從CPU的基礎(chǔ)上擴(kuò)展而來,基本關(guān)系我們可以

2021-10-28 15:51:14 35

35 廣州星嵌DSP/ARM/FPGA 選型手冊2023

2023-05-05 10:24:22 15

15

電子發(fā)燒友App

電子發(fā)燒友App

評論