引言

隨著以太網(wǎng)技術(shù)的飛速發(fā)展,工業(yè)以太網(wǎng)漸漸成為自動(dòng)化控制系統(tǒng)里主流的高速率的通信方式,工業(yè)以太網(wǎng)技術(shù)已經(jīng)成為一個(gè)獨(dú)立發(fā)展的分支。EPA是我國第一個(gè)擁有自主知識(shí)產(chǎn)權(quán)、并被國際標(biāo)準(zhǔn)化組織接收和采用的工業(yè)自動(dòng)化標(biāo)準(zhǔn)。該標(biāo)準(zhǔn)是一種基于以太網(wǎng)、無線局域網(wǎng)、藍(lán)牙等信息網(wǎng)絡(luò)通信技術(shù)的,適用于工業(yè)自動(dòng)化控制系統(tǒng)裝置與儀器儀表間、工業(yè)自動(dòng)化儀器儀表相互間數(shù)據(jù)通信的工業(yè)控制網(wǎng)絡(luò)通信標(biāo)準(zhǔn)。

大量的EPA現(xiàn)場設(shè)備都是通過加裝EPA通信卡來進(jìn)行通信,該通信卡的處理器多數(shù)采用ARM核。近年來,隨著半導(dǎo)體技術(shù)的飛速發(fā)展,傳統(tǒng)的芯片設(shè)計(jì)方法正在進(jìn)行一場革命,其標(biāo)志就是系統(tǒng)芯片(SoC)被業(yè)界廣泛接受,并成為研究和開發(fā)的熱點(diǎn)。隨著SoC技術(shù)應(yīng)運(yùn)而生的是SOPC 技術(shù)。它結(jié)合了SoC和FPGA的優(yōu)點(diǎn),可裁減、可擴(kuò)充、可升級(jí),并具備軟硬件在系統(tǒng)中可編程的功能。SOPC能夠提供更好的性能以及更低的功耗,有效節(jié)省電路板空間并降低產(chǎn)品的總成本,電子工業(yè)正逐漸向SOPC設(shè)計(jì)轉(zhuǎn)移,使SOPC成為現(xiàn)代電子系統(tǒng)的最佳選擇之一。在充分研究EPA網(wǎng)絡(luò)通信和SOPC技術(shù)的基礎(chǔ)上,開發(fā)了一種基于SOPC技術(shù)的EPA控制器。

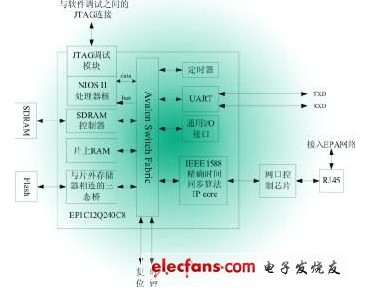

圖1基于FPGA的EPA控制器的硬件結(jié)構(gòu)框圖

SOPC技術(shù)

SOPC技術(shù)是美國Altera公司于2000年最早提出的,并同時(shí)推出了相應(yīng)的開發(fā)軟件Quartus II。SOPC是基于FPGA解決方案的SoC,與ASIC的SoC解決方案相比,SOPC系統(tǒng)及其開發(fā)技術(shù)具有更多的特色,并具備以下的基本特征:至少包含一個(gè)以上的嵌入式處理器IP核;具有小容量片內(nèi)高速RAM資源;豐富的IP核資源可供靈活選擇;有足夠的片上可編程邏輯資源;處理器調(diào)試接口和FPGA編程接口共用或并存;可包含部分可編程模擬電路;單芯片、低功耗。

SOPC是一種新的系統(tǒng)設(shè)計(jì)技術(shù),也是一種新的軟硬件綜合設(shè)計(jì)技術(shù)。通過它,可以很快地將硬件系統(tǒng)(包括微處理器,存儲(chǔ)器,外設(shè)以及用戶邏輯電路等)和軟件設(shè)計(jì)都放在一個(gè)可編程的FPGA芯片中,以達(dá)到系統(tǒng)的IC設(shè)計(jì)。這種設(shè)計(jì)方式,具有開發(fā)周期短以及系統(tǒng)可修改等優(yōu)點(diǎn)。設(shè)計(jì)完成的SOPC可以通過HARDCOPY轉(zhuǎn)為ASIC芯片,從而可以實(shí)現(xiàn)快速量產(chǎn)。

EPA現(xiàn)場控制器設(shè)計(jì)

針對控制系統(tǒng)中連接管理網(wǎng)、控制網(wǎng)和現(xiàn)場設(shè)備單元的要求,采用SOPC技術(shù)、現(xiàn)場總線技術(shù)和自動(dòng)控制技術(shù),設(shè)計(jì)一種適用于EPA工業(yè)以太網(wǎng)的控制器,并在其可編輯軟核的CPU處理器上實(shí)現(xiàn)了實(shí)時(shí)操作系統(tǒng)及EPA通信協(xié)議棧。該EPA現(xiàn)場控制器可實(shí)現(xiàn)實(shí)時(shí)控制信息的輸入輸出,并對以太網(wǎng)上的其他的EPA設(shè)備進(jìn)行監(jiān)控、顯示和故障報(bào)警。本文將針對該EPA控制器的基于SOPC技術(shù)的CPU核心處理模塊和通信處理模塊分別進(jìn)行說明。

EPA現(xiàn)場控制器的硬件設(shè)計(jì)總體方案

圖1是EPA現(xiàn)場控制器的硬件系統(tǒng)結(jié)構(gòu)框圖。整個(gè)設(shè)計(jì)中,硬件上實(shí)現(xiàn)EP1C12Q240C8芯片、LAN91C111芯片的外圍接口電路的設(shè)計(jì);實(shí)現(xiàn)了串口通信和網(wǎng)絡(luò)通信的設(shè)計(jì);實(shí)現(xiàn)了復(fù)位電路、JTAG、時(shí)鐘電路、電源電路的設(shè)計(jì);實(shí)現(xiàn)了鍵盤電路、LCD顯示電路、蜂鳴器報(bào)警電路的設(shè)計(jì);實(shí)現(xiàn)了HY57V641620芯片、AM29LV160芯片外圍電路的設(shè)計(jì),拓展了豐富的存儲(chǔ)器資源,可移植linux、windows CE操作系統(tǒng)等;拓展了總線接口,可以根據(jù)工業(yè)現(xiàn)場的實(shí)際需要接入相應(yīng)的板卡(如DI/DO模塊、AI/AO模塊,實(shí)現(xiàn)與現(xiàn)場數(shù)據(jù)之間的數(shù)模、模數(shù)轉(zhuǎn)換、拓展MMC存儲(chǔ)卡,拓展其存儲(chǔ)容量等)。

在設(shè)計(jì)時(shí),考慮到由于該控制器的結(jié)構(gòu)、功能較為復(fù)雜,涉及到的器件種類較多。所以在設(shè)計(jì)時(shí),將硬件板卡分為兩部分來做。第一部分:CPU核心處理模塊,包含CPU處理器EP1C12Q240C8、存儲(chǔ)器(FLASH、SDRAM)、電源部分、時(shí)鐘源、JTAG、EPCS下載口和復(fù)位電路。第二部分:通信處理模塊,包含網(wǎng)絡(luò)通信(LAN91C111網(wǎng)卡芯片和RJ45)、串口通信(MAX3232)、LCD接口、鍵盤接口和蜂鳴器。

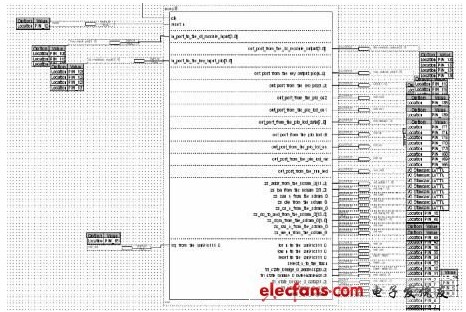

圖2 芯片系統(tǒng)結(jié)構(gòu)框圖

基于SOPC技術(shù)的CPU核心處理模塊

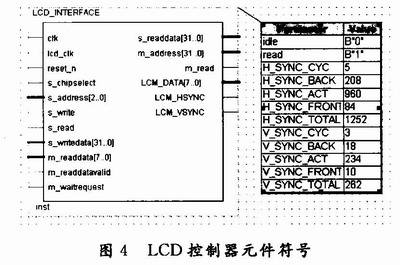

整個(gè)方案的實(shí)現(xiàn)是以接入實(shí)時(shí)工業(yè)以太網(wǎng)絡(luò)為目的,在芯片內(nèi)部實(shí)現(xiàn)部分EPA協(xié)議,同時(shí)控制器實(shí)現(xiàn)對工業(yè)以太網(wǎng)上的其他設(shè)備的監(jiān)控、顯示及數(shù)據(jù)分析。設(shè)計(jì)中采用Altera公司的新一代低成本的FPGA芯片EP1C12Q240C8芯片,該芯片包含有12060LE(邏輯單元),可根據(jù)實(shí)際需要,配置其NIOSⅡCPU軟核、與CPU相連的片內(nèi)外設(shè)和存儲(chǔ)器以及與片外存儲(chǔ)器和片外設(shè)備相連的接口等。其芯片系統(tǒng)結(jié)構(gòu)框圖如圖2所示。

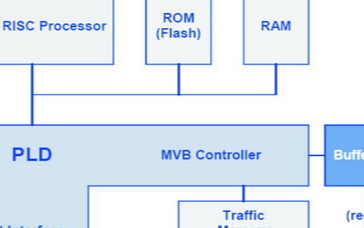

整個(gè)CPU處理器的硬軟件設(shè)計(jì)均在Quartus II 5.1版本上實(shí)現(xiàn)。NIOSⅡ處理器核是Altera公司的第二代用戶可配置的通用32位RISC軟核微處理器,是Altera公司特有的基于FPGA架構(gòu)的可配置的軟CPU內(nèi)核,其特性和外設(shè)可根據(jù)實(shí)際需要進(jìn)行增加或剪裁。所有NIOSⅡ處理器系統(tǒng)使用統(tǒng)一的指令和編程模型,并有三種類型以滿足不同設(shè)計(jì)的要求,分別是快速型、經(jīng)濟(jì)型和標(biāo)準(zhǔn)型。在本控制器中,所定制的NIOSⅡ軟核選用快速型,該內(nèi)核處理速度為49DMIPS,耗費(fèi)的邏輯門數(shù)為1400~1800LE,同時(shí)帶有硬件乘法器和硬件除法器。根據(jù)EPA網(wǎng)絡(luò)對控制器的要求,添加與CPU相連的片內(nèi)外設(shè)和片外設(shè)備接口:SDRAM控制器、片內(nèi)RAM、三態(tài)橋、UART、定時(shí)器、通用I/O口、LCD顯示驅(qū)動(dòng)電路和以太網(wǎng)接口。按照設(shè)計(jì)要求,在Quartus II 5.1版本下的對CPU的配置情況如圖3所示。FPGA芯片可根據(jù)實(shí)際需要靈活地增加功能,同樣對不必要的功能也可進(jìn)行刪減,以滿足快速、高效和低成本的設(shè)計(jì)。

在配置完CPU處理器的內(nèi)部結(jié)構(gòu)以后,按照設(shè)計(jì)需要對CPU的外圍進(jìn)行配置。由于該控制器是接入EPA網(wǎng)絡(luò),需要實(shí)現(xiàn)EPA協(xié)議,而FPGA芯片EP1C12Q240C8的內(nèi)部只有288K的RAM,所以在片外擴(kuò)展了16M bits的FLASH-AM29LV160D和64M bits的SDRAM-HY57V641620的。從外部引入12V的直流電源,經(jīng)過電平轉(zhuǎn)換以后得到3.3V和1.5V的電源,為CPU、存儲(chǔ)器及其他受電設(shè)備供電。CPU上的時(shí)鐘源使用的是50MHz的鐘振。JTAG和EPCS下載口用于硬軟件的下載。將在Quartus Ⅱ上編輯的硬件程序和軟件程序通過JTAG和EPCS下載口,下載到FLASH和RAM(片內(nèi)或者片外)中,可進(jìn)行在線調(diào)試。該復(fù)位電路是由10KW電阻、10mF電容和按鍵組成,可實(shí)現(xiàn)按鍵低電平復(fù)位和上電低電平復(fù)位。

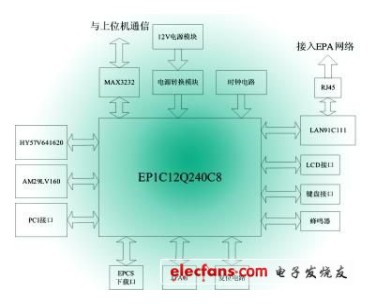

圖3 EP1C12Q240C8芯片配置情況

通信處理模塊

整個(gè)設(shè)計(jì)以FPGA芯片EP1C12Q240C8為數(shù)據(jù)處理中心,通過網(wǎng)絡(luò)通信,完成對工業(yè)以太網(wǎng)上的其他設(shè)備的數(shù)據(jù)通信,同時(shí)通過MAX3232實(shí)現(xiàn)和上位機(jī)的串口通信。在該模塊中,加入了LCD接口、行列式鍵盤接口和蜂鳴器接口,對工業(yè)以太網(wǎng)上的其他EPA設(shè)備進(jìn)行監(jiān)控和顯示,有較好的人機(jī)交互的功能。

在該設(shè)計(jì)中,網(wǎng)絡(luò)通信分為有線和無線兩種通信方式。其中,有線網(wǎng)絡(luò)通信使用的是10M/100M的LAN91C111的自適應(yīng)網(wǎng)卡芯片,并通過RJ45網(wǎng)口接入EPA網(wǎng)絡(luò)。LAN91C111是SMSC公司為嵌入式應(yīng)用系統(tǒng)推出的第三代快速以太網(wǎng)控制器。LAN91C111的芯片上集成了遵循SMSC/CD協(xié)議的MAC(媒體層)和PHY(物理層),符合IEEE802.3/802.U-100Base-Tx/10Base-T規(guī)范。在本控制器上預(yù)留了藍(lán)牙模塊和ZigBee模塊的無線通信接口,作為輔助處理模塊。可根據(jù)工業(yè)現(xiàn)場的實(shí)際情況,接入無線通信模塊,實(shí)現(xiàn)與EPA網(wǎng)絡(luò)的無線通信,通過該模塊能夠監(jiān)測無線現(xiàn)場設(shè)備的運(yùn)行情況及相關(guān)參數(shù)。

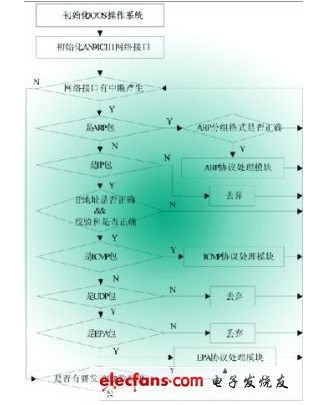

在整個(gè)EPA通信協(xié)議棧網(wǎng)絡(luò)層和傳輸層接收報(bào)文處理流程中。NIOSⅡ處理器復(fù)位后初始化UC/OS Ⅱ操作系統(tǒng)、網(wǎng)絡(luò)接口、堆棧以及定時(shí)器等外圍設(shè)備接口。從外部存儲(chǔ)器FLASH中獲取IP地址和MAC地址等網(wǎng)絡(luò)信息。當(dāng)收到的報(bào)文IP地址和MAC地址都是本機(jī)地址時(shí),把報(bào)文以LWIP所要求的特殊結(jié)構(gòu)體形式存儲(chǔ)在接收緩沖區(qū)中,然后發(fā)送到EPA協(xié)議棧中進(jìn)行處理,當(dāng)檢查到UDP端口號(hào)是0x88BC時(shí),將報(bào)文交由EPA應(yīng)用層處理模塊進(jìn)行處理。

其部分報(bào)文處理程序如下:

/*報(bào)文發(fā)送*/

void SendTask(void *pdata){

struct netconn *conn;

struct ip_addr remote_addr,local_addr;

struct netbuf * buf;

struct udp_pcb * udpbuf;

struct pbuf * buf;

char text[] = “A static test”;

/*設(shè)置遠(yuǎn)程主機(jī)的IP地址*/

remote_addr.addr = htonl(0x8080023D);

/*設(shè)置本地主機(jī)的IP地址*/

local_addr.addr = htonl(0x80800233);

for(;;){

/*建立一個(gè)新連接*/

conn = netconn_new(NETCONN_UDP);

/*綁定本地IP地址和端口號(hào)*/

netconn_bind(conn,&local_addr,0x88BC);

/*連接遠(yuǎn)程主機(jī)*/

netconn_connect(conn,&remote_addr,0x88BC);

buf = netbuf_new();

/*建立任意的數(shù)據(jù)*/

netbuf_ref(buf,text,sizeof(text));

netconn_send(conn,buf);

netconn_delete(conn);

netbuf_delete(buf);

OSTimeDlyHMSM(0,0,1,0);

buf = pbuf_alloc(PBUF_RAW, 60,

PBUF_RAM);

memcpy(buf-》payload,text,

sizeof(text));

udpbuf = udp_new();

udpbuf-》local_port = 0x88bc;

udpbuf-》remote_port = 0x88bc;

udpbuf-》local_ip = local_addr;

udpbuf-》remote_ip = remote_addr;

udp_bind(udpbuf, &udpbuf-》local_ip,

udpbuf-》local_port);

udp_sendto(udpbuf,buf,&remote_addr,udpbuf-》remote_port);

udp_remove(udpbuf); //釋放

udp_pcb內(nèi)存

pbuf_free(buf);

OSTimeDlyHMSM(0,0,1,0);

/* Main initializes lwIP, creates a single task and starts task scheduler. */

void ReceiveTask(void * pdata){//該任務(wù)

和IP協(xié)議棧相關(guān),該任務(wù)由

_sys_thread_new函數(shù)來創(chuàng)建

struct netbuf * buf1,*buf2,*buf1_temp;

struct netconn * conn1,*conn2;

void * payload;

u16_t len;

struct ip_addr remote_addr,local_addr;

char text[] = “I get a EPA packet,please

give me another,I need you, baby.”;

remote_addr.addr = htonl

(0x8080023D);

local_addr.addr = htonl(0x80800233);

conn1 = netconn_new(NETCONN_

UDP);

conn2 = netconn_new(NETCONN_

UDP);

netconn_bind(conn2, &local_addr, 0x88bc);

netconn_connect(conn2,&remote_addr,

0x88BC);

netconn_bind(conn1, &local_addr, 0x88bc);

while((buf1_temp = netconn_recv

(conn1))!=NULL){

//關(guān)于netbuf的結(jié)構(gòu)可以參看api.h文件,在該結(jié)構(gòu)體中,成員p是指向pbuf的一個(gè)指針

buf1 = netbuf_new();

buf1 = buf1_temp;

payload = buf1-》p-》payload;

len = buf1-》p-》len;

netbuf_delete(buf1);

buf2 = netbuf_new();

netbuf_ref(buf2,text,sizeof(text));

netconn_send(conn2,buf2);

netbuf_delete(buf2);

圖4 EPA協(xié)議棧接收報(bào)文處理流程圖

結(jié)語

在完成整個(gè)設(shè)計(jì),控制器接入EPA網(wǎng)絡(luò)中能夠正常運(yùn)行。由于控制器中的處理器使用的是FPGA芯片,有較強(qiáng)的靈活性,能夠進(jìn)行編程、除錯(cuò)、再編程和重復(fù)操作,因而可以充分地進(jìn)行設(shè)計(jì)開發(fā)和驗(yàn)證。當(dāng)電路有少量改動(dòng)時(shí)候,更凸現(xiàn)出其優(yōu)勢,其現(xiàn)場編程能力可以延長產(chǎn)品在市場上的壽命,可以用來系統(tǒng)升級(jí),從而大大提高了控制器的性能。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論