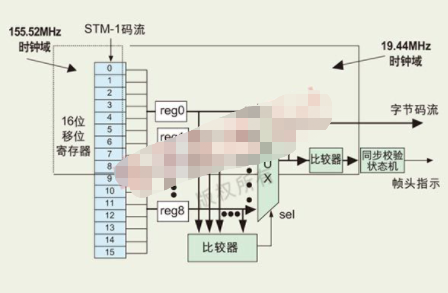

本文介紹了集中式插入法幀同步系統(tǒng)的原理,分析了幀同步系統(tǒng)的工作流程。采用模塊化的設(shè)計思想,利用VHDL設(shè)計了同步參數(shù)可靈活配置的幀同步系統(tǒng),闡述了關(guān)鍵部件的設(shè)計方法,提出了一種基于FPGA的幀同步系統(tǒng)設(shè)計方案。

2013-11-11 13:36:01 4359

4359

基于VHDL語言的數(shù)字鐘系統(tǒng)設(shè)計 基于FPGA的交通燈控制 采用可編程器件(FPGA/CPLD)設(shè)計數(shù)字鐘 數(shù)字鎖相環(huán)法位同步信號 基于FPGA的碼速調(diào)整電路的建模與設(shè)計 誤碼檢測儀

2012-02-10 10:40:31

FPGA設(shè)計中幀同步系統(tǒng)的實(shí)現(xiàn)數(shù)字通信時,一般以一定數(shù)目的碼元組成一個個“字”或“句”,即組成一個個“幀”進(jìn)行傳輸,因此幀同步信號的頻率很容易由位同步信號經(jīng)分頻得出,但每個幀的開頭和末尾時刻卻無法由

2012-08-11 16:22:49

FPGA設(shè)計中幀同步系統(tǒng)的實(shí)現(xiàn)數(shù)字通信時,一般以一定數(shù)目的碼元組成一個個“字”或“句”,即組成一個個“幀”進(jìn)行傳輸,因此幀同步信號的頻率很容易由位同步信號經(jīng)分頻得出,但每個幀的開頭和末尾時刻卻無法由

2012-08-11 17:44:43

的音頻格式也被DVD-A所采用,它支持立體聲和5.1環(huán)繞聲,1999年由DVD討論會發(fā)布和推出的。我們知道在現(xiàn)實(shí)生活中,人耳聽到的聲音是模擬信號,PCM就是要把聲音從模擬轉(zhuǎn)換成數(shù)字信號的一種技術(shù),他

2019-07-05 08:37:52

PCM的長幀同步和短幀同步有什么區(qū)別

2023-10-09 08:20:47

了最新的大規(guī)模數(shù)字集成電路和厚薄膜工藝技術(shù)而推出的新一代高集成度單板PCM基群復(fù)接設(shè)備,它可以在標(biāo)準(zhǔn)的PCM30基群即 2M傳輸通道上直接提供30路終端業(yè)務(wù)接口。用戶接口類型多樣(包括語音、數(shù)據(jù)、圖象

2012-04-20 15:56:34

畢設(shè)需要用labview軟件進(jìn)行數(shù)字復(fù)接分接實(shí)驗(yàn)的仿真,但是從來沒有接觸過那個軟件。哪位能教教么?我最近也在看視頻學(xué)習(xí),但是還是不懂要怎么去用二進(jìn)制數(shù)去輸出相應(yīng)的方波序列,或者說這個題目不知道怎么下手?哪位能提點(diǎn)一下嗎

2015-03-26 22:00:04

數(shù)字復(fù)接芯片有哪幾種?有何不同?復(fù)接芯片有哪些應(yīng)用舉例?

2021-05-27 06:08:21

嗨,我有一個項目,我必須在發(fā)送器端序列化16位數(shù)字輸入數(shù)據(jù),然后在接收器端反序列化數(shù)據(jù)。這種數(shù)字鏈路的預(yù)期速度是100MHz-500MHz。這種實(shí)現(xiàn)必須是系統(tǒng)同步的,即沒有任何時鐘轉(zhuǎn)發(fā),我必須在Rx

2019-08-06 10:31:49

,該板卡上擁有兩塊K7 325T FPGA和三個FMC插槽可供用戶使用。本方案使用兩塊FMC205和兩塊USDR_U3構(gòu)成了一個4通道的同步信號采集系統(tǒng)。每個FMC205插在一個U3板卡FMC插槽上

2018-10-16 09:51:54

使用Xilinx V5系列的FPGA開發(fā)AD9783芯片,將兩路相同的信號數(shù)據(jù),送給DAC,具體利用DCO反饋時鐘,通過源語產(chǎn)生差分時鐘產(chǎn)生DCI,后利用DCO 1,0狀態(tài)分別送兩路數(shù)據(jù);同時配置8

2023-12-19 06:03:59

數(shù)字電路中,時鐘是整個電路最重要、最特殊的信號: ⑴ 系統(tǒng)內(nèi)大部分器件的動作都是在時鐘的跳變沿上進(jìn)行, 這就要求時鐘信號時延差要非常小,否則就可能造成時序邏輯狀態(tài)出錯; ⑵ 時鐘信號通常是

2012-03-05 14:29:00

【背景】針對當(dāng)前生理電信號采集設(shè)備多為異步數(shù)據(jù)采集設(shè)備,高速模擬復(fù)用開關(guān)無法實(shí)現(xiàn)理想開、關(guān)狀態(tài),各信號通道串?dāng)_較大,開關(guān)的開啟、關(guān)閉無法實(shí)現(xiàn)時域同步;依據(jù)數(shù)字信號處理理論:時域信號時移導(dǎo)致頻域信號

2012-06-14 00:11:59

請教論壇大神,三路16位AD同步采集,用SPI把數(shù)據(jù)串行傳送給FPGA,然后在FPGA內(nèi)部 同步鎖存再送給FIFO緩存,然后并行送出。請問,同步鎖存怎么實(shí)現(xiàn),然后需要設(shè)計怎樣的FIFO,謝謝解惑!

2014-12-04 10:27:15

現(xiàn)在面臨的問題是,兩路信號,一路來源于驅(qū)動器的位置信號,一路來源與ni數(shù)據(jù)采集卡,想通過這兩路信號繪制一條曲線,要求時間上非常同步,位置信息和采集信息一一對應(yīng),請問通過什么辦法可以解決此類問題?、??{:4_106:}

2013-04-15 16:14:23

DSP技術(shù)廣泛應(yīng)用于各個領(lǐng)域,但傳統(tǒng)的數(shù)字信號處理器由于以順序方式工作使得數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應(yīng)用目標(biāo)的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實(shí)現(xiàn)數(shù)字信號處理系統(tǒng),具有很強(qiáng)的實(shí)時性和靈活性,因此利用FPGA實(shí)現(xiàn)數(shù)字信號處理成為數(shù)字信號處理領(lǐng)域的一種新的趨勢。

2019-10-17 08:12:27

://www.bilibili.com/video/BV1xC4y1H7QM?p=10本系列將帶來FPGA的系統(tǒng)性學(xué)習(xí),從最基本的數(shù)字電路基礎(chǔ)開始,最詳細(xì)操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息

2023-02-28 16:38:14

采集系統(tǒng),A/D建立穩(wěn)定的工作狀態(tài)需要相當(dāng)長時間,頻繁地改變A/D的工作狀態(tài)會影響測量的精度,嚴(yán)重時會造成信號的失真。為此,同步命令不直接作用于高速A/D,而是用FPGA產(chǎn)生A/D采樣時鐘信號,并根據(jù)

2021-07-05 11:23:33

使用。 本文基于快速傅里葉IP核可復(fù)用和重配置的特點(diǎn),實(shí)現(xiàn)一種頻域的FPGA數(shù)字脈壓處理器,能夠完成正交輸入的可變點(diǎn)LFM信號脈沖壓縮,具有設(shè)計靈活,調(diào)試方便,可擴(kuò)展性強(qiáng)的特點(diǎn)。 1 系統(tǒng)功能硬件

2018-11-09 15:53:22

基于FPGA的雙路低頻信號發(fā)生器設(shè)計摘要 本設(shè)計是基于Altera公司的Cyclone II系列EP2C8Q208C8N芯片的雙路低頻信號發(fā)生器。系統(tǒng)應(yīng)用FPGA內(nèi)部特有的可配置IP核和鎖相環(huán)等

2018-08-23 15:32:05

數(shù)字復(fù)分接技術(shù)是數(shù)字通信網(wǎng)中的一項重要技術(shù),能將若干路低速信號合并為一路高速信號,以提高帶寬利用率和數(shù)據(jù)傳輸效率。

2019-09-26 07:48:06

基于FPGA設(shè)計了一高速數(shù)字下變頻系統(tǒng),在設(shè)計中利用并行NCO和多相濾波相結(jié)合的方法有效的降低了數(shù)據(jù)的速率,以適合數(shù)字信號處理器件的工作頻率。

2019-09-26 07:06:35

基于fpga的數(shù)字通信系統(tǒng)數(shù)字復(fù)接器建模與設(shè)計

2014-04-15 21:58:57

中仿真數(shù)字復(fù)接實(shí)驗(yàn),從而提高用戶的學(xué)習(xí)效果,也可單獨(dú)用LabView軟件來開設(shè)實(shí)驗(yàn),這樣就不受臺套數(shù)的限制。課題主要工作流程:1、了解LabView實(shí)驗(yàn)室虛擬儀器工作平臺,并熟練掌握其編程及數(shù)據(jù)采集

2016-05-14 15:51:33

。 1、MT9075芯片簡介[1] MT9075是 Mitel 公司推出的一個可以產(chǎn)生并處理PCM30信號的器件,不僅合并了PCM30成幀器、線性接口部件(UU)和鏈路控制器,還具有時鐘同步、中斷控制

2019-06-24 05:00:50

通過濾波放大電路濾去高頻干擾和低頻漂移信號,同時也進(jìn)行線性放大,使之變?yōu)橐徊ㄐ握?guī)幅值適當(dāng)?shù)恼?b class="flag-6" style="color: red">信號,然后經(jīng)過A/D轉(zhuǎn)換變成數(shù)字信號進(jìn)入:PIC單片機(jī)處理。 系統(tǒng)采用一種改進(jìn)的雙T型選頻網(wǎng)絡(luò),在提高Q

2018-10-17 11:39:28

我想做多個FPGA的時鐘同步,目前的想法是用一個FPGA的內(nèi)部時鐘,復(fù)制到外接IO口,接到另一個FPGA的外部時鐘引腳,波形有較小的相移但是可以保證同步。想問一下可以復(fù)制多次,驅(qū)動多個FPGA的同步嗎。對驅(qū)動能力有什么要求?其中每一個FPGA都用的是一個EP4CE的最小系統(tǒng)板。

2019-01-21 15:07:41

本文基于FPGA的技術(shù)特點(diǎn),結(jié)合數(shù)字復(fù)接技術(shù)的基本原理,實(shí)現(xiàn)了基群速率(2048kbps)數(shù)字信號的數(shù)字分接與復(fù)接。

2021-04-30 06:27:39

1 概述1.1簡介本文介紹了如何使用dsPIC30F 數(shù)字信號控制器(Digital Signal Controller,DSC)控制正弦電流來驅(qū)動具有位置傳感器的永磁同步

2021-08-27 07:29:05

PCM編碼原理與規(guī)則是什么?如何利用FPGA編程技術(shù)實(shí)現(xiàn)PCM編碼原理?機(jī)場監(jiān)視監(jiān)控網(wǎng)絡(luò)中低速接入應(yīng)用

2021-04-15 06:38:46

在數(shù)字通信系統(tǒng)中,同步技術(shù)是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監(jiān)測輸入碼元信號,確保收發(fā)同步,而且在獲取幀同步及對接收的數(shù)字碼元進(jìn)行各種處理的過程中也為系統(tǒng)提供了一個基準(zhǔn)

2019-08-05 06:43:01

采用PCM編碼原理及FPGA編程技術(shù)實(shí)現(xiàn)PCM數(shù)字基群接口傳輸?shù)退贁?shù)據(jù)的接入

2021-04-30 07:09:04

在設(shè)計AO輸出時,采用pcm1792a芯片,采用的是pcm模式,當(dāng)fs>102.4KHz(此時過采樣率配置為32),R和L的兩路輸出不能同步,根據(jù)datasheet,將其配置為立體聲模式

2019-08-12 07:40:09

數(shù)據(jù)復(fù)接方法有哪些?如何去實(shí)現(xiàn)它們?在設(shè)計數(shù)據(jù)復(fù)接與分接設(shè)備過程中有哪些難點(diǎn)?怎樣利用FPGA去實(shí)現(xiàn)多路話音/數(shù)據(jù)復(fù)接設(shè)備?

2021-04-14 06:42:57

數(shù)字復(fù)接的基本原理是什么?數(shù)字復(fù)接系統(tǒng)是如何構(gòu)成的?怎樣去設(shè)計數(shù)字復(fù)接系統(tǒng)?

2021-04-28 07:04:28

請教各位大大:我最近做FPGA采集100MHz的信號,另一路同步觸發(fā)。但觸發(fā)信號上升沿在40ns左右,最后導(dǎo)致信號波形左右晃動。請問在FPGA中如何處理可以準(zhǔn)確采集到觸發(fā)信號,排除左右晃動的情況?

2013-03-06 00:22:42

各位大神我想請教下兩正弦信號同步的問題,一路信號為fpga內(nèi)部產(chǎn)生的dds信號,另一路信號由外部輸入給fpga,已知兩信號頻率相同,如何保證它們實(shí)時相位同步啊?跪求解決方案~

2016-01-15 17:52:13

實(shí)驗(yàn)二 脈沖編碼調(diào)制(PCM)實(shí)驗(yàn)一、實(shí)驗(yàn)?zāi)康?、了解語音信號編譯碼的工作原理;2、驗(yàn)證PCM編碼原理; 3、初步了解PCM專用大規(guī)模集成電路的工作原理 和應(yīng)用;4、了解語音信號數(shù)字化技術(shù)的主要指

2009-10-11 08:57:57

MCLK, BCLK,LRCLK三個時鐘信號?網(wǎng)上有比較多的方案是選用 CPLD(或者FPGA) + 雙晶振,來達(dá)到分頻和同步的目的? 請問這樣是否靠譜?CPLD(或者FPGA)是否要同步輸出 MCLK, BCLK,LRCLK三個時鐘信號給主控和PCM1794A?非常感謝!Ricky

2019-08-16 10:47:25

使用Xilinx V5系列的FPGA開發(fā)AD9783芯片,將兩路相同的信號數(shù)據(jù),送給DAC,具體利用DCO反饋時鐘,通過源語產(chǎn)生差分時鐘產(chǎn)生DCI,后利用DCO 1,0狀態(tài)分別送兩路數(shù)據(jù);同時配置8

2019-02-28 14:49:44

二次群復(fù)接的基本原理是什么?基于CPLD的PDH通信二次群復(fù)接器的設(shè)計怎樣對PDH通信二次群復(fù)接器進(jìn)行仿真?

2021-04-30 07:01:48

要求是利用FPGA開發(fā)板,設(shè)計一個多路PCM編碼的復(fù)接器,已知8路電話信號已經(jīng)過PCM編碼,每路位寬8bit,頻率8KHz,以64比特寬度并行輸入到復(fù)接器,要求復(fù)接邏輯能夠把8電話路信號順序排隊,以

2014-09-16 21:39:41

本帖最后由 luna 于 2011-3-3 14:44 編輯

PCM編解碼系統(tǒng)中的編碼器,傳輸變換兩路音頻信號為一路帶有冗余信息的PCM信號。冗余信息包含糾正記錄或重放期間產(chǎn)生的隨機(jī)誤差所增加

2011-03-03 00:08:17

一:概述30路電話+4路百兆網(wǎng)絡(luò)PCM電話光端機(jī)是漢源高科(北京)科技有限公司采用自主知識產(chǎn)權(quán)的大規(guī)模集成電路,應(yīng)用時分復(fù)用技術(shù),將以太網(wǎng)信號和電話信號混合編碼后在一對光纖上傳輸。實(shí)現(xiàn)10/100M

2022-06-13 22:23:31

本文介紹了可編程邏輯器件(PLD)在雙音多頻信號的PCM 編碼中的應(yīng)用。從雙音多頻信號的PCM 編碼到PCM 編碼信號的輸出,利用CPLD、硬件描述語言VHDL 及MATLAB 來實(shí)現(xiàn)整個功能,仿真

2009-08-14 11:40:18 44

44 該文闡述了現(xiàn)場可編程邏輯器件FPGA的主要特點(diǎn),應(yīng)用FPGA芯片和VHDL硬件描述語言設(shè)計的模擬示波器數(shù)字信號顯示系統(tǒng)的設(shè)計原理和設(shè)計方法。現(xiàn)場可編程邏輯門陣列(Field Programmab

2009-08-17 10:36:11 19

19 本文針對磁通門信號采集與處理的具體特點(diǎn),對基于FPGA的磁通門數(shù)字信號處理系統(tǒng)進(jìn)行了研究。該系統(tǒng)采用A/D轉(zhuǎn)換器對磁通門輸出信號進(jìn)行采樣,采樣后的數(shù)據(jù)通過FPGA進(jìn)行數(shù)據(jù)

2009-12-23 15:09:09 15

15 根據(jù)直接數(shù)字合成器的基本原理,給出了基于FPGA 的直接數(shù)字合成器的設(shè)計與實(shí)現(xiàn),利用FPGA有效地擴(kuò)展了輸出波形的頻率范圍,實(shí)現(xiàn)了數(shù)字移相信號發(fā)生器。該信號發(fā)器主要采用了

2009-12-26 16:34:58 36

36 本文針對磁通門信號采集與處理的具體特點(diǎn),對基于FPGA的磁通門數(shù)字信號處理系統(tǒng)進(jìn)行了研究。該系統(tǒng)采用A/D轉(zhuǎn)換器對磁通門輸出信號進(jìn)行采樣,采樣后的數(shù)據(jù)通過FPGA進(jìn)行數(shù)據(jù)處理,再

2010-07-21 17:24:58 26

26 根據(jù)直接數(shù)字合成器的基本原理,給出了基于FPGA的直接數(shù)字合成器的設(shè)計與實(shí)現(xiàn),利用FPGA有效地擴(kuò)展了輸出波形的頻率范圍,實(shí)現(xiàn)了數(shù)字移相信號發(fā)生器。該信號發(fā)生器主要采用了直接

2010-07-21 17:30:47 69

69 從時分復(fù)接系統(tǒng)對位同步系統(tǒng)的性能要求出發(fā),提出了一種基于FPGA的快速位同步系統(tǒng)的設(shè)計方案,給出了位同步系統(tǒng)的實(shí)驗(yàn)仿真,結(jié)果表明該系統(tǒng)有較快的位同步建立時間,節(jié)省了F

2010-07-28 18:13:40 20

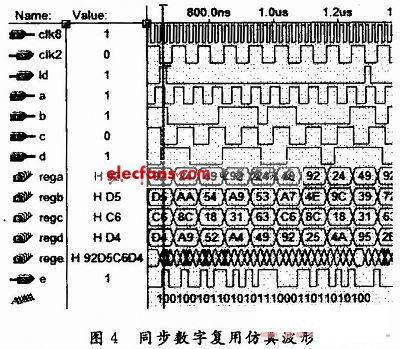

20 從時分復(fù)接系統(tǒng)對幀同步系統(tǒng)的性能要求出發(fā),提出了一種采用FPGA實(shí)現(xiàn)幀同步系統(tǒng)的設(shè)計方案,重點(diǎn)介紹了同步保護(hù)電路的設(shè)計,并給出了FPGA設(shè)計的實(shí)驗(yàn)仿真,實(shí)驗(yàn)結(jié)果表明該電路

2010-08-06 16:46:59 24

24 主題內(nèi)容與適用范圍

本標(biāo)準(zhǔn)規(guī)定了PCM編解碼系統(tǒng)信號的格式和其他有關(guān)條件。

本標(biāo)準(zhǔn)適用于錄像系統(tǒng)錄放音頻信號用的PCM編解碼器。

系統(tǒng)說明

PCM編解碼

2010-08-31 18:26:25 35

35 為實(shí)現(xiàn)設(shè)備中存在的低速數(shù)據(jù)光纖通信的同步復(fù)接/ 分接,提出一種基于FPGA 的幀同步頭信號提取檢測方案,其中幀頭由7 位巴克碼1110010 組成,在數(shù)據(jù)的接收端首先從復(fù)接數(shù)據(jù)中

2010-10-26 16:56:54 46

46 采用PCM編碼原理及FPGA編程技術(shù)實(shí)現(xiàn)PCM數(shù)字基群接口傳輸?shù)退贁?shù)據(jù)的接入

一、概述

----高速傳輸系統(tǒng)中低速設(shè)備

2009-02-08 11:19:36 1691

1691

什么是PCM

PCM是用于將一個模擬信號(如話音)嫁接到一個64kbps的數(shù)字位流上,以便于傳輸。PCM將連續(xù)的模擬信號變換成離散的數(shù)字信號,在數(shù)字音響中普遍采用的是脈沖編

2009-04-10 12:55:25 25205

25205 基于FPGA的提取位同步時鐘DPLL設(shè)計

在數(shù)字通信系統(tǒng)中,同步技術(shù)是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監(jiān)測輸入碼元信號,確保收發(fā)

2010-01-25 09:36:18 2890

2890

本內(nèi)容為華為電信基礎(chǔ)知識題庫,列出了電信的基礎(chǔ)知識題 1、語音信號數(shù)字化過程中,采用的是的量化方法是非均勻量化。 2、PCM30/32路系統(tǒng)中,每個碼的時間間隔是488ns 。 3、PCM30/32路系統(tǒng)中,TS0用于傳送幀同步信號,TS16用于傳送話路信令。 4、PCM30/32路

2011-02-18 17:42:19 211

211 本文利用Max+ Plus 軟件對PCM30/ 32 路系統(tǒng)的發(fā)送端時序與幀結(jié)構(gòu)進(jìn)行了仿真,由仿真結(jié)果可以清楚地發(fā)現(xiàn)該系統(tǒng)發(fā)端時序的規(guī)律

2011-03-28 10:55:27 2508

2508

淺談數(shù)字中繼PCM故障的原因與清除方法。某一PCM系統(tǒng)與對端的相應(yīng)系統(tǒng)的連接中由于單板配置、數(shù)據(jù)配置、虛焊、光路中斷或其它原因而導(dǎo)致的傳輸故障即引起該告警。

2011-09-15 10:33:40 2829

2829 本文提出基于FPGA的數(shù)字收發(fā)機(jī)信號處理研究與實(shí)現(xiàn)

2011-11-01 18:20:42 50

50 本書共分8章,主要內(nèi)容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設(shè)計中常用軟件簡介、用fpga實(shí)現(xiàn)數(shù)字信號處理的數(shù)據(jù)規(guī)劃、多種結(jié)構(gòu)類型的fir數(shù)字濾波器的fpga實(shí)現(xiàn)、不同結(jié)構(gòu)

2011-11-04 15:50:12 0

0 為了對中頻PCM信號進(jìn)行直接解調(diào),提出一種全新的數(shù)字化PCM中頻解調(diào)器的設(shè)計方法。在實(shí)現(xiàn)過程中,采用大規(guī)模的FPGA芯片對位幀同步器進(jìn)行了融合,便于設(shè)備的集成化和小型化。這種新

2012-03-05 17:51:52 58

58 本文以時間同步儀的功能為出發(fā)點(diǎn),設(shè)計了基于ARM和FPGA的控制系統(tǒng),該系統(tǒng)以ARM芯片S3C2440A為控制核心,在FPGA芯片XCS30的輔助控制下,完成了時間同步儀的人機(jī)交互、參數(shù)設(shè)定、電文處

2012-05-25 14:33:54 41

41 基于FPGA數(shù)字信號處理,本文主要探討了基于FPGA數(shù)字信號處理的實(shí)現(xiàn)

2015-10-30 10:39:38 30

30 針對航空測試中常用的同步器信號,提出一種基于嵌入式系統(tǒng)的雙通道同步器信號采集系統(tǒng)。系統(tǒng)以同步器專用芯片對信號進(jìn)行預(yù)處理,解析出數(shù)字量的角度和角速率,以FPGA為控制器進(jìn)行數(shù)據(jù)處理,實(shí)現(xiàn)兩路角度和角速率測量功能。經(jīng)過仿真實(shí)驗(yàn)和系統(tǒng)調(diào)試,結(jié)果表明此系統(tǒng)能夠穩(wěn)定高效的采集和處理同步器信號。

2015-12-04 15:03:44 0

0 本書比較全面地闡述了fpga在數(shù)字信號處理中的應(yīng)用問題。本書共分8章,主要內(nèi)容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設(shè)計中常用軟件簡介、用fpga實(shí)現(xiàn)數(shù)字信號處理的數(shù)據(jù)規(guī)劃、多種

2015-12-23 11:07:46 44

44 多路同步數(shù)字調(diào)相信號源一般采用單片機(jī)和多片專用DDS芯片配合實(shí)現(xiàn)。該技術(shù)同步實(shí)現(xiàn)復(fù)雜,成本高。給出了一種基于FPGA的多路同步信號源的設(shè)計方法,通過VHDL語言硬件編程實(shí)現(xiàn)了基于單片FPGA

2016-05-27 13:47:49 7436

7436

基于FPGA數(shù)字信號處理

2016-12-14 22:08:25 20

20 數(shù)字信號處理的FPGA實(shí)現(xiàn)

2016-12-14 22:08:25 32

32 DSP技術(shù)廣泛應(yīng)用于各個領(lǐng)域,但傳統(tǒng)的數(shù)字信號處理器由于以順序方式工作使得數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應(yīng)用目標(biāo)的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實(shí)現(xiàn)數(shù)字信號處理系統(tǒng),具有很強(qiáng)

2017-10-31 10:37:23 0

0 一、PCM接入設(shè)備概述 PCM的含義 PCM:Pulse Code Modulation的縮寫,即:脈沖編碼調(diào)制。脈沖編碼調(diào)制的作用:將模擬信號經(jīng)抽樣、量化、編碼轉(zhuǎn)成標(biāo)準(zhǔn)的數(shù)字信號。 PCM設(shè)備

2017-11-16 16:26:05 44

44 本文設(shè)計并在FPGA芯片中實(shí)現(xiàn)了數(shù)字音頻廣播系統(tǒng)的信號調(diào)制系統(tǒng)。信號調(diào)制系統(tǒng)位于整個數(shù)字音頻廣播系統(tǒng)基帶信號處理鏈的末端,是基帶數(shù)字信號處理的核心系統(tǒng)。根據(jù)Eureka147標(biāo)準(zhǔn),信號調(diào)制系統(tǒng)需要

2017-11-22 15:25:01 3892

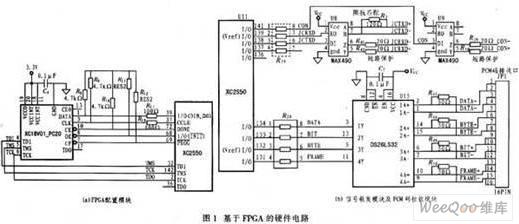

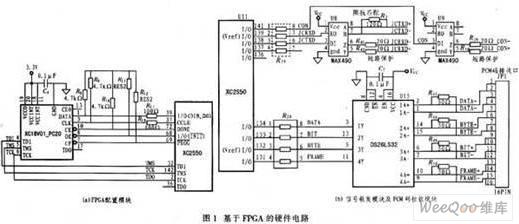

3892 圖1給出基于FPGA的硬件電路。其中,圖1(a)為FPGA配置模塊;圖1(b)為信號收發(fā)模塊及PCM碼接收模塊。

2018-12-30 09:28:00 2897

2897

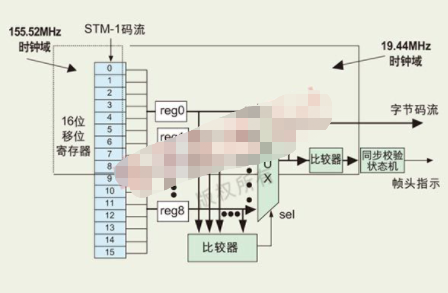

同步技術(shù)在數(shù)字通信系統(tǒng)中是非常重要的技術(shù),一般有位(碼元)同步、字(碼組)同步、載波同步和幀同步,對于網(wǎng)絡(luò)系統(tǒng)來說還有網(wǎng)同步。現(xiàn)代SDH數(shù)字傳輸網(wǎng)是全網(wǎng)同步的數(shù)字傳送網(wǎng)絡(luò),對于接收端的數(shù)據(jù)處理

2021-06-23 15:44:00 2451

2451

數(shù)字信號處理的FPGA實(shí)現(xiàn).第3版英文

2021-10-18 10:55:32 0

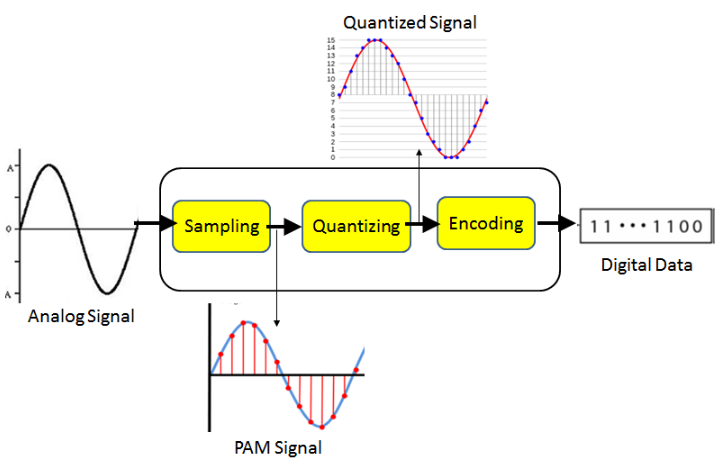

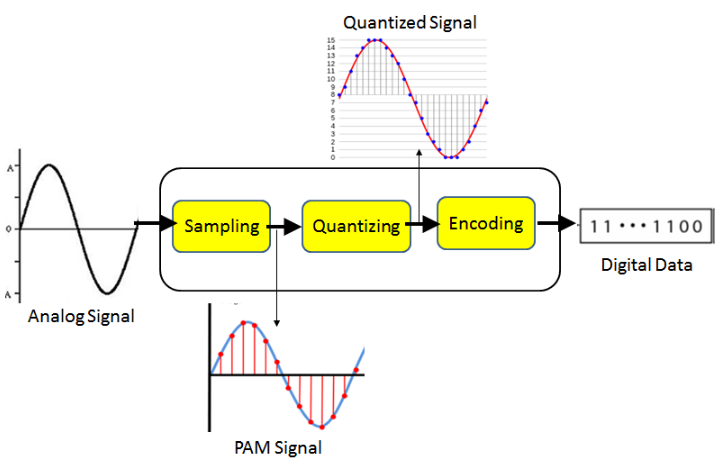

0 大多數(shù)當(dāng)前的數(shù)字音頻系統(tǒng)(計算機(jī)、光盤、數(shù)字電話等)使用多比特脈沖編碼調(diào)制 (PCM) 來表示聲音信號。PCM 的優(yōu)點(diǎn)是易于操作。這允許對音頻流執(zhí)行信號處理操作,例如混合、濾波和均衡。如圖1所示,模擬到PCM轉(zhuǎn)換包括三個步驟:采樣、量化和編碼。

2023-05-29 09:40:45 1059

1059

時鐘信號的同步 在數(shù)字電路里怎樣讓兩個不同步的時鐘信號同步? 在數(shù)字電路中,時鐘信號的同步是非常重要的問題。因?yàn)樵?b class="flag-6" style="color: red">信號處理過程中,如果不同步,就會出現(xiàn)信號的混淆和錯誤。因此,在數(shù)字電路中需要采取一些

2023-10-18 15:23:48 771

771

電子發(fā)燒友App

電子發(fā)燒友App

評論