FPGA CPLFPGA CPLD 數(shù)字電路設(shè)計經(jīng)驗分享FPGA/CPLD數(shù)字電路設(shè)計經(jīng)驗分享摘要:在數(shù)字電路的設(shè)計中,時序設(shè)計是一個系統(tǒng)性能的主要標志,在高層次設(shè)計方法中,對時序控制的抽象度也相應(yīng)

2012-08-11 10:17:18

本帖最后由 xianer317 于 2014-6-21 19:34 編輯

FPGA/CPLD數(shù)字電路設(shè)計經(jīng)驗分享

2014-06-21 19:33:20

FPGACPLD數(shù)字電路設(shè)計經(jīng)驗分享

2012-08-07 21:46:49

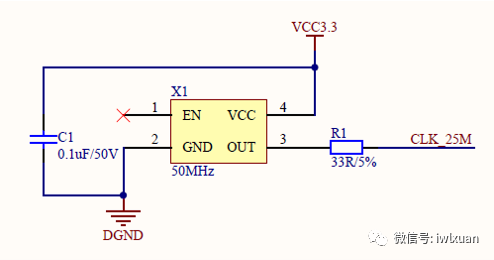

`FPGA核心板電路設(shè)計架構(gòu)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 核心板除了一顆昂貴

2015-04-20 11:25:47

FPGA電源電路設(shè)計本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 整個系統(tǒng)需要三檔不同的電源電壓,即

2015-04-22 12:06:21

SDRAM電路設(shè)計本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 如圖3.39所示,SDRAM的電路很簡單

2015-05-04 11:45:05

字庫芯片電路設(shè)計本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 最后,我們再來看看字庫芯片U1,該芯片

2015-06-09 10:48:54

`FPGA板級電路設(shè)計五要素本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 和純粹基于PC機的各種軟件編程

2015-04-01 11:04:11

FPGA布線開關(guān)的電路設(shè)計1 研究方法及其條件假定2 導(dǎo)通晶體管布線開關(guān)設(shè)計 2.1導(dǎo)通晶體管布線開關(guān)尺寸優(yōu)化2.2 導(dǎo)通晶體管存在的問題及其改進3 三態(tài)緩沖布線開關(guān)的設(shè)計3.1三態(tài)緩沖器尺寸優(yōu)化3.2 三態(tài)緩沖布線開關(guān)的缺點及其改進4 各種布線開關(guān)性能比較及其建議

2011-03-02 09:50:16

FPGA應(yīng)用可分為三個層面:電路設(shè)計、產(chǎn)品設(shè)計、系統(tǒng)設(shè)計1.系統(tǒng)級應(yīng)用 系統(tǒng)級的應(yīng)用是FPGA與傳統(tǒng)的計算機技術(shù)結(jié)合,實現(xiàn)一種FPGA版的計算機系統(tǒng)如用XilinxV-4, V-5系列的FPGA

2012-03-16 09:43:55

FPGA電源電路設(shè)計本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》整個系統(tǒng)需要三檔不同的電源電壓,即3.3V、2.5V和1.2V。如圖3.13所示,我們使用了三顆LDO分別產(chǎn)生。T1

2019-01-10 09:34:18

FPGA控制的PS2接口電路設(shè)計

2021-03-07 11:47:27

是行之有效的,通過許多設(shè)計實例證明采用這種方式可以使電路的后仿真通過率大大提高,并且系統(tǒng)的工作頻率可以達到一個較高水平。FPGA數(shù)字電路設(shè)計經(jīng)驗分享[hide][/hide]

2012-03-05 16:33:30

下載配置與調(diào)試接口電路設(shè)計FPGA是SRAM型結(jié)構(gòu),本身并不能固化程序。因此FPGA需要一片F(xiàn)lash結(jié)構(gòu)的配置芯片來存儲邏輯配置信息,用于進行上電配置。以Altera公司的FPGA為例,配置芯片

2019-06-11 05:00:07

FPGA板級電路設(shè)計五要素本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 和純粹基于PC機的各種軟件編程

2019-01-25 06:27:02

FPGA的IRIG-B(DC)碼產(chǎn)生電路設(shè)計FPGA的IRIG-B(DC)碼產(chǎn)生電路設(shè)計.doc

2012-08-11 10:34:15

電路設(shè)計[FPGA]設(shè)計經(jīng)驗

2012-05-23 19:49:45

電路設(shè)計[FPGA]設(shè)計經(jīng)驗

2012-08-20 15:37:36

電路設(shè)計[FPGA]設(shè)計經(jīng)驗

2019-01-03 14:19:28

異步SRAM存儲器接口電路設(shè)計(Altera FPGA開發(fā)板)如圖所示:FLASH存儲器接口電路圖(Altera FPGA開發(fā)板)高速SDRAM存儲器接口電路設(shè)計(Altera FPGA開發(fā)板)如下

2012-08-16 18:49:43

+問題總結(jié))/樣品BOM——小批量低價BOM表分析工具.urlMOS管驅(qū)動電路設(shè)計秘籍(工作原理+電路設(shè)計+問題總結(jié))/電子行業(yè)采購神器.url[td]FPGA從0到1學(xué)習(xí)資料集錦(開發(fā)指南+電路圖集+例程源碼).zip2830KB...

2020-07-23 17:22:15

MOS管驅(qū)動電路設(shè)計秘籍(工作原理+電路設(shè)計+問題總結(jié))+FPGA從0到1學(xué)習(xí)資料集錦(開發(fā)指南+電路圖集+例程源碼)鏈接:https://pan.baidu.com/s

2020-07-21 18:52:16

基于FPGA的集成化PWM控制電路設(shè)計

2013-03-25 22:12:38

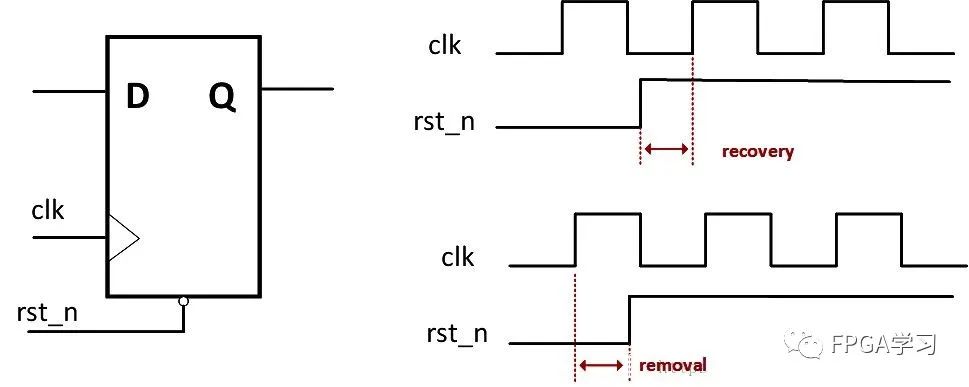

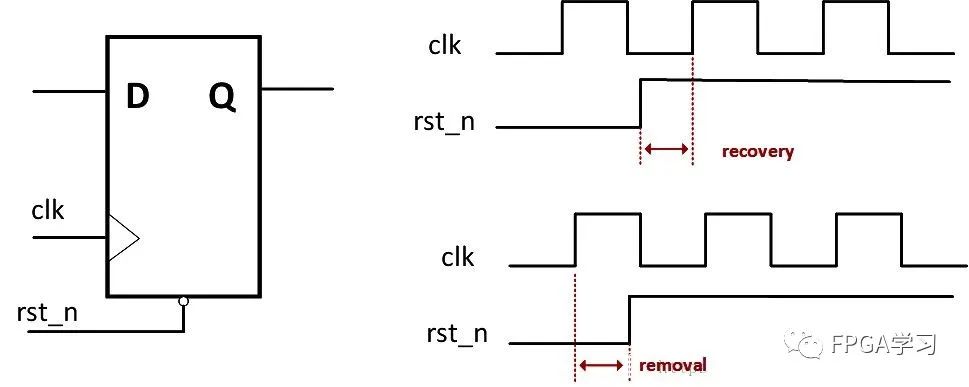

FPGA的同步電路設(shè)計基礎(chǔ)知識 同步電路設(shè)計將系統(tǒng)的狀態(tài)變化與時鐘信號同步,通過這種方法降低電路設(shè)計難度。一、觸發(fā)器定義:一種儲存1個二進制位的存儲單元,可以用做時序邏輯電路的記憶元件。FPGA邏輯

2019-12-11 15:02:36

`例說FPGA連載16:電源電路設(shè)計特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖2.9所示,J1為FPGA的電源插座,SW1為

2016-08-05 16:22:03

`例說FPGA連載20:NAND Flash電路與擴展電路設(shè)計特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖2.29所示,這是

2016-08-15 17:27:34

`例說FPGA連載9:FPGA板級電路設(shè)計五要素特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 和純粹基于PC機的各種軟件編程

2016-07-18 16:24:54

FPGA設(shè)計有別于DSP和ARM系統(tǒng),相比之下較為靈活和自由。主要是設(shè)計構(gòu)思好專用管腳的電路,通用I/O的連接可以自身定義。因而,FPGA電路設(shè)計中會有一些獨特的方法能夠參照。

2020-04-25 08:00:00

關(guān)于以太網(wǎng)到多路E1適配電路設(shè)計及FPGA實現(xiàn)你想知道的都在這

2021-05-06 06:17:04

開發(fā) ,不僅成本低、周期短 、可靠性高 ,而且具有完全的知識產(chǎn)權(quán) 。本文介紹 了一個以 公司可編程邏輯芯片一 為控制核心 、附加一定外圍電路組成的汽車尾燈控制電路。這篇論文是從中國知網(wǎng)付費下載的,請大家珍惜,幫忙頂起。基于FPGA的汽車尾燈控制電路設(shè)計與實現(xiàn)[hide][/hide]

2011-11-10 09:14:35

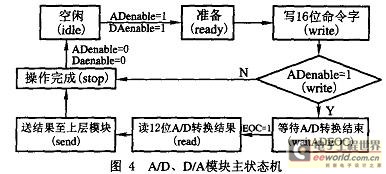

位數(shù)/模轉(zhuǎn)換(D/A)芯片,它采用串行數(shù)據(jù)輸入形式,即數(shù)字信號被一位一位地寫入AD7543數(shù)/模轉(zhuǎn)換(D/A)芯片中,因此,AD7543要與一個控制器配合使用才能發(fā)揮作用。那么,我們該如何利用AD7543和FPGA進行數(shù)/模轉(zhuǎn)換電路設(shè)計呢?

2019-08-01 06:19:16

FPGA芯片是由哪些部分組成的?如何去實現(xiàn)一種基于FPGA芯片的可重構(gòu)數(shù)字電路設(shè)計?

2021-11-05 08:38:57

大家好,我是電子愛好者新手,現(xiàn)在想學(xué)點數(shù)字電路設(shè)計。剛把數(shù)字電路這么課程學(xué)完。我想學(xué)電路設(shè)計,不知道如何下手。比如FPGA什么的,這些都怎么開始學(xué)習(xí)啊。請知情者指點下。謝謝

2013-08-02 08:17:31

承接各種電路設(shè)計,layout等工作,可以提供專業(yè)的解決方案,單片機、FPGA等嵌入式芯片設(shè)計,具有專業(yè)電子電路設(shè)計團隊,你的選擇成就未來!{:1:}

2016-12-09 17:51:59

基半導(dǎo)體激光器的遠距離語音通話電路設(shè)計; 1.遠距離聲音調(diào)制發(fā)射接受電路設(shè)計; 2.信號濾波放大電路設(shè)計; 3.聲音環(huán)境濾波和高性能放大電路設(shè)計;最好能有鎖相電路存在

2014-06-21 13:05:49

如圖是海德漢編碼器輸出信號調(diào)理電路,Z+,Z-為差分信號,電路的作用是將三角波信號經(jīng)過比較器調(diào)理成方波信號,但我不是太懂原理,希望大家能指教一下。

2018-12-03 09:37:16

我今年研二了,馬上就要畢業(yè)了,一直接觸硬件的項目。去年在普天的單板硬件研發(fā)實習(xí),學(xué)習(xí)了些單板電路設(shè)計的東西。我現(xiàn)在向往兩個方向發(fā)展,一是FPGA(因為模電實在搞不懂,覺得verilog HDL寫起來

2014-06-27 16:06:01

FPGA實現(xiàn)的綜合,測試,時序分析和板級調(diào)試;·帶領(lǐng)和指導(dǎo)其他工程師完成項目工作。 職位要求·本科或以上學(xué)歷,3年以上工作經(jīng)驗;·有相關(guān)產(chǎn)品的設(shè)計經(jīng)驗,在相關(guān)產(chǎn)品的研發(fā)中起核心作用;·熟練的邏輯電路設(shè)計

2012-06-26 10:20:28

待測器件特性。任職資格: 1、本科及以上學(xué)歷(資深者可放寬至專科),電子,自動化相關(guān)專業(yè)畢業(yè) ;2、2年以上模擬電路設(shè)計經(jīng)驗,能獨立設(shè)計數(shù)字及模擬電路,包括FPGA、單片機外圍電路選型,設(shè)計;3、具有

2016-11-30 11:07:23

請問有誰做過測試電路設(shè)計?用FPGA與單片機混合的電路!求交流,我QQ是724657165

2014-08-12 19:21:29

醫(yī)療行業(yè)搞硬件開發(fā),有用到FPGA,經(jīng)理一直強調(diào)這塊電路要注意,但也沒說有啥,想問一下FPGA在電路設(shè)計上需要注意什么?

2020-08-27 08:08:17

,我們還不如談?wù)?b class="flag-6" style="color: red">fpga電路。大部分公司里面,fpga其實是屬于硬件這塊的,至少通訊公司里面fpga是和硬件部門分在一起的。如果是芯片設(shè)計公司,fpga一般用作芯片原型設(shè)計的,也就是流片之前...

2021-12-15 07:40:10

漢粵精密過濾器濾芯 漢粵濾芯【1】國產(chǎn)品牌濾芯均為我司生產(chǎn)的替代原廠品牌濾芯,其過濾濾材采用德國原裝進口HV公司產(chǎn)品,注冊商標為“佳潔”牌。本公司涉及的其它品牌均無品牌意義,只是作為

2022-04-11 14:32:56

FPGA實用電路設(shè)計子項目自評報告一、本項目的背景、開展的目的和意義1、 背景在學(xué)習(xí)了《EDA技術(shù)》課程后,為更好地理論聯(lián)系實際,培養(yǎng)工科學(xué)生的動手能力,盡早成

2009-03-21 11:25:32 34

34 以太網(wǎng)到多路E1適配電路設(shè)計及FPGA實現(xiàn)

摘要:介紹了一種基于現(xiàn)場可編程門陣列(FPGA)的以太網(wǎng)數(shù)據(jù)-多路E1反向復(fù)用器同步電路設(shè)計,分析了FPGA具體實現(xiàn)過程中的一些常

2009-11-13 20:59:00 22

22 針對非相干體制擴頻測控系統(tǒng)信號模擬器的要求,提出的基于現(xiàn)場可編程門陣列(FPGA)與DSP 的信號模擬器距離模擬電路設(shè)計及實現(xiàn)方案。該距離模擬電路采用計數(shù)器與偽碼數(shù)控

2010-01-13 14:13:38 16

16 基于FPGA的兩相步進電機細分驅(qū)動電路設(shè)計摘要:在采用步進電機驅(qū)動的機構(gòu)中,為了提高定位精度,提出了一種基于FPGA 的兩相步進電機細分驅(qū)動電路的設(shè)計方案。

2010-05-11 16:09:41 50

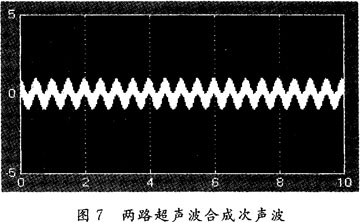

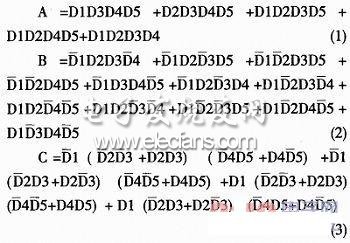

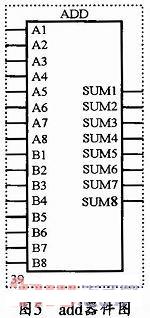

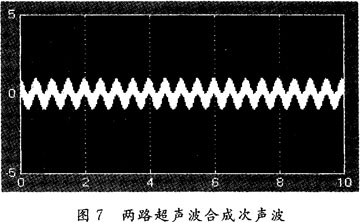

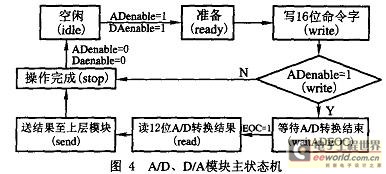

50 基于FPGA的次聲波合成的電路設(shè)計

摘要:次聲波是頻率在10一~20Hz的波,在生物醫(yī)學(xué)、氣象學(xué)、軍事等領(lǐng)域有著廣泛應(yīng)用前景,此頻段

2009-10-25 09:53:54 1525

1525

基于AD7543和FPGA的數(shù)/模轉(zhuǎn)換電路設(shè)計

引 言

數(shù)/模轉(zhuǎn)換(D/A)電路,是數(shù)字系統(tǒng)中常用的電路之一,其主要作用是把數(shù)字信號轉(zhuǎn)換成模擬信

2009-11-17 09:57:19 1843

1843 基于FPGA的多通道HDLC收發(fā)電路設(shè)計

HDLC(High Level Date Link Control)協(xié)議是通信領(lǐng)域中應(yīng)用最廣泛的協(xié)議之一,它是面向比特的高級數(shù)據(jù)鏈路控制規(guī)程,具有差錯檢測功能強大

2009-12-10 10:14:35 1435

1435 基于FPGA的PCB測試機硬件電路設(shè)計研究

引言

PCB 光板測試機基本的測試原理是歐姆定律,其測試方法是將待測試點間加一定的測試電壓,用譯碼電路選中PCB

2010-01-04 09:12:33 957

957

基于FPGA的光電抗干擾電路設(shè)計方案

光電靶的基本原理是:當(dāng)光幕內(nèi)的光通量發(fā)生足夠大的變化時,光電傳感器會響應(yīng)這種變化而產(chǎn)生電信號。這就

2010-02-09 10:31:20 627

627

傳統(tǒng)的距離門控電路多采用分立元器件,工作頻率和控制精度均十分有限,難于滿足重復(fù)頻率高的測距需求.通過分析高重復(fù)率距離門控的時序,提出并實現(xiàn)了一種基于FPGA的高重復(fù)率距離門控電路方法.該方法充分發(fā)揮了FPGA在運算、存儲、時鐘管理等方面的優(yōu)勢:采

2011-03-15 15:05:00 24

24 Altium Designer 6 是Ahium 公司推出的最新的板級電路設(shè)計系統(tǒng),它完美地綜合了原理 圖繪制、電路仿真、PCB 設(shè)計、設(shè)計規(guī)則檢查、FPGA 及邏輯器件設(shè)計等功能,為用戶提供 了全面的設(shè)計解

2011-03-23 10:48:11 446

446 FPGA的應(yīng)用,1.電路設(shè)計中FPGA的應(yīng)用,2.產(chǎn)品設(shè)計,3.系統(tǒng)級應(yīng)用

2011-09-08 17:33:05 5946

5946 在工程應(yīng)用中,雙向電路是設(shè)計者不得不面對的問題.在實際應(yīng)用中,數(shù)據(jù)總線往往是雙向的.如何正確處理數(shù)據(jù)總線是進行時序邏輯電路設(shè)計的基礎(chǔ).在程序設(shè)計過程中,關(guān)鍵技術(shù)在于:實體部

2011-11-11 10:27:13 2830

2830 采用了VHDL語言編程的設(shè)計方法,通過FPGA來實現(xiàn)按鍵消抖的硬件電路。論述了基于計數(shù)器、RS觸發(fā)器和狀態(tài)機3種方法來實現(xiàn)按鍵消抖電路,并給出仿真結(jié)果。通過下載到CycloneEP1C6T144芯片

2011-12-05 14:13:34 223

223 高速SDRAM存儲器接口電路設(shè)計(Altera FPGA開發(fā)板)如下圖所示:

2012-08-15 14:33:41 3326

3326

異步SRAM存儲器接口電路設(shè)計(Altera FPGA開發(fā)板)如圖所示:

2012-08-15 14:37:05 3862

3862

廣東高云半導(dǎo)體科技股份有限公司(以下簡稱“高云半導(dǎo)體”)今日宣布發(fā)起IP軟核平臺—星核計劃,該計劃旨在打造具有中國自主知識產(chǎn)權(quán)的可重復(fù)使用的集成電路設(shè)計平臺。星核計劃以FPGA為設(shè)計及驗證平臺,積累

2014-11-03 16:06:05 1745

1745 分析了FPGA器件發(fā)生單粒子效應(yīng)的空間分布特性,設(shè)計并實現(xiàn)了一種面向FPGA單粒子軟錯誤的檢測電路。將該電路放置在FPGA待檢測電路的附近,利用單粒子效應(yīng)的空間特性,則可以根據(jù)檢測模塊的狀態(tài)變化

2015-12-31 09:25:13 8

8 基于FPGA的高速USB2.0數(shù)據(jù)采集系統(tǒng)主控電路設(shè)計

2016-01-04 15:31:55 0

0 基于FPGA的超聲波傳感器前端電路設(shè)計..

2016-01-04 17:03:55 14

14 基于FPGA的慣性平臺測試保護電路設(shè)計..

2016-01-04 17:03:55 7

7 基于FPGA的光電系統(tǒng)同步自適應(yīng)電路設(shè)計與實現(xiàn)

2016-01-04 17:03:55 10

10 設(shè)計和后處理功能,還可以進行從原理圖到 PCB 布線工具包的無縫隙數(shù) 據(jù)傳輸。 對于電路設(shè)計者來說,能滿足電路電子設(shè)計與仿真,滿足從參數(shù)到產(chǎn)品的 設(shè)計要求,節(jié)約電路設(shè)計時間,降低實驗費用,提高設(shè)計的可靠性。

2016-05-13 15:07:44 26

26 電路設(shè)計[FPGA]設(shè)計經(jīng)驗,有需要的下來看看

2016-05-20 11:16:35 46

46 電子專業(yè)單片機相關(guān)知識學(xué)習(xí)教材資料——FPGACPLD數(shù)字電路設(shè)計經(jīng)驗,感興趣的小伙伴們可以瞧一瞧。

2016-09-13 17:46:48 0

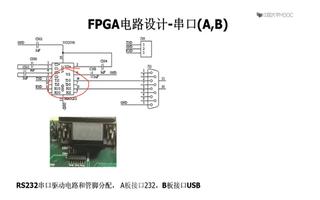

0 基于FPGA的串口通信電路設(shè)計

2017-01-24 17:30:13 33

33 基于FPGA技術(shù)的RS232接口時序電路設(shè)計方案

2017-01-26 11:36:55 29

29 數(shù)字電路設(shè)計方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 在論壇里有人發(fā)帖子,問關(guān)于FPGA的硬件電路問題,我想涉及到這個問題的基本都是硬件工程師或者在讀學(xué)生,所以我介紹一下我是怎么學(xué)習(xí)FPGA的硬件電路設(shè)計的吧!

2017-02-11 12:55:11 25430

25430 基于FPGA短程激光相位測距儀數(shù)字信號處理電路設(shè)計_趙一霽

2017-03-19 11:38:26 11

11 基于FPGA的壓電陀螺數(shù)字化檢測電路設(shè)計_李國斌

2017-03-19 19:07:17 0

0 圖像處理技術(shù)應(yīng)用越來越廣泛,特別是工業(yè)檢測領(lǐng)域。然而,圖像處理技術(shù)應(yīng)用的基礎(chǔ)是圖像的獲取,為了更加靈活地設(shè)計各種應(yīng)用產(chǎn)品,本課題研究基于FPGA的面陣 CCD驅(qū)動傳輸電路設(shè)計,利用該電路能夠獲取高質(zhì)量、高分辨率的圖像,為后續(xù)的圖像處理技術(shù)應(yīng)用打下基礎(chǔ)。

2017-08-30 16:38:07 3

3 DSP和FPGA的HDLC協(xié)議通訊電路設(shè)計

2017-10-19 14:46:11 7

7 基于FPGA的調(diào)焦電路設(shè)計方案資料下載

2018-05-07 15:53:08 9

9 .docx DC-DC升壓電路.docx FPGACPLD數(shù)字電路設(shè)計經(jīng)驗分享.docx MIC電路工作總結(jié).docx MOS管驅(qū)動電路詳解.docx PCB電路設(shè)計指南(經(jīng)典).docx PLC輸出電路

2019-01-11 18:19:38 0

0 在設(shè)計可編程門陣列(FPGA)電路時,必須極端重視電源問題,從而使最終產(chǎn)品能在所有可能的條件下無缺陷工作并處于最優(yōu)狀態(tài)。FPGA 電路電源有兩項需考慮的問題: FPGA 電路上電要求和電路功耗分析。這篇文章針對這兩方面的要求,討論您可能遇到的問題,以及解決方案。

2019-05-31 14:39:13 2442

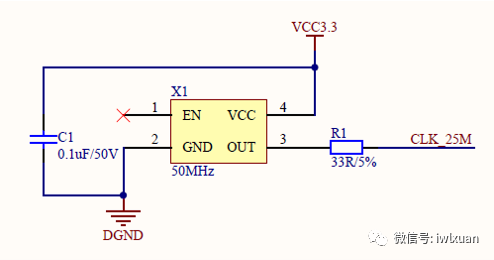

2442 本文檔的主要內(nèi)容詳細介紹的是FPGA教程之FPGA硬件最小系統(tǒng)設(shè)計的詳細資料說明包括了:1.FPGA最小系統(tǒng)概念以及硬件系統(tǒng)的構(gòu)成,2.FPGA主芯片電路設(shè)計,3.JTAG下載與調(diào)試接口,4.高速

2019-04-04 17:18:48 101

101 中國大學(xué)MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進階應(yīng)用。

2019-08-06 06:08:00 3083

3083 中國大學(xué)MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進階應(yīng)用。

2019-12-02 07:08:00 2118

2118

本教程介紹Quartus Prime CAD系統(tǒng)。本文概述了用fpga器件實現(xiàn)的典型電路設(shè)計CAD流程,并說明了該流程是如何在quartus prime軟件中實現(xiàn)的。通過給出使用quartus prime軟件在intel-fpga設(shè)備中實現(xiàn)非常簡單的電路的逐步說明,說明了設(shè)計過程。

2019-09-20 08:00:00 6

6 FPGA設(shè)計有別于DSP和ARM系統(tǒng),相比之下較為靈活和自由。主要是設(shè)計構(gòu)思好專用管腳的電路,通用I/O的連接可以自身定義。因而,FPGA電路設(shè)計中會有一些獨特的方法能夠參照。

2020-03-20 15:53:36 1531

1531 本文檔的主要內(nèi)容詳細介紹的是FPGA的硬件電路設(shè)計教程和FPGA平臺資料簡介包括了:FPGA技術(shù)概述;主流FPGA器件介紹;VIRTEX-5 FPGA電路設(shè)計;V4LX160 FPGA平臺介紹;

2020-07-06 18:11:22 158

158 通常情況下,時鐘的分頻在FPGA設(shè)計中占有重要的地位,在此就簡單列出分頻電路設(shè)計的思考思路。

2020-07-10 17:18:03 2192

2192 利用FPGA的在系統(tǒng)下載或重新配置功能,可以在電路設(shè)計和調(diào)試時改變整個電路的硬件邏輯關(guān)系,而不需要改變印制電路板的結(jié)構(gòu)。

2021-05-12 10:46:10 25

25 FPGA CPLD數(shù)字電路設(shè)計經(jīng)驗分享.(電源技術(shù)發(fā)展怎么樣)-FPGA CPLD數(shù)字電路設(shè)計經(jīng)驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 。 下面將討論FPGA/CPLD的復(fù)位電路設(shè)計。 2、分類及不同復(fù)位設(shè)計的影響 根據(jù)電路設(shè)計,復(fù)位可分為異步復(fù)位和同步復(fù)位。 對于異步復(fù)位,電路對復(fù)位信號是電平敏感的,如果復(fù)位信號受到干擾,如出現(xiàn)短暫的脈沖跳變,電路就會部分或全部被

2023-04-06 16:45:02 782

782 前面在時序分析中提到過亞穩(wěn)態(tài)的概念,每天學(xué)習(xí)一點FPGA知識點(9)之時序分析并且在電路設(shè)計中如果不滿足Tsu(建立時間)和Th(保持時間),很容易就出現(xiàn)亞穩(wěn)態(tài);在跨時鐘域傳輸?shù)囊幌盗写胧┮彩菫榱私档蛠喎€(wěn)態(tài)發(fā)生的概率。

2023-05-25 15:55:43 885

885

小編在本節(jié)介紹FPGA芯片外圍電路設(shè)計規(guī)范和配置過程,篇幅比較大,時鐘的設(shè)計原則就有17條,伙伴們耐心讀一讀。

2023-08-15 16:18:11 3374

3374

電子發(fā)燒友網(wǎng)站提供《FPGA/CPLD數(shù)字電路設(shè)計經(jīng)驗分享.pdf》資料免費下載

2023-11-21 11:03:12 3

3

電子發(fā)燒友App

電子發(fā)燒友App

評論