ARM在硬件上不支持除法指令,編譯器是通過調用C庫函數來實現除法運算的,有許多不同類型的除法程序來適應不同的除數和被除數。但直接利用C庫函數中的標準整數除法程序,根據執行情況和輸入操作數的范圍,要花費20~100個周期,消耗較多的軟件運行時間。在實時嵌入式應用中,對時間參數較為敏感,故可以考慮如何優化避免除法消耗過多的CPU運行時間。

除法和模運算(/和%)執行起來比較慢,所以應盡量避免使用。但是,除數是常數的除法運算和用同一個除數的重復除法,執行效率會比較高。在ARM中,可以利用單條MUL指令實現乘法操作。本文將闡述如何用乘法運算代替除法運算,以及如何使除法的次數最少化。

1 避免除法運算

在非嵌入式領域,因為CPU運算速度快、存儲器容量大,除法操作通常都是不加考慮直接使用的。但在嵌入式領域,首先需要考慮的是這些除法操作是否是必須的。以對環形緩沖區操作為例,經常要用到除法,其實完全可以避免這些除法運算。

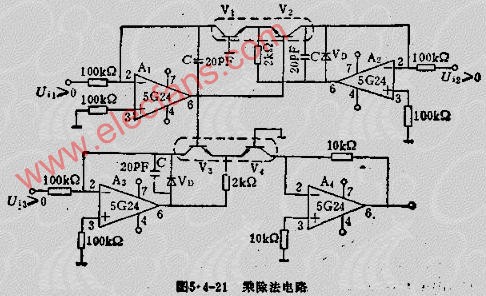

?

假定有一個buffer_size大小的環形緩沖區,如圖1所示,offset指定目前所在的位置。通過increment字節來增加offset的值,一般是這樣寫的:

0ffset=(Offset+increment)%buffer_size;

效率更高的寫法是:

offset+=increment;

if(offset>=buffer_size){

offset-=buffer_size;

}

第一種寫法要花費50個周期,而第二種因為沒有除法運算,只須花費3個周期。這里假定increment

如果不能避免除法運算,那么就應盡量使除數和被除數是無符號的整數。有符號的除法程序執行起來更加慢,因為它們先要取得除數和被除數的絕對值,再調用無符號除法運算,最后再確定結果的符號。

2 充分利用商和余數

許多C語言庫中的除法函數返回商和余數。換句話說,每一個除法運算,余數是可以無償得到的,反之亦然。例如,要在屏幕緩沖區找到偏移量為offset的屏幕位置(x,y),可以這樣寫:

typeclef struct{

int x;

int y;

}point;

point getxy_v1(unsigned int offset,unsigned int bytes_per_line){

point p;

p.y=offset/lt)ytes_per_line;

p.x=offset - p.y* bytes_per_line;

return p;

}

這里,似乎對p.x使用減法和乘法,少了一次除法運算;但是,實際上使用模運算或者取余操作效率更高,對getxy_v1改進如下:

point getxy_v2(unsigned int offset,unsigned int bytes_per_line){

point P;

P.x=offset%bytes_per_1ine;

P.y=offset/bytes_per_line;

return P;

}

從下面編譯器的輸出結果可以看到,只有一次除法調用。實際上,這個程序要比前面的getxy_vl少4條指令(注意,并不是對所有的編譯器和C庫都有這樣的結果)。

getxy_v2

STMFD r13!,{r4,r14};保存r4,lr人堆棧

MOV r4,r0 ;賦值后r4保存的為點P基址

MOV r0,r2 ;r0=bytes_per_line

BL rt_udiv ;調用無符號除法例程

(r0.;r1)=(rl/r0,rl%r0)

STR r0,[r4,#4] ;P.y=offset/bytes_per_line

STR rl,[r4,#o] ;P.x=offset%bytes_per_line

LDMFD r13!,(r4,pc);恢復上下文,返回

3 把除法轉換為乘法

在程序中,同一個除數的除法經常會出現很多次。在前面的例子中,bytes_per_line的值在整個程序中都是固定不變的。又如3到2笛卡爾坐標變換,其中就使用了同一個除數兩次:

(x,Y,x)→(x/z,y/z)

這種情況下,使用cache指令中的值1/z,并使用1/z的乘法來代替除法運算,效率會更高。另外,要盡可能使用int類型的運算,避免使用浮點運算。

下面將更加偏重于從數學和理論的角度分析,把重復除法轉換成乘法運算。

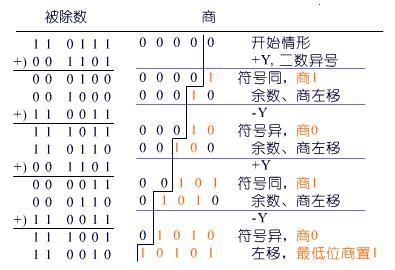

下面來區分精確數學意義上的除法和整型除法運算:

n/d,即整數n被分成整數d份,結果趨向于O(與C語言相同);

n%d,即n被d除之后的余數,就是n--d(n/d);

n/d=n·d-1,即真正數學意義上的n被d除。

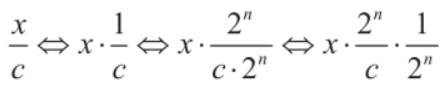

當使用整型除法時,最容易估算d-1值的方法是計算232/d。然后,就可以估算n/d為:

(n(232/d))/232 (1)

在執行n的乘法時,需要精確到64位。對于這種方法,會出現如下問題:

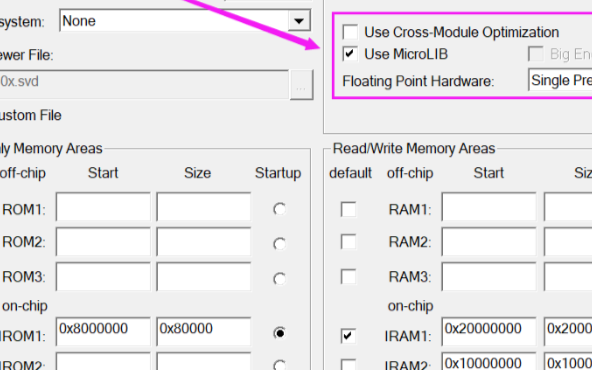

為了計算232/d,由于一個unsigned int類型的數據放不下232,編譯器要使用64位long long類型的數,而且必須指定除法為(1 ull<<32)/d。這種64位的除法比32位的除法執行起來要慢得多。

如果d碰巧是1,那么232/d就不再適合于un—signed int數據類型。

上面的做法似乎很好,而且解決了這兩個問題。那么,再來看一下用(232一1)/d代替232/d。 令

s=0xffffffff ul/d (2)

?

以上n/d-2,q,n/d+1為整數值,所以可得q=n/d或q=(n/d)一1,即初步估計的結果q與正確值n/d有可能存在偏差1。可以發現,通過計算余數r=n—q·d(O≤r<2d)是比較容易的。下面的代碼糾正了這個結果:

r=n--q*d;/*初步估計結果余數r的范圍為O≤r<2d*/

if(r>=d){/*若需要校正*/

r-=d;/*校正r,使O≤r

n++;/*相應商加1進行校正*/

} /*得正確結果q=n/d和r=n%d*/

下面給出一個實例,用上面的算法完成了N個元素的數組被d除。首先,計算上面所說的s值,然后用乘以5來代替每個被d除的除法。64位的乘是很容易實現的,因為ARM中有一條指令UMULL,可以進行2個32位數相乘,給出一個64位的結果。

void scale(

unsigned int*dest; /*目的數據*/

unsigned int*src; /*源數據*/

unsignedInt d; /*分母d*/

urlslglaedInt N;) /*數據長度*/

{

unsigned int s=0xFFFFFFFFu/d;

do{

unsigned int n,q,r;

n=*(src++);

q=(urtslgrted int)(((unsined tong long)n*s)>>32);

r=n*d;

if(r>=d){ /*若需要對商進行校正*/

q++;

}

*(dest++)=q;

}while(--N);

}

這里假定除數和被除數都是32位的無符號整數。當然,使用32位乘法進行16位的無符號數計算,或者使用1 28位乘法進行64位數計算,運算規則是一樣的。可以為特定的數據選擇最窄的運算寬度。如果數據是16位的,那么就設置s=(216一1)/d,然后用標準的整型乘法來求值q。

4 結論

如果不能避免除法運算,那么應盡可能使用除法程序同時產生商n/d和余數n%d的好處。對于重復對一除數d的除法.預先計算好s=(2k一1)/d,用乘以s的2k位乘法來代替除以d的k位無符號整數除法,可大大減少由于直接使用除法操作引入的指令周期數。

電子發燒友App

電子發燒友App

評論