隨著平板顯示技術(shù)的不斷更新,大型LED顯示系統(tǒng)利用發(fā)光二極管構(gòu)成的點(diǎn)陣模塊或像素單元組成大面積顯示屏,主要顯示字符、圖像等信息,具有低功耗、低成本、高亮度、長(zhǎng)壽命、寬視角等優(yōu)點(diǎn)。近年來(lái)廣泛應(yīng)用在證券交易所、車站機(jī)場(chǎng)、體育場(chǎng)館、道路交通、廣告媒體等場(chǎng)所。

通常用單一單片機(jī)作為主控器件控制和協(xié)調(diào)大屏幕顯示。由多片單片機(jī)構(gòu)成的多處理器系統(tǒng),其中一片作為主CPU,其他作為子CPU共同控制大屏幕的顯示,該系統(tǒng)可以減輕主CPU 的負(fù)擔(dān),提高了LED點(diǎn)陣的刷新頻率。但單片機(jī)的驅(qū)動(dòng)頻率有限,無(wú)法驅(qū)動(dòng)等分辨率LED屏幕,尤其是對(duì)于多灰度級(jí)彩色大屏幕,數(shù)據(jù)送到顯示屏之前要進(jìn)行灰度調(diào)制重現(xiàn)圖像的色彩,對(duì)數(shù)據(jù)的處理速度要求更高,單片機(jī)控制在速度上無(wú)法滿足上述要求。因此該方案主要應(yīng)用于實(shí)時(shí)性要求不高的場(chǎng)合,主要進(jìn)行一些文字、圖片等靜態(tài)異步顯示的控制。視頻圖像信號(hào)頻率高、數(shù)據(jù)量大,要求實(shí)時(shí)處理,采用FPGA/CPLD設(shè)計(jì)控制電路,其中的同步控制、主從控制、讀寫控制和灰度調(diào)制等大量電路進(jìn)行了集成,簡(jiǎn)化系統(tǒng)結(jié)構(gòu),便于調(diào)試且系統(tǒng)結(jié)構(gòu)緊湊,工作可靠。與單片機(jī)控制電路相比,電路結(jié)構(gòu)明顯簡(jiǎn)潔,電路的面積減小,可靠性增強(qiáng),調(diào)試也更為簡(jiǎn)單,由于FPGA/CPLD可以并行處理多個(gè)進(jìn)程,比起單片機(jī)對(duì)任務(wù)的順序處理效率更高,點(diǎn)陣的刷新頻率也隨之提高。

對(duì)實(shí)時(shí)性要求較高、數(shù)據(jù)量較大的場(chǎng)合下,可編程邏輯器件是首選的核心數(shù)據(jù)處理器。本系統(tǒng)考慮對(duì)于傳輸視頻數(shù)據(jù)大小和驅(qū)動(dòng)LED大屏幕刷新頻率的要求,LED發(fā)送卡、接收卡均采用FPGA作為核心處理器,筆者選擇Xilinx公司基于90nm工藝制造的XC3S250E-FTG256,內(nèi)有25萬(wàn)邏輯門,最高頻率可以達(dá)到600MHz,完全可以滿足系統(tǒng)速度的要求在系統(tǒng)中作為掃描控制單元,同時(shí)以MCU芯片為主控制單元。采用該方案可以有效簡(jiǎn)化顯示屏的電路結(jié)構(gòu),從而提高了整個(gè)控制系統(tǒng)的靈活性和可靠性。

1 系統(tǒng)的組成和工作原理

該系統(tǒng)采用89C51單片機(jī)和SDRAM 組成控制中心,由基于Xilinx公司的FPGA的90nm工藝制造的XC3S250E-FTG256和RAM 組成掃描控制模塊,以FLASH作為存儲(chǔ)器模塊,采用以太網(wǎng)傳輸數(shù)據(jù),組成LED屏的控制系統(tǒng)。系統(tǒng)結(jié)構(gòu)如圖1所示。其工作原理為:主機(jī)通過(guò)TFTP協(xié)議將圖片傳輸給系統(tǒng)以太網(wǎng)接口模塊,以太網(wǎng)接口模塊解析協(xié)議,接收?qǐng)D片數(shù)據(jù),然后將數(shù)據(jù)傳輸給MCU,MCU 將接收到的數(shù)據(jù)寫入存儲(chǔ)模塊NAND Flash.在顯示時(shí),MCU讀取FLASH 中的數(shù)據(jù),通過(guò)SPI接口將數(shù)據(jù)傳輸給FPGA掃描控制模塊,經(jīng)掃描控制模塊處理后傳輸?shù)絃ED屏幕上顯示。

?

圖1 基于FPGA和MCU的LED顯示屏控制系統(tǒng)框圖

2 硬件系統(tǒng)設(shè)計(jì)

2.1存儲(chǔ)器電路設(shè)計(jì)

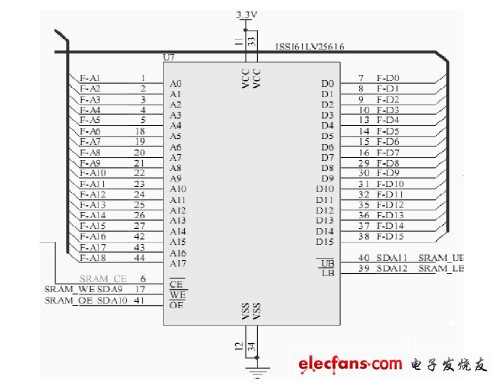

本系統(tǒng)中需要用2片RAM 芯片作為緩存來(lái)存儲(chǔ)視頻數(shù)據(jù),并以乒乓方式進(jìn)行快速讀寫操作。目前主要有動(dòng)態(tài)存儲(chǔ)器(DRAM)和靜態(tài)存儲(chǔ)器(SRAM),SRAM 的讀寫時(shí)間短,靜態(tài)功耗比較低,總線利用率高,它不需要刷新電路就能保存內(nèi)部存儲(chǔ)的數(shù)據(jù),但是它的集成度較低,相同的容量占用體積大,價(jià)格較高,主要用于性能要求較高的領(lǐng)域。

DRAM 只能將數(shù)據(jù)保持很短的時(shí)間,它使用電容存儲(chǔ),必須經(jīng)常刷新電路來(lái)保存數(shù)據(jù),它的讀寫過(guò)程比較復(fù)雜,時(shí)間較長(zhǎng),動(dòng)態(tài)功耗較大,總線利用率比較低。不過(guò)DRAM 的存儲(chǔ)容量大,價(jià)格便宜,被大量用在服務(wù)器和電腦中。由于DRAM 讀寫過(guò)程比較復(fù)雜,本系統(tǒng)要求存儲(chǔ)器有快速的讀寫響應(yīng),所以設(shè)計(jì)中選用SRAM 作為存儲(chǔ)器。本系統(tǒng)所用的LED屏大小為512×64,每個(gè)像素?cái)?shù)據(jù)(RGB)占用24bit,則一場(chǎng)畫面的數(shù)據(jù)量為512×64×24=768kbits.本設(shè)計(jì)選用ISSI公司的IS61LV25616芯片來(lái)存儲(chǔ)視頻數(shù)據(jù)。SAA7111輸出16bit視頻信號(hào),16位數(shù)據(jù)線正好方便存儲(chǔ)數(shù)據(jù)。它的容量為256×1 024×16bit,足夠存儲(chǔ)一場(chǎng)視頻數(shù)據(jù),并有留有充足的容量供系統(tǒng)以后的升級(jí)。SRAM 的電路設(shè)計(jì)如圖2所示。

?

圖2 SRAM 電路

2.2 FPGA的硬件設(shè)計(jì)

FPGA的硬件設(shè)計(jì)如圖3所示。FPGA 需要提供大量的I/O引腳和高速的顯示控制信號(hào),所選用的基于Xilinx公司的FPGA 的90nm 工藝制造的XC3S250E-FTG256可以滿足設(shè)計(jì)的要求。

?

圖3 FPGA的硬件結(jié)構(gòu)

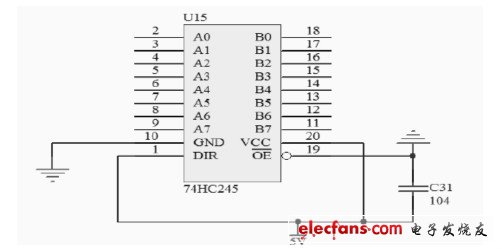

FPGA采用的電壓是3.3V,而LED屏體顯示電路的電壓是5V的TTL邏輯電平,因此需要進(jìn)行電平轉(zhuǎn)換的電路。這個(gè)電路由74HC245構(gòu)成,工作電壓為5V,74HC245采用CMOS工藝,是一種三態(tài)輸出、8組總線收發(fā)器,其輸入電平兼容3.3V系統(tǒng),使用外接的5V電源將輸出電平提升到5V,同時(shí)為各種控制和數(shù)據(jù)信號(hào)提供驅(qū)動(dòng)能力。74HC245的電路如圖4所示。其中:OE為輸出控制引腳,低電平為有效;DIR引腳用于控制轉(zhuǎn)換方向,接高電平時(shí)表示從A向B轉(zhuǎn)換,A0~A7用于輸入數(shù)據(jù)信號(hào),B0~B7用于輸出轉(zhuǎn)換后的數(shù)據(jù)信號(hào)。

?

圖4 74HC245驅(qū)動(dòng)電路

2.4顯示板的驅(qū)動(dòng)電路

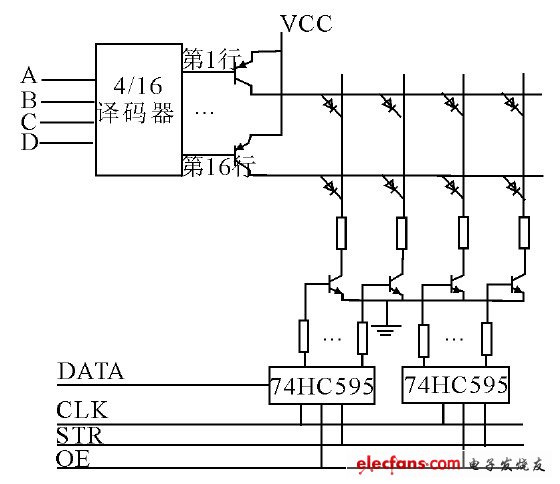

LED顯示板的面積很大,它的正面由LED 顯示塊級(jí)聯(lián)而成,背面是驅(qū)動(dòng)電路。由于LED的驅(qū)動(dòng)電流相對(duì)較大,驅(qū)動(dòng)電路應(yīng)盡量和LED點(diǎn)陣模塊靠近。因此行列驅(qū)動(dòng)器一般都安裝在屏體的背面。LED顯示板的驅(qū)動(dòng)電路中采用了74HC595芯片,是硅結(jié)構(gòu)的CMOS器件,兼容低電壓TTL電路,具有8位串入并出的移位、并行鎖存和三態(tài)輸出功能。移位寄存器和鎖存器使用獨(dú)立的時(shí)鐘,數(shù)據(jù)SDATA 在SCLK的上升沿輸入移位寄存器,在LT的上升沿進(jìn)入的鎖存器中去。當(dāng)使能信號(hào)OE為低電平時(shí),鎖存器的數(shù)據(jù)輸出到LED.74HC595芯片可以解決數(shù)據(jù)顯示和數(shù)據(jù)串行傳輸在時(shí)間上的沖突問(wèn)題,在顯示1行各列數(shù)據(jù)的同時(shí),可以準(zhǔn)備下1列的LED數(shù)據(jù)。以1/16行掃描為例,LED顯示板的驅(qū)動(dòng)電路如圖5所示。

CLK是移位寄存器時(shí)鐘,每個(gè)脈沖將引起1位數(shù)據(jù)移入74HC595中,當(dāng)1行的數(shù)據(jù)全部移完后,鎖存信號(hào)LT控制數(shù)據(jù)從74HC595的寄存器移入鎖存器。A、B、C、D是行掃描信號(hào),其中A是最低位,通過(guò)4/16譯碼器控制LED屏的行掃描。OE是消影信號(hào),它可以選擇控制行信號(hào)或列信號(hào),用于LED點(diǎn)陣是否能被點(diǎn)亮和控制整屏的亮度。如果OE控制列信號(hào),它接74HC595芯片的OE端,因?yàn)橹挥挟?dāng)OE為低電平時(shí)74HC595的輸出才有效,否則輸出三態(tài)。如果OE控制行信號(hào),它接到4/16譯碼器的使能端,低電平時(shí)行掃描不起作用。

圖5 LED顯示板的驅(qū)動(dòng)電路

3 系統(tǒng)軟件設(shè)計(jì)

整個(gè)系統(tǒng)的軟件包括2部分:上位機(jī)應(yīng)用軟件和嵌入制單元軟件。上位機(jī)軟件編輯在LED顯示屏上顯示的數(shù)息,并實(shí)現(xiàn)與下位機(jī)的通信;嵌入式控制單元軟件實(shí)現(xiàn)了接收和存儲(chǔ)、數(shù)據(jù)輸出和圖像顯示方式變換,從而實(shí)現(xiàn)LED屏的控制。

3.1上位機(jī)應(yīng)用軟件

上位機(jī)應(yīng)用軟件用Visual C++編寫,主要實(shí)現(xiàn)顯示的編輯與通訊的功能。該軟件運(yùn)行于WindowsXP環(huán)境中,方便用戶使用。完成的功能有:(1)對(duì)顯示信息進(jìn)行編輯、修改功能,也可以直接調(diào)用Windows中的256色畫圖文件(*.bmp);(2)在上位機(jī)上對(duì)顯示的內(nèi)容進(jìn)行預(yù)覽,以保證有較好的顯示效果;(3)依照上位機(jī)與I2C接口模塊的協(xié)議,將信息傳輸給系統(tǒng)以I2C接口模塊,從而實(shí)現(xiàn)顯示數(shù)據(jù)的更新。

3.2嵌入式控制單元的軟件

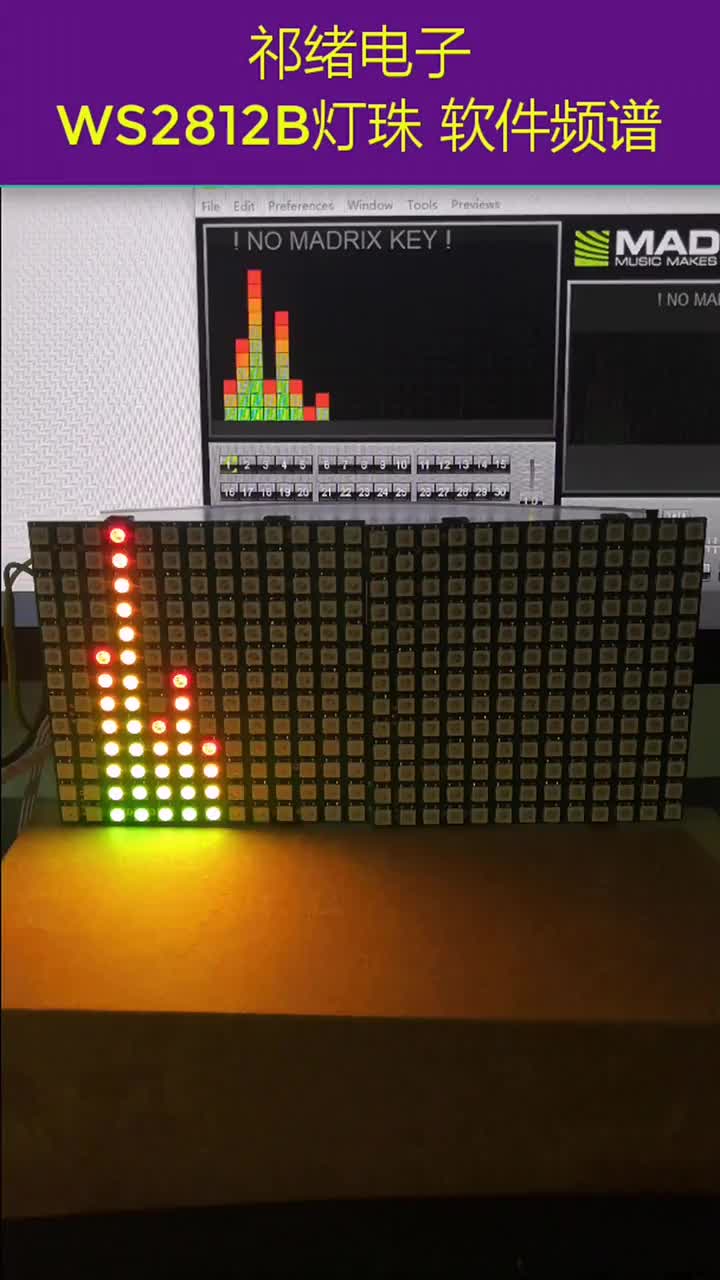

嵌入式控制單元的軟件實(shí)現(xiàn)以下3大功能:數(shù)據(jù)接收和存儲(chǔ)、數(shù)據(jù)輸出和圖像顯示方式變換。(1)依照顯示屏與上位機(jī)之間的通訊協(xié)議,與上位機(jī)進(jìn)行通訊,接收顯示數(shù)據(jù),存入Flash存儲(chǔ)器。(2)將待顯示的數(shù)據(jù)從Flash存儲(chǔ)器中取出,對(duì)數(shù)據(jù)進(jìn)行處理,實(shí)現(xiàn)上移、下移、左移、右移等豐富多彩的圖像顯示效果。(3)通過(guò)SPI接口將數(shù)據(jù)傳輸給掃描控制模塊,F(xiàn)PGA通過(guò)串并轉(zhuǎn)換等將數(shù)據(jù)轉(zhuǎn)換成適合LED屏驅(qū)動(dòng)電路格式的數(shù)據(jù),然后傳到LED屏幕上顯示出來(lái),仿真如圖6,7所示。

?

圖6 軟件模擬顯示效果

?

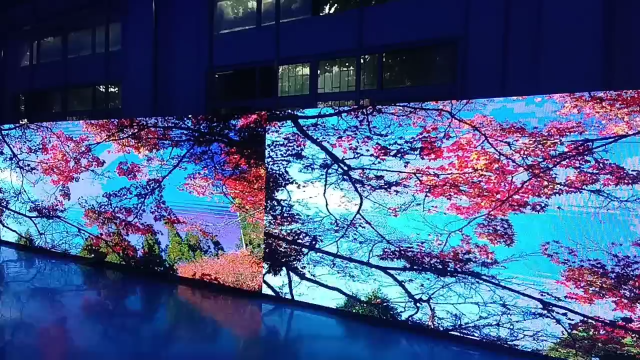

圖7 LED顯示屏實(shí)際顯示效果

4 結(jié)語(yǔ)

與傳統(tǒng)的基于單片機(jī)的LED屏控制系統(tǒng)相比較,該系統(tǒng)在不增加系統(tǒng)成本的情況下,可支持256灰度級(jí)的全彩圖文信息的顯示,可以播放全彩動(dòng)畫;可存儲(chǔ)較大容量的數(shù)據(jù)(64MB);通過(guò)I2C接口快速傳輸數(shù)據(jù),為顯示區(qū)域較大、顯示內(nèi)容切換頻繁的大屏幕LED顯示控制系統(tǒng)提供良好的解決方案。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論