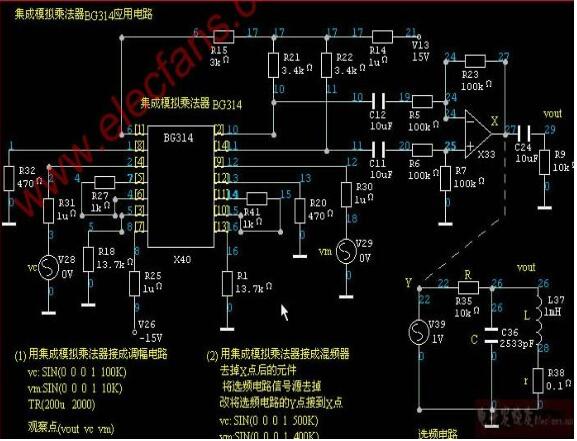

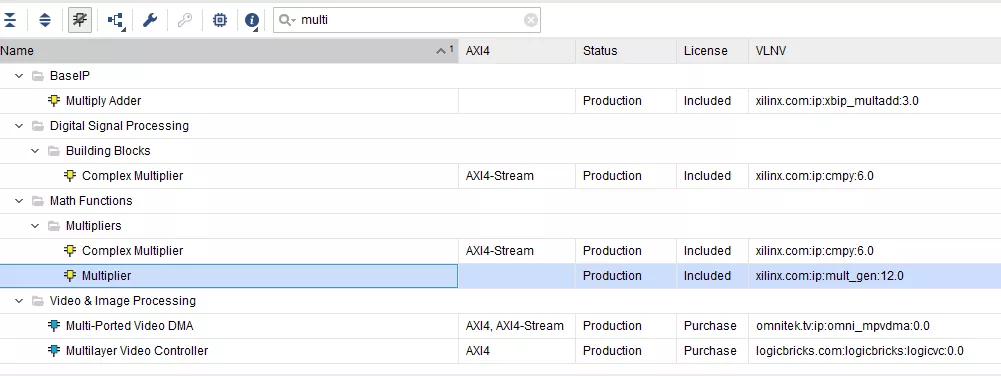

模擬乘法器視頻開關電路圖

2010-10-02 09:25:56 2893

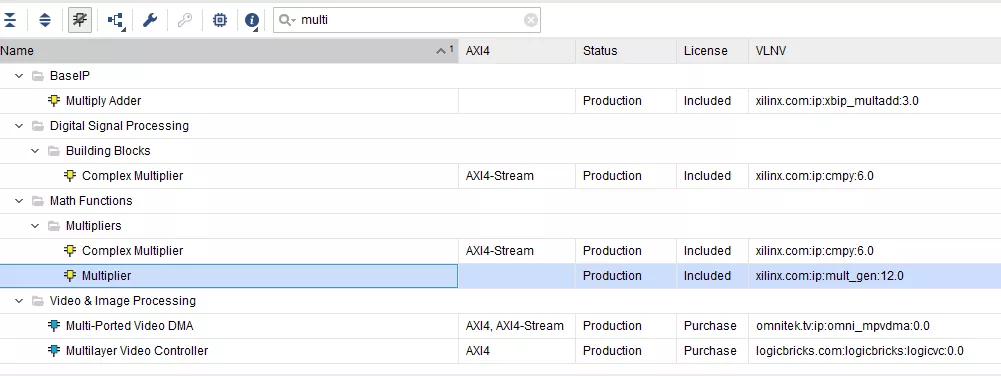

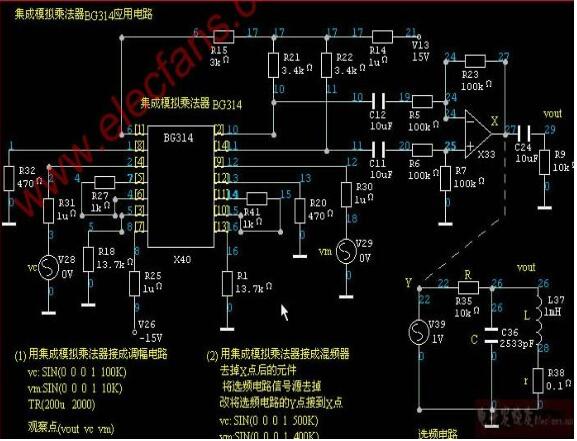

2893 剛接觸學習FPGA,懂得verilog HDL的基礎語法,有一塊帶XILINX的ZYNQ xc7z020的開發(fā)板,開發(fā)軟件用的是vivado;現(xiàn)在要設計一個16位的乘法器,功能已經實現(xiàn)。但需要考查

2018-02-25 16:03:46

的乘法器,功能已經實現(xiàn)。但需要考查性能指標:功耗、速度、吞吐量、覆蓋率。但對這幾個概念沒有太大的了解①請問對于一個乘法器而言這幾個方面指的是什么?②在Project Summary中有一個

2018-02-25 21:12:01

fpga中定點乘法器設計(中文)目錄聲明 ………………………………………………………………………………………… 10、 約定

2012-08-12 11:59:01

怎樣做一個乘法器電路

2013-01-09 18:26:48

請問TI有沒有類似AD835這樣的乘法器??

2018-06-21 02:36:06

乘法器和混頻器的區(qū)別 表面上看,都是做“乘法”了,其實區(qū)別很大。 乘法器,一般叫模擬乘法器,是用于

2009-11-13 16:37:25

請問關于乘法器的Verilog 程序中,移位累加具體每一步是怎么走的,自己琢磨了一番,感覺不是太懂,求高手解釋。(明白二進制乘法的計算過程)

2015-10-17 23:08:02

AVR的硬件乘法器8X8的嗎,數(shù)據(jù)手冊上是這么寫的。結果是16位的他這個乘法器應該是內核自帶的吧,還是外設呢如果用CV編譯,如何調用乘法器呢數(shù)據(jù)手冊上只給出了匯編代碼,如果是用c語言如何調用呢,還是不用調用直接寫式子就可以了呢?

2020-07-22 08:00:51

Altera的FPGA內置的乘法器為何是18位的?

2023-10-18 07:01:41

問題:專用乘法器不適用于FPGA而是模擬工作正常。我試過的:在我的一個設計中,我使用10x10bit乘法器。原來我只是使用w6 = Vout * Vout。在模擬中,這似乎適用于我的設備利用率總結它

2019-05-29 06:12:17

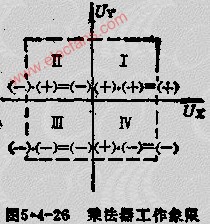

我想請問一下各位大佬四象限乘法器的四象限是什么意思呢?可以具體 說明一下嗎?謝謝啦!

2019-08-06 15:14:13

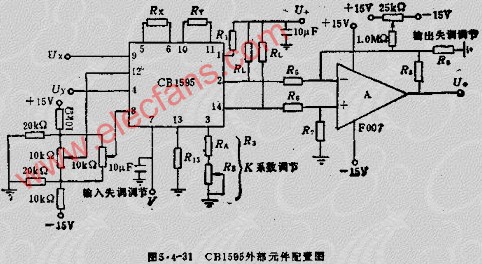

mc1496模擬乘法器

2015-08-08 20:50:54

求大神解答用AD633乘法器芯片進行仿真

2014-04-22 23:26:59

有關于乘法器的相關知識和代碼。最近看到別人做乘法器, 自己也想試一試,上網找到特權同學的乘法器的視頻講解,但是對于我等初學者,還是搞不懂。經過一天的分析和整理,終于明白了,想分享給那些和我一樣的菜鳥

2016-04-02 00:28:19

本帖最后由 eehome 于 2013-1-5 10:07 編輯

fpga中定點乘法器設計(中文)

2012-08-24 00:55:37

/devkits/HW-SPAR3A-SK-UNI-G.htm它有兩個模擬輸入和fpga,有20個乘法器但是我想要更多的輸入和更多的乘法器塊,是否能夠滿足這些功能的任何板?

2019-08-23 07:03:09

在數(shù)字化飛速發(fā)展的今天,人們對微處理器的性能要求也越來越高。作為衡量微處理器性能的主要標準,主頻和乘法器運行一次乘法的周期息息相關。因此,為了進一步提高微處理器性能,開發(fā)高速高精度的乘法器勢在必行

2019-09-03 08:31:04

我正在研究一種適用于Vedic Maths算法的乘法器。我想對傳統(tǒng)乘法器和vedic乘法器的時序延遲進行比較分析。我有spartan 3e和Xilinx 12.1時序分析器。請任何人都可以指導我

2019-07-04 06:36:45

變頻控制和乘法器的基本原理分別是什么?乘法器在變頻控制中有什么作用?

2021-04-13 06:40:36

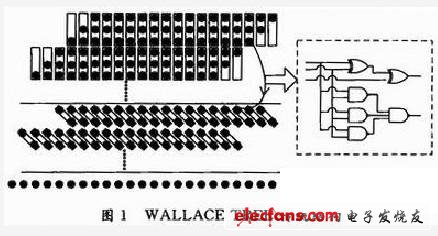

本文介紹了32 位浮點陣列乘法器的設計, 采用了改進的Booth 編碼, 和Wallace樹結構, 在減少部分積的同時, 使系統(tǒng)具有高速度, 低功耗的特點, 并且結構規(guī)則, 易于VLSI的實現(xiàn)。

2021-05-08 07:44:31

在數(shù)字信號處理中,乘法器是整個硬件電路時序的關鍵路徑。速度和面積的優(yōu)化是乘法器設計過程的兩個主要考慮因素。由于現(xiàn)代可編程邏輯芯片FPGA的集成度越來越高,及其相對于ASIC設計難度較低和產品設計

2019-09-03 07:16:34

模擬乘法器為何沒輸出信號我在仿真analog 的乘法器。我使用的是 Multisim 自帶的庫文件。器件用的 AD834。我畫好設計圖后,接上虛擬示波器。可是,信號發(fā)生器里有信號,乘法器后沒有。請問各位高人,我哪里畫錯了。還是,multisim自帶的庫文件就不行

2022-04-01 16:48:04

說明:求fpga乘法器,要求快的,不是一個一個的加,而是像乘法豎式一樣的,如:10111000111000 *1011111 =10111000111000*1011111

2012-08-16 14:08:36

請求大神分享一種改進的Wallace樹型乘法器的設計

2021-04-14 06:41:13

最近在做乘法器,我想問下用VHDL做軟乘法器,有點不懂軟乘法器,求大神帶!

2015-07-30 11:10:55

2017年國賽原件清單上有乘法器,用什么芯片做乘法器會比較好,求助大神。

2017-08-02 10:49:28

求浮點數(shù)乘除計算程序,求用硬件乘法器計算浮點數(shù)的程序

2015-11-03 22:32:47

硬件乘法器是怎么實現(xiàn)的

2023-09-22 06:53:57

一,乘法器硬件乘法器是一個通過內部總線與 CPU 相連的 16 位外圍模塊。MSP430 單片機可以在部改變 CPU 結構和指令的情況下增加功能,這種結構特別適用于對運算速度要求很嚴格的情況。硬件

2021-12-09 07:05:15

為了提高乘法器的綜合性能,從3個方面對乘法器進行了優(yōu)化設計。采用改進的Booth算法生成各個部分積,利用跳躍式Wallace樹結構進行部分積壓縮,通過改進的LING加法器對壓縮結果進

2009-04-17 09:35:20 27

27 AD834是美國ADI公司推出的寬頻寬、四象限、高性能的模擬乘法器.它工作穩(wěn)定,計算誤差小,并具有低失真和微功耗的特點,本文介紹了AD834模擬乘法器的主要特性、工作原理、應用考慮和

2009-04-27 16:36:57 86

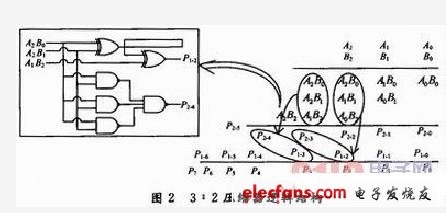

86 本文設計了適用于 SOC(System On Chip)的快速乘法器內核。通過增加一位符號位,可以支持24×24 無符號和有符號乘法。在乘法器的設計中,采用了改進的Booth 算法來減少部分積的數(shù)目

2009-09-21 10:40:42 20

20 模擬乘法器AD834的原理與應用:AD834是美國ADI公司推出的寬頻寬、四象限、高性能的模擬乘法器。它工作穩(wěn)定,計算誤差小,并具有低失真和微功耗的特點,本文介紹了AD834模擬乘法器

2009-09-29 10:49:21 183

183 對數(shù)字陣列乘法器的移位加算法、Pezaris 算法、Baugh-Wooley 算法的性能進行了分析,討論其各自的特點;指出進一步提高并行快速乘法器性能的研究重點。關鍵詞:陣列乘法器;

2009-12-14 09:28:16 41

41 設計了一個基于FPGA的單精度浮點數(shù)乘法器.設計中采用改進的帶偏移量的冗余Booth3算法和跳躍式Wallace樹型結構,并提出對Wallace樹產生的2個偽和采用部分相加的方式,提高了乘法器的運

2010-09-29 16:46:56 44

44 AD532是首款預調整的單芯片乘法器/除法器;無需任何外部調整電阻或輸出運算放大器,即可保證±1.0%的最大乘法誤差和±10 V的輸出電壓范圍。AD532經過內部調整,易于使用,為設計

2010-10-02 09:37:50 132

132

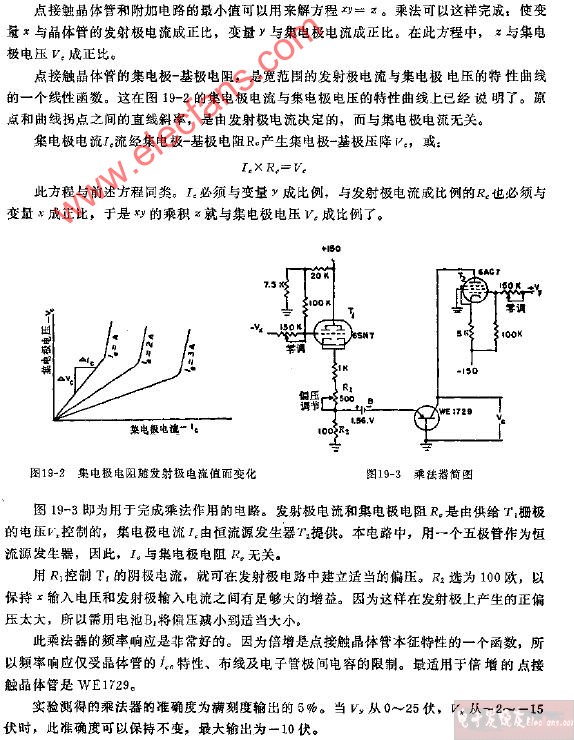

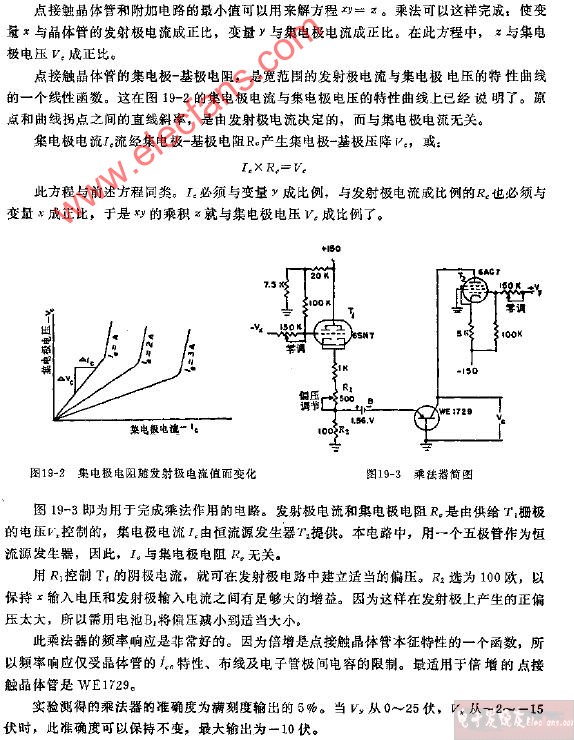

點接觸晶體管乘法器電路圖

2009-07-03 13:37:00 578

578

采用乘法器的可變環(huán)寬比較器電路圖

2009-07-25 11:36:29 587

587

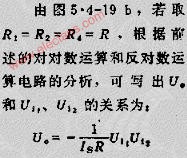

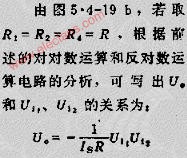

乘法器對數(shù)運算電路應用

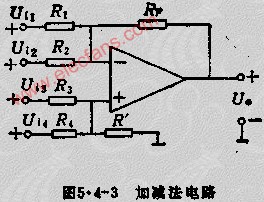

由對數(shù)電路實現(xiàn)乘法運算的數(shù)學原理是:UO=EXP(INU11+INU12)=U11+U12

圖5.4-19示出了滿足上式的乘法器的方框

2010-04-24 16:03:19 2273

2273

乘法器的基本概念

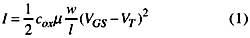

乘法器是一種完成兩個互不相關的模擬信號相乘作用的電子器件。理想乘法器的輸出特性方程可由下式表示:

UO

2010-05-18 14:03:59 13355

13355

1/4平方乘法器

這種乘法器是根據(jù)數(shù)學關系設計而成的,因此稱為1/4平方乘法電路,或稱1/4平方乘法器。其

2010-05-18 14:08:10 1777

1777

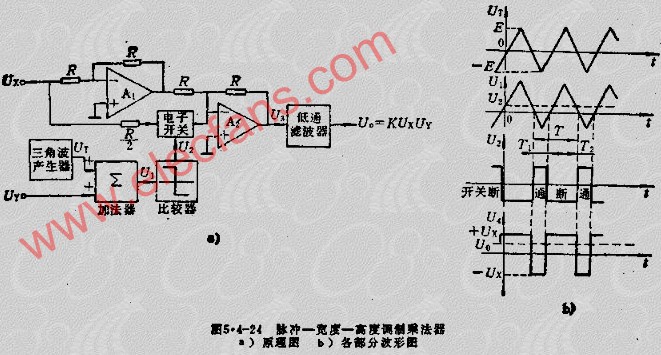

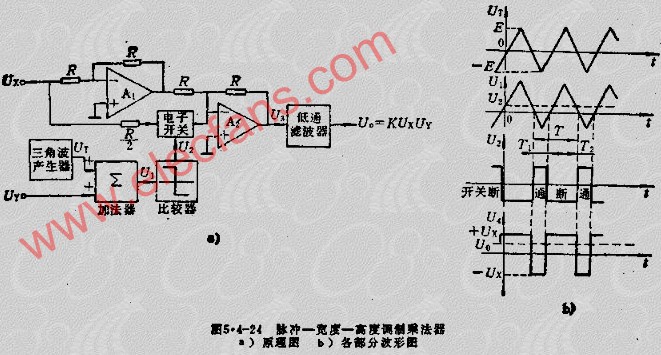

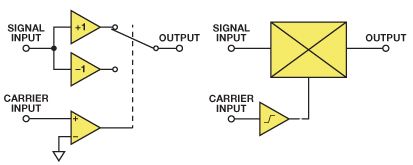

脈沖-寬度-高度調制乘法器

脈沖-寬度-高度調制乘法器雙稱為時間分割乘法器。這類乘法器電路原理圖如圖5.4-24A所示。圖中,三角波電壓UT和模擬輸入電壓UY

2010-05-18 14:23:53 1782

1782

變跨導乘法器的基本原理

圖5.4-25為變跨導乘法器原理圖。它利用V1、V2管的跨導GM正比于恒流源電流IO,而IO又受另一個輸入電壓控制,而實

2010-05-18 14:48:28 2947

2947

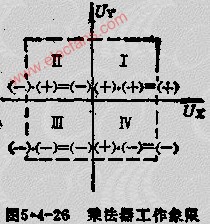

N象限變跨導乘法器

為了克服圖5.4-25所示的乘法器的缺點,在基電路的基礎上,采用了雙重差分放大式結構,設計出如圖5.4-27所示的N象限變跨導乘法器。

2010-05-18 15:24:08 1545

1545

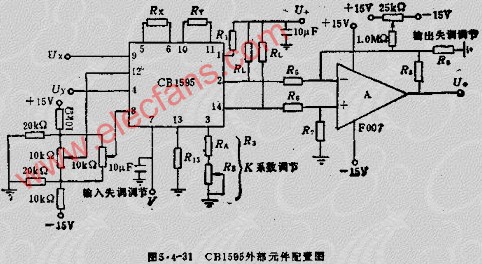

可變跨導乘法器的品種

模擬乘法器就基單片結構的形式來說,基本上分為兩大類,即用于處理交流小信號的如圖5.4-27所示的基本電路,以及適用于模擬運算

2010-05-18 15:51:40 1736

1736

變跨導乘法器

這種乘法器現(xiàn)在已經成為一種工業(yè)上的標準方法,是應用極為廣泛的優(yōu)質乘法器。

2010-05-18 16:00:55 1087

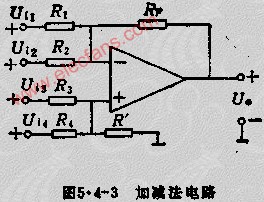

1087 乘法器在模擬運算電路中的應用

相乘運算

2010-05-18 16:48:06 1879

1879 乘法器在通信電路中的應用

普通振幅調制

2010-05-18 17:46:47 1268

1268 如圖所示為有負載驅動能力的乘法電路。由乘法器MPY600和高速緩沖器OPA633組成具有負載驅動能力的乘法器電路

2011-01-29 19:01:33 1372

1372

實驗目的 1、熟悉Xilinx的ISE 軟件的使用和設計流程; 2、掌握Modelsim仿真軟件的使用方法; 3、用乘法運算符實現(xiàn)一個16*16 乘法器模塊; 4、用IP核實現(xiàn)一個16*16 乘法器模塊; 5、用例化語

2011-05-20 17:00:14 66

66 AD834具有的800MHz的可用帶寬是此前所有 模擬乘法器 所無法相比的。在推出AD834之前,ADI公司已經有了大約20年設計模擬乘法器的歷史,也推出過其他的模擬乘法器產品,如:AD734四象限模

2011-07-18 15:33:21 242

242 定點乘法器設計(中文) 運算符: + 對其兩邊的數(shù)據(jù)作加法操作; A + B - 從左邊的數(shù)據(jù)中減去右邊的數(shù)據(jù); A - B - 對跟在其后的數(shù)據(jù)作取補操作,即用0減去跟在其后的數(shù)據(jù); - B * 對其兩邊的

2012-01-17 10:39:01 32

32 設計了一種支持IEEE754浮點標準的32位高速流水線結構浮點乘法器。該乘法器采用新型的基4布思算法,改進的4:2壓縮結構和部分積求和電路,完成Carry Save形式的部分積壓縮,再由Carry Lo

2012-02-29 11:20:45 3269

3269 本文提出了一種高頻四象限電流乘法器。該乘法器電路結構對稱。提出的乘法器電路工作在±1.18 V的電源電壓下。由于從輸人端到地的低寄生電容,該電路可以工作在高頻條件下,實驗

2012-03-07 10:52:52 3516

3516

這個模擬乘法器原理圖可作為分壓器和乘數(shù)。該電路是由四個部分組成。晶體管匹配確定乘法電路的精確度。

2012-03-13 16:58:36 22787

22787

低壓高頻CMOS電流乘法器原理圖通過調節(jié)跨導參數(shù)k和參數(shù)a,來調節(jié)乘法器的增益。參數(shù)k和MOS管的尺寸直接相關。

2012-03-14 17:25:47 2364

2364

模擬乘法器,大家自己有需要的趕緊下載吧,機不可失

2015-10-27 14:10:20 0

0 8乘8乘法器verilog源代碼,有需要的下來看看

2016-05-23 18:21:16 24

24 基于AD835的乘法器原理圖及PCB設計

2016-06-08 16:46:10 0

0 華清遠見FPGA代碼-FPGA片上硬件乘法器的使用

2016-10-27 18:07:54 10

10 一個自己寫的八位數(shù)的乘法器

2016-12-01 15:45:23 15

15 高速雙域乘法器設計及其應用_鄭朝霞

2017-01-07 18:39:17 0

0 模擬乘法器作用及電路

2017-10-23 09:22:40 28

28 乘法器,求模運算部分利用Barrett約減運算,用硬件描述語言進行FPGA設計與實現(xiàn),避免了除法運算。對于192位的操作數(shù),完成Barrett模乘需要約186個時鐘周期,計算速率可以達到269.17 Mb/s。

2017-11-08 15:18:19 32

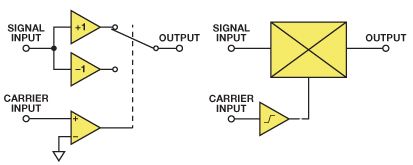

32 雖然許多有關調制的描述都將其描繪成一種乘法過程,但實際情況更為復雜。 首先,為清晰起見,若信號Acos(t)和未調制的載波cos(t)施加于理想乘法器的兩路輸入,則我們將得到一個調制器。這是因為兩個

2017-11-15 14:45:18 15

15 設計了一種新穎的3232位高速流水線乘法器結構.該結構所采用的新型Radix-16 Booth算法吸取了冗余Booth編碼與改進Booth編碼的優(yōu)點,能簡單、快速地產生復雜倍數(shù).設計完成的乘法器

2018-03-15 13:34:00 6

6 硬件乘法器是現(xiàn)代計算機中必不可少的一部分,其基礎是加法器結構。

2018-05-11 10:52:45 8533

8533 在做項目的過程中,經常遇到乘法計算,乘法器的設計就尤為重要。乘法器決定了最終電路功能能否實現(xiàn),資源使用量多少以及時序性能優(yōu)劣等。

2018-07-04 09:41:45 8885

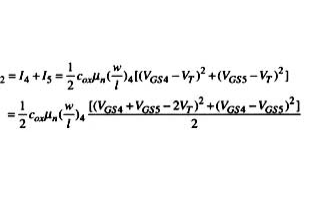

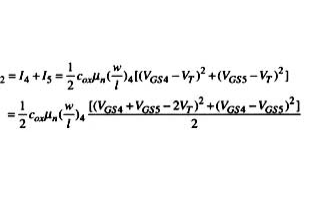

8885 在集成電路系統(tǒng)中,模擬乘法器在信號調制解調、鑒相、頻率轉換、自動增益控制和功率因數(shù)校正控制等許多方面有著非常廣泛的應用。實現(xiàn)模擬乘法器的方法有很多,按采用的工藝不同,可以分為三極管乘法器和CMOS乘法器。

2019-05-31 08:20:00 2618

2618

在微處理器芯片中,乘法器是進行數(shù)字信號處理的核心,同時也是微處理器中進行數(shù)據(jù)處理的關鍵部件。乘法器完成一次操作的周期基本上決定了微處理器的主頻。乘法器的速度和面積優(yōu)化對于整個CPU的性能來說是非常重要的。為了加快乘法器的執(zhí)行速度,減少乘法器的面積,有必要對乘法器的算法、結構及電路的具體實現(xiàn)做深入的研究。

2019-05-15 08:27:00 14914

14914

本文在設計實現(xiàn)乘法器時,采用了4-2和5-2混合壓縮器對部分積進行壓縮,減少了乘法器的延時和資源占 用率;經XilinxISE和QuartusII兩種集成開發(fā)環(huán)境下的綜合仿真測試

2018-12-19 13:30:25 10461

10461

乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數(shù)相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機算數(shù)技術來實現(xiàn)。

2019-11-28 07:06:00 3062

3062 作者:貓叔 FPGA中乘法器是很稀缺的資源,但也是我們做算法必不可少的資源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我們可以通過調IP Core的方式或者

2020-09-27 15:12:52 8952

8952

乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數(shù)相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機算數(shù)技術來實現(xiàn)。乘法器不僅作為

2021-02-18 15:08:01 24395

24395

模擬乘法器是對兩個模擬信號(電壓或電流)實現(xiàn)相乘功能的的有源非線性器件。

2021-02-18 16:37:28 8665

8665 模擬乘法器是輸出電壓與兩路輸入電壓之積成正比的有源網絡。理想的乘法器具有無限大的輸入阻抗及零輸出阻抗,其標尺因子不隨頻率變化并且與電壓的大小無關。如果理想的乘法器的任意一路輸入電壓為零時,則輸出電壓就為零。換句話說,它的失調、漂移和噪聲電壓均為零。

2021-02-18 17:21:19 5656

5656

MT-079:模擬乘法器

2021-03-21 02:50:06 12

12 在集成電路系統(tǒng)中,模擬乘法器在信號調制解調、鑒相、頻率轉換、自動增益控制和功率因數(shù)校正控制等許多方面有著非常廣泛的應用。實現(xiàn)模擬乘法器的方法有很多,按采用的工藝不同,可以分為三極管乘法器和CMOS乘法器。

2021-03-23 09:40:19 3930

3930

MT-079:模擬乘法器

2021-04-27 10:15:32 10

10 本設計以16位乘法器的設計為基礎,從而掌握現(xiàn)代大規(guī)模集成數(shù)字邏輯電路的應用設計方法,進一步掌握電子儀器的正確使用方法,以及掌握利用計算機進行電子設計自動化(EDA)的基本方法。由16位加法器構成

2021-06-01 09:43:56 26

26 我們使用調制器而不是乘法器有幾個原因。乘法器的兩個端口都是線性的,因此載波輸入上的任何噪聲或調制都會使信號輸入成倍并降低輸出,而調制器載波輸入的幅度變化大多可以忽略不計。二階機制會導致載波輸入端的幅度噪聲影響輸出,但在最好的調制器中,這些噪聲被最小化,這里不討論。

2023-01-30 14:26:35 2103

2103

本文是本系列的第二篇,本文主要介紹FPGA常用運算模塊-加減法器和乘法器,xilinx提供了相關的IP以便于用戶進行開發(fā)使用。

2023-05-22 16:13:57 2625

2625

本文是本系列的第五篇,本文主要介紹FPGA常用運算模塊-復數(shù)乘法器,xilinx提供了相關的IP以便于用戶進行開發(fā)使用。

2023-05-22 16:23:28 1204

1204

電子發(fā)燒友App

電子發(fā)燒友App

評論