FPGA的IRIG-B編碼器實(shí)現(xiàn)

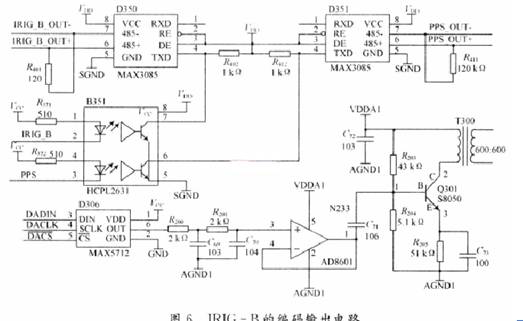

我國(guó)靶場(chǎng)測(cè)量、工業(yè)控制、電力系統(tǒng)測(cè)量與保護(hù)、計(jì)算、通信、氣象等測(cè)試設(shè)備均采用國(guó)際標(biāo)準(zhǔn)IRIG-B格式的時(shí)間碼(簡(jiǎn)稱B碼)作為時(shí)間同步標(biāo)準(zhǔn)。B

2010-03-29 09:58:13 2221

2221

本文介紹了FPGA在實(shí)現(xiàn)高清低碼流視頻編碼中的作用以及如何具體實(shí)現(xiàn)。目前現(xiàn)狀是高清視頻720p的碼流一般在2Mbps以上,1080p的碼流在4Mbps以上,要大幅度降低碼流,需要從幾個(gè)方面考慮。

2013-09-23 13:41:15 1986

1986 Netflix提出了一種基于感知視頻編碼優(yōu)化框架,在非峰值流時(shí)間期間,將此編碼系統(tǒng)應(yīng)用于AVC-High和VP9數(shù)據(jù)流,提高了用戶的視頻質(zhì)量的同時(shí)并節(jié)省了帶寬。

2018-03-19 10:37:30 9292

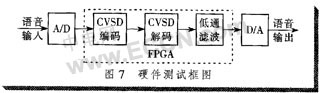

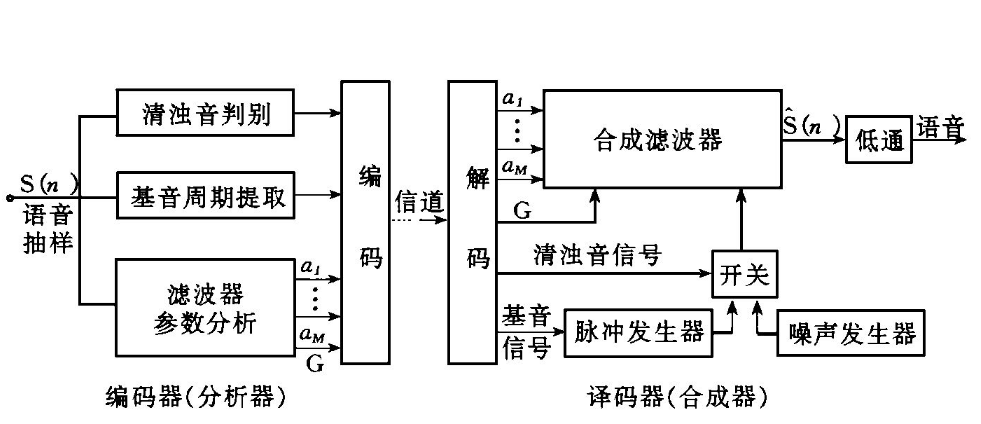

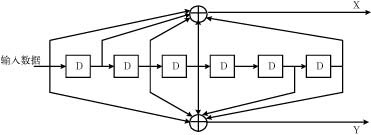

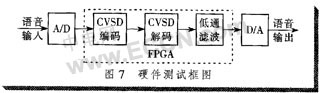

9292 FPGA和Nios_軟核的語(yǔ)音識(shí)別系統(tǒng)的研究引言語(yǔ)音識(shí)別的過程是一個(gè)模式匹配的過程 在這個(gè)過程中,首先根據(jù)說話人的語(yǔ)音特點(diǎn)建立語(yǔ)音模型,對(duì)輸入的語(yǔ)音信號(hào)進(jìn)行分析,并提取所需的語(yǔ)音特征,在此基礎(chǔ)上建立

2012-08-11 11:47:15

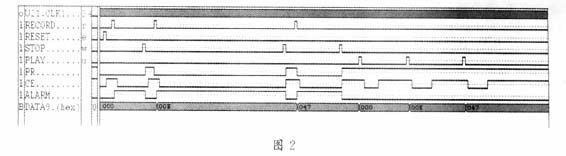

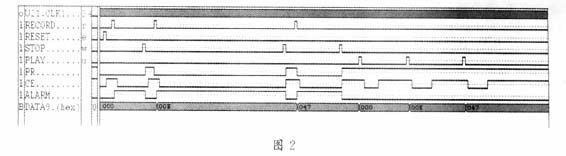

FPGA在語(yǔ)音存儲(chǔ)與回放系統(tǒng)中的應(yīng)用是什么

2021-05-06 07:13:11

以及最新的DSP系統(tǒng)工具的概況;接著主要介紹了計(jì)算機(jī)算法的概念、理論、有限字長(zhǎng)效用、FIR和IIR濾波器的實(shí)現(xiàn)、多速率和自適應(yīng)信號(hào)處理的FPGA實(shí)現(xiàn);最后,介紹了System Genrerator

2009-07-21 09:22:42

最近,需要使用fpga實(shí)現(xiàn)iec-61850-9-2報(bào)文編碼,設(shè)計(jì)中涉及到的 字段非常多,以至于邏輯特別復(fù)雜,占用資源太多,設(shè)計(jì)的頻率上不去。有沒有哪位同道做過fpga報(bào)文編碼類的設(shè)計(jì),請(qǐng)不吝賜教。

2013-11-12 23:20:19

語(yǔ)音識(shí)別技術(shù)的最重大突破是隱含馬爾科夫模型Hidden Markov Model的應(yīng)用。從Baum提出相關(guān)數(shù)學(xué)推理,經(jīng)過Labiner等人的研究,卡內(nèi)基梅隆大學(xué)的李開復(fù)最終實(shí)現(xiàn)了第一個(gè)基于隱馬爾科夫模型的大詞匯量語(yǔ)音識(shí)別系統(tǒng)Sphinx。此后嚴(yán)格來說語(yǔ)音識(shí)別技術(shù)并沒有脫離HMM框架。

2019-10-08 14:29:52

請(qǐng)問有人接觸或設(shè)計(jì)過這個(gè)么?對(duì)于語(yǔ)音編碼打包能不能給點(diǎn)意見,其他方面的也行,先謝謝了

2020-04-28 03:31:50

方法語(yǔ)音編碼方案的選取對(duì)移動(dòng)通信系統(tǒng)的通話質(zhì)量、信道容量等有重要影響。本文討論了TD-SCDMA系統(tǒng)中AMR語(yǔ)音編碼的自適應(yīng)機(jī)制,同時(shí)分析了AMR中代數(shù)碼本線性預(yù)測(cè)(ACELP)算法及實(shí)現(xiàn)過程。該

2009-07-29 08:30:15

以及最新的DSP系統(tǒng)工具的概況;接著主要介紹了計(jì)算機(jī)算法的概念、理論、有限字長(zhǎng)效用、FIR和IIR濾波器的實(shí)現(xiàn)、多速率和自適應(yīng)信號(hào)處理的FPGA實(shí)現(xiàn);最后,介紹了System Genrerator

2009-07-21 09:20:11

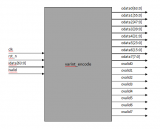

介紹FPGA開發(fā)板上組合邏輯電路的實(shí)現(xiàn),這些實(shí)例包括在數(shù)字邏輯設(shè)計(jì)課程中所熟知的部分中規(guī)模集成電路:優(yōu)先編碼器、多路復(fù)用器以及加法器,最后還將介紹算術(shù)邏輯單元ALU的實(shí)現(xiàn)。優(yōu)先編碼器實(shí)驗(yàn)原理在數(shù)字系統(tǒng)中

2022-08-04 17:39:32

我想知道基于FPGA出租車計(jì)價(jià)系統(tǒng)實(shí)現(xiàn)的技術(shù)框架是什么?

2016-04-26 10:36:46

基于FPGA的語(yǔ)音信號(hào)采集與播放系統(tǒng)設(shè)計(jì)原理圖怎么畫,求大牛幫助啊 。

2015-04-22 16:16:00

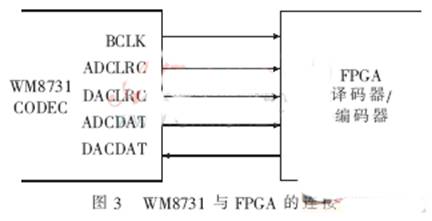

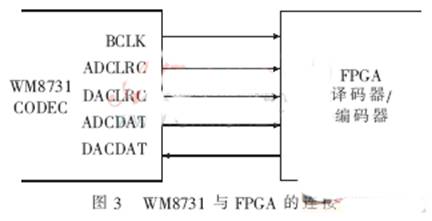

)EP2C35F672C6NK為平臺(tái),結(jié)合音頻編/解碼芯片WM8731實(shí)現(xiàn)語(yǔ)音錄制與回放。該FPGA芯片具有豐富的片內(nèi)資源,大量的邏輯宏單元和多個(gè)硬件乘法器,大量的自定義I/O接口,此外還有4個(gè)鎖相環(huán),為系統(tǒng)提供實(shí)時(shí)

2019-10-22 07:17:15

26期摘 要:對(duì)于采用信道編碼技術(shù)進(jìn)行糾錯(cuò)的系統(tǒng),只能糾正隨機(jī)錯(cuò)誤,無(wú)法解決突發(fā)錯(cuò)誤的問題。詳細(xì)闡述了一種基于漢明碼的交織編碼技術(shù),并以FPGA為平臺(tái)進(jìn)行了實(shí)現(xiàn)與仿真。仿真結(jié)果表明該交織編碼技術(shù)可以

2018-05-11 14:09:54

基于DSP的漢字語(yǔ)音識(shí)別系統(tǒng)如何實(shí)現(xiàn)

2021-03-12 06:33:15

本實(shí)驗(yàn)采用單片機(jī)和FPGA來實(shí)現(xiàn)多點(diǎn)有線語(yǔ)音通信系統(tǒng)。其中單片機(jī)通過編寫串口通信協(xié)議來實(shí)現(xiàn)對(duì)語(yǔ)音數(shù)字信號(hào)以及文字信息的點(diǎn)對(duì)點(diǎn)傳送。本實(shí)驗(yàn)實(shí)現(xiàn)的是異步串行通信,根據(jù)RS232協(xié)議,使用串行傳輸線通過

2011-03-08 16:05:01

語(yǔ)音編碼技術(shù)在當(dāng)今數(shù)字通信尤其在無(wú)線系統(tǒng)中發(fā)揮著越來越重要的作用。利用語(yǔ)音編碼技術(shù)可有效降低信息存儲(chǔ)量、提高信道利用率。混合激勵(lì)線性預(yù)測(cè)(MELP)語(yǔ)音編碼算法能在較低碼率下提供較高的語(yǔ)音質(zhì)量、自然度和清晰度,已成為美國(guó)國(guó)防部新的2.4 Kb/s的語(yǔ)音編碼標(biāo)準(zhǔn)。

2019-08-19 07:34:48

如何實(shí)現(xiàn)高響度語(yǔ)音電路設(shè)計(jì)?語(yǔ)音電路系統(tǒng)是如何構(gòu)成的?語(yǔ)音電路特性有哪些?

2021-04-12 07:04:22

PCM編碼原理與規(guī)則是什么?如何利用FPGA編程技術(shù)實(shí)現(xiàn)PCM編碼原理?機(jī)場(chǎng)監(jiān)視監(jiān)控網(wǎng)絡(luò)中低速接入應(yīng)用

2021-04-15 06:38:46

本文基于AMBE-2000,設(shè)計(jì)并實(shí)現(xiàn)了一種基于AMBE-2000的語(yǔ)音系統(tǒng)。該系統(tǒng)具有設(shè)計(jì)簡(jiǎn)便、語(yǔ)音編碼速率可變、音質(zhì)優(yōu)、接口靈活、工作電壓低、功耗小等諸多優(yōu)點(diǎn),可廣泛應(yīng)用于衛(wèi)星通信、短波、微波通信和保密通信等場(chǎng)合,具有很高的實(shí)用價(jià)值。

2021-06-02 06:33:40

本文采用FPGA實(shí)現(xiàn)ADPCM(Adaptive Differential Pulse CodeModulation,自適應(yīng)差分脈沖編碼調(diào)制)編解碼器設(shè)計(jì),對(duì)語(yǔ)音信息進(jìn)行壓縮存儲(chǔ)。從而使存儲(chǔ)信息量增大了一倍。

2021-05-17 06:26:37

本文采用通用法實(shí)現(xiàn)MELP聲碼器算法,選擇TI公司的TMS320VC5416 DSP芯片作為主處理器,完成聲碼器的主要功能。

2021-06-07 07:02:50

怎么實(shí)現(xiàn)ZigBee語(yǔ)音圖像無(wú)線監(jiān)控系統(tǒng)的設(shè)計(jì)?

2021-06-04 06:32:23

怎么實(shí)現(xiàn)ZigBee技術(shù)語(yǔ)音圖像無(wú)線監(jiān)控系統(tǒng)的設(shè)計(jì)?

2021-05-11 06:21:10

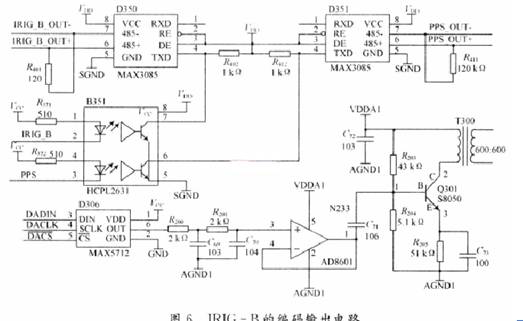

本文介紹一種基于FPGA并執(zhí)行IRIG-B標(biāo)準(zhǔn)的AC/DC編碼技術(shù),與基于MCU或者DSP和數(shù)字邏輯電路實(shí)現(xiàn)的編碼方法相比,該技術(shù)可以大大降低系統(tǒng)的設(shè)計(jì)難度,降低成本,提高B碼的精確性和系統(tǒng)靈活性。

2021-04-29 06:56:12

如何實(shí)現(xiàn)基于語(yǔ)音控制的智能家居控制系統(tǒng)的設(shè)計(jì)?

2022-01-25 07:50:09

IJF編碼是什么原理?如何實(shí)現(xiàn)IJF編碼?采用FPGA和集成器件來實(shí)現(xiàn)IJF編碼

2021-04-13 06:56:04

車載導(dǎo)航人機(jī)語(yǔ)音交互系統(tǒng)的實(shí)現(xiàn)引言 語(yǔ)音作為自然的人機(jī)接口,可以使車載導(dǎo)航系統(tǒng)實(shí)現(xiàn)更安全、更人性化的操作。通過國(guó)內(nèi)外車載導(dǎo)航系統(tǒng)的功能對(duì)比可知,支持語(yǔ)音交互是車載導(dǎo)航系統(tǒng)的一個(gè)發(fā)展趨勢(shì)。另外

2008-08-15 21:27:56

的設(shè)計(jì)中,根據(jù)人機(jī)交互的需求,設(shè)計(jì)語(yǔ)音導(dǎo)航系統(tǒng)的硬件框架如圖 1所示。語(yǔ)音導(dǎo)航系統(tǒng)和用戶之間的人機(jī)交互接口由觸摸屏、按鈕、話筒、顯示屏和擴(kuò)音器等五個(gè)交互設(shè)備組成。該硬件框架可實(shí)現(xiàn)常規(guī)的手動(dòng)交互方式,也可以

2019-05-07 07:00:21

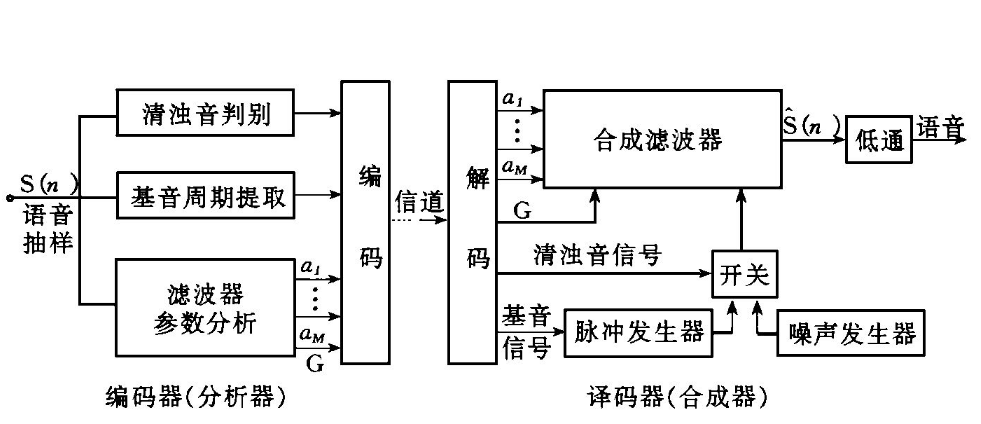

比較流行的大規(guī)模集成電路Verilog開發(fā)語(yǔ)言。系統(tǒng)軟件功能實(shí)現(xiàn)了A/D控制模塊、語(yǔ)音編碼控制模塊、并串轉(zhuǎn)換控制模塊、串并轉(zhuǎn)換控制模塊、D/A控制模塊、語(yǔ)音解碼控制模塊和反向數(shù)據(jù)的收發(fā)控制模塊。

2019-07-17 07:43:08

出A、B信號(hào)的上升沿和下降沿。輸入信號(hào)與其延時(shí)信號(hào)異或后,就可得到倍頻信號(hào)。2 接口電路的FPGA總體方案及設(shè)計(jì)實(shí)現(xiàn)光電編碼器的可靠性與精度直接決定了控制系統(tǒng)的可靠性與控制精度。控制系統(tǒng)精度不會(huì)高于

2019-06-10 05:00:08

800Mbps準(zhǔn)循環(huán)LDPC碼編碼器的FPGA實(shí)現(xiàn)CCSDS星載圖像壓縮模塊的FPGA設(shè)計(jì)與實(shí)現(xiàn)FPGA和Nios_軟核的語(yǔ)音識(shí)別系統(tǒng)的研究RC4加密算法的FPGA設(shè)計(jì)與實(shí)現(xiàn)多FPGA系統(tǒng)中自定義

2012-02-02 17:26:14

介紹了G.729語(yǔ)音編碼器算法和定點(diǎn)數(shù)字信號(hào)處理芯片TMS320VC549,重點(diǎn)討論了低速率語(yǔ)音編碼器在TMS320VC549上實(shí)時(shí)實(shí)現(xiàn)過程中軟、硬件設(shè)計(jì)中的關(guān)鍵技術(shù)。采用了定點(diǎn)數(shù)字信號(hào)處理器

2009-02-19 23:37:13 26

26 在電子耳蝸設(shè)計(jì)中,語(yǔ)音信號(hào)的實(shí)時(shí)有效編碼及傳輸是其中的關(guān)鍵技術(shù)。本文根據(jù)耳蝸的空間位置編碼原理,設(shè)計(jì)了一套電子耳蝸語(yǔ)音處理軟硬件系統(tǒng),以數(shù)字信號(hào)處理器(Dig

2009-07-16 08:26:58 18

18 語(yǔ)音編碼方案的選取對(duì)移動(dòng)通信系統(tǒng)的通話質(zhì)量、信道容量等有重要影響。本文討論了TD-SCDMA系統(tǒng)中AMR語(yǔ)音編碼的自適應(yīng)機(jī)制,同時(shí)分析了AMR中代數(shù)碼本線性預(yù)測(cè)(ACELP)算法及實(shí)現(xiàn)

2009-07-29 08:27:38 18

18 論文對(duì)MELP 編解碼算法的原理進(jìn)行了簡(jiǎn)要分析,討論了如何在定點(diǎn)DSP 芯片TMS320VC5416 上實(shí)現(xiàn)該算法,并研究了其關(guān)鍵技術(shù),最后對(duì)測(cè)試結(jié)果進(jìn)行了分析。關(guān)鍵詞:MELP;語(yǔ)音編碼;

2009-08-06 08:46:47 20

20 Schur 遞歸算法是GSM 全速率語(yǔ)音編碼算法中計(jì)算短期濾波參數(shù)的一個(gè)關(guān)鍵部分。由于它是一個(gè)典型的雙循環(huán)結(jié)構(gòu),所以在算法的FPGA 實(shí)現(xiàn)中也具有代表意義,本文對(duì)Schur 遞歸算法的特

2009-09-26 08:34:11 17

17 通過使用改進(jìn)的游程編碼算法!多重查找表設(shè)計(jì)及預(yù)存儲(chǔ)命令字等技術(shù)"實(shí)現(xiàn)了一種適用于廣泛硬件平臺(tái)的嵌入式TTS漢字語(yǔ)音系統(tǒng)"其可發(fā)音字符涵蓋了GB2312漢字編碼字符集

2010-07-02 15:07:15 28

28 介紹了一種使用射頻技術(shù)的無(wú)線收發(fā)模塊的編解碼應(yīng)用設(shè)計(jì),自主調(diào)制與解調(diào),該方式電路連接簡(jiǎn)單,傳輸距離遠(yuǎn),且不受方向性約束。選用未經(jīng)編碼的無(wú)線模塊,通過FPGA實(shí)現(xiàn)編碼

2010-07-21 17:40:24 27

27 本文針對(duì)A律13折線法的算法特點(diǎn),提出一種并行數(shù)據(jù)處理算法,實(shí)現(xiàn)了編碼的流水線操作。運(yùn)用VHDL語(yǔ)言將其在FPGA中實(shí)現(xiàn),借助quartus II6.0平臺(tái)進(jìn)行驗(yàn)證,并對(duì)驗(yàn)證結(jié)果進(jìn)行分析,評(píng)估了系統(tǒng)

2010-07-28 17:32:50 21

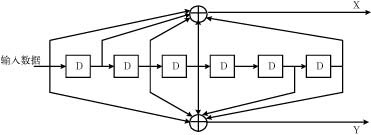

21 本文介紹了可變參數(shù)交織編碼器FPGA實(shí)現(xiàn)的圖形設(shè)計(jì)過程,給出了完整的設(shè)計(jì)思路和設(shè)計(jì)電路,并對(duì)設(shè)計(jì)進(jìn)行了仿真實(shí)驗(yàn),從仿真圖中可以清楚的看出不同交織深度下的性能指標(biāo)

2010-07-28 17:59:27 10

10 本文重點(diǎn)研究了AVS-P2熵編碼器的算法、結(jié)構(gòu)以及利用FPGA實(shí)現(xiàn)的若干關(guān)鍵問題,給出了詳細(xì)的塊變換系數(shù)熵編碼器硬件結(jié)構(gòu),并通過了仿真驗(yàn)證。實(shí)現(xiàn)中提出了一種新的2D-VLC碼表存儲(chǔ)

2010-08-06 16:37:38 24

24 討論了低碼率語(yǔ)音編碼MELP的編解碼過程,有效降低了語(yǔ)音編碼碼率并能使說話者個(gè)人語(yǔ)音特征減弱,特別適合需要弱化說話者語(yǔ)音特點(diǎn)的場(chǎng)合。給出了其FPGA的硬件實(shí)現(xiàn)框圖,據(jù)此

2010-12-01 16:57:14 33

33 介紹了一種采用FPGA硬件實(shí)現(xiàn)ADPCM算法的方法,并基于此算法對(duì)預(yù)先采集的各種報(bào)警語(yǔ)音進(jìn)行壓縮編碼并存儲(chǔ)。在遇到危險(xiǎn)時(shí),由單片機(jī)做出危險(xiǎn)判斷,并自動(dòng)選擇播放相應(yīng)的報(bào)警

2010-12-11 15:59:50 28

28 為了滿足數(shù)字通信及其他商業(yè)應(yīng)用的需求,語(yǔ)音壓縮編碼技術(shù)得到迅速發(fā)展。近年來主流的低速率語(yǔ)音編碼方案主要基于LPC-10,混合激勵(lì)線性預(yù)測(cè)(MELP),多帶激勵(lì)編碼(MBE),正弦

2011-01-04 10:20:37 16

16 【摘 要】 簡(jiǎn)述了ISD語(yǔ)音芯片,重點(diǎn)介紹了基于現(xiàn)場(chǎng)可編程門陣列(FPGA)開發(fā)設(shè)計(jì)ISD語(yǔ)音芯片的實(shí)現(xiàn)方法。 關(guān)鍵詞:FPGA,

2009-05-11 19:57:22 1252

1252

3G系統(tǒng)采用了什么語(yǔ)音編碼技術(shù)?

語(yǔ)音編碼包括波形編碼和聲源編碼兩種類型:波形編碼以再現(xiàn)波形為目的,利用波形相關(guān)性采用

2009-06-15 09:48:57 2274

2274 摘要: 在簡(jiǎn)單介紹算術(shù)編碼和自適應(yīng)算術(shù)編碼的基礎(chǔ)上,介紹了利用FPGA器件并通過VHDL語(yǔ)言描述實(shí)現(xiàn)自適應(yīng)算術(shù)編碼的過程。整個(gè)編碼系統(tǒng)在LTERA公司的MAX+plus Ⅱ軟

2009-06-20 13:40:24 1026

1026

摘 要:本文介紹了串型級(jí)聯(lián)編碼的原理,以及它在數(shù)字電視地面?zhèn)鬏?b class="flag-6" style="color: red">系統(tǒng)中的應(yīng)用,通過FPGA設(shè)計(jì)電路實(shí)現(xiàn)編碼過程,最后說明串型級(jí)聯(lián)編碼的應(yīng)用優(yōu)越性。

2009-06-20 13:49:18 532

532

基于FPGA的32Kbit/s CVSD語(yǔ)音編解碼器的實(shí)現(xiàn)

64 Kbit/s的A律或μ律的對(duì)數(shù)壓擴(kuò)PCM編碼在大容量的光纖通信系統(tǒng)和數(shù)字微波系統(tǒng)中已得到廣泛應(yīng)用,但由于占用較大的傳輸帶寬

2010-01-12 09:52:15 729

729

采用DSP芯片的MELP聲碼器的算法設(shè)計(jì)方案

摘要:論文對(duì)MELP編解碼算法的原理進(jìn)行了簡(jiǎn)要分析,討論了如何在定點(diǎn)DSP芯片MS320VC5416上實(shí)現(xiàn)該算法,

2010-03-06 14:20:11 1207

1207

利用語(yǔ)音編碼技術(shù)可有效降低信息存儲(chǔ)量、提高信道利用率。混合激勵(lì)線性預(yù)測(cè)(MELP)語(yǔ)音編碼算法能在較低碼率下提供較高的語(yǔ)音質(zhì)量、自然度和清晰度,已成為美國(guó)國(guó)防部新的2.

2010-06-03 09:07:27 1203

1203

1 前言

TI公司新近推出的語(yǔ)音合成芯片MSP50C30并采和MELP語(yǔ)音壓縮算法,通過外接64M位存儲(chǔ)器對(duì)語(yǔ)音信號(hào)進(jìn)行了壓縮存儲(chǔ)和合成。經(jīng)過這樣處理合成后的語(yǔ)音音質(zhì)良好,放

2010-09-03 17:32:39 1001

1001

提出了一種基于FPGA并利用Verilog HDL實(shí)現(xiàn)的CMI編碼設(shè)計(jì)方法。研究了CMI碼型的編碼特點(diǎn),提出了利用Altera公司CycloneⅡ系列EP2C5Q型號(hào)FPGA完成CMI編碼功能的方案。在系統(tǒng)程序設(shè)計(jì)中,首先產(chǎn)生m序列,然后程序再對(duì)m序列進(jìn)行CMI碼型變換。在CMI碼型變換過程中

2011-01-15 15:44:04 67

67 設(shè)計(jì)了一種新型的中速率混合 語(yǔ)音壓縮編碼 系統(tǒng)。該系統(tǒng)把語(yǔ)音分割成基帶(013~1 kHz) 和高頻部分(1~314 kHz) 。對(duì)于重要的基帶信號(hào),采用高質(zhì)量的4 bit/ 樣點(diǎn)的ADPCM 技術(shù);對(duì)于相對(duì)次要的

2011-06-01 15:41:09 37

37 本方案采用FPGA和集成器件來實(shí)現(xiàn)IJF編碼和IJF-OQPSK調(diào)制具有高度集成化、配置靈活、性能穩(wěn)定、易于實(shí)現(xiàn)的特點(diǎn),由于IJF編碼有很多性能更好的變形,只需在此基礎(chǔ)修改ROM中的波形系數(shù)

2011-08-11 10:14:41 1382

1382

研究了能夠同時(shí)對(duì)多路 光電編碼器 脈沖信號(hào)進(jìn)行細(xì)分、計(jì)數(shù)以及傳輸?shù)臄?shù)據(jù)采集處理系統(tǒng)。提出了以高度集成的FPGA芯片為核心的設(shè)計(jì)方式,實(shí)現(xiàn)6路光電編碼器信號(hào)的同步實(shí)時(shí)處理。坐

2011-08-18 16:33:15 90

90 本文提出了一種用FPGA實(shí)現(xiàn)糾錯(cuò)編碼的設(shè)計(jì)思想,并以Altera MAX+PluslI為硬件開發(fā)平臺(tái)。利用FPGA編程的特點(diǎn),用軟件編程方法,很好的解決了糾錯(cuò)編碼中存在的碼速變換和實(shí)時(shí)性問題,實(shí)現(xiàn)

2011-11-10 17:10:59 61

61 為實(shí)現(xiàn)某專用接口裝置的接口功能檢測(cè),文中詳細(xì)地介紹了一種34位串行碼的編碼方式,并基于FPGA芯片設(shè)計(jì)了該類型編碼的接收、發(fā)送電路。重點(diǎn)分析了電路各模塊的設(shè)計(jì)思路。電路采

2012-06-18 12:37:09 41

41 基于MELP的水下實(shí)時(shí)語(yǔ)音通信機(jī)的研究與實(shí)現(xiàn)

2013-09-23 17:47:53 24

24 800Mbps準(zhǔn)循環(huán)LDPC碼編碼器的FPGA實(shí)現(xiàn)

2016-05-09 10:59:26 37

37 FPGA和Nios_軟核的語(yǔ)音識(shí)別系統(tǒng)的研究。

2016-05-10 10:46:40 20

20 FPGA和Si4463的跳頻語(yǔ)音通信系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2017-08-31 11:05:53 15

15 語(yǔ)音信號(hào)去噪和編碼系統(tǒng)設(shè)計(jì),DSP嵌入式系統(tǒng)開發(fā)典型案例

2017-10-19 10:23:48 15

15 DSP嵌入式系統(tǒng)開發(fā)典型案例, 第5章 語(yǔ)音信號(hào)去噪和編碼系統(tǒng)設(shè)計(jì)

2017-10-20 14:30:44 4

4 1 引言 1996年3月,美國(guó)政府?dāng)?shù)字語(yǔ)音處理協(xié)會(huì)(DDVPC)選擇了2.4kbps混合激勵(lì)線性預(yù)測(cè)(MELP)語(yǔ)音編碼器作為窄帶保密語(yǔ)音編碼的產(chǎn)品以及各種應(yīng)用的新標(biāo)準(zhǔn)由于MELP具有良好的音質(zhì)

2017-10-24 10:59:25 2

2 TMS320DM6446的MELP_CELP混合編碼方法研究與實(shí)現(xiàn)

2017-10-26 14:15:00 6

6 1 引言 1996年3月,美國(guó)政府?dāng)?shù)字語(yǔ)音處理協(xié)會(huì)(DDVPC)選擇了2.4kbps混合激勵(lì)線性預(yù)測(cè)(MELP)語(yǔ)音編碼器作為窄帶保密語(yǔ)音編碼的產(chǎn)品以及各種應(yīng)用的新標(biāo)準(zhǔn)由于MELP具有良好的音質(zhì)

2017-11-01 15:44:00 3

3 1 引言 美國(guó)政府?dāng)?shù)字語(yǔ)音處理協(xié)會(huì)(DDVPC)選擇了2.4kbps混合激勵(lì)線性預(yù)測(cè)(MELP)語(yǔ)音編碼器作為窄帶保密語(yǔ)音編碼的產(chǎn)品以及各種應(yīng)用的新標(biāo)準(zhǔn)由于MELP具有良好的音質(zhì)、極低的碼率,以及

2017-11-02 10:21:40 1

1 1 引言 1996年3月,美國(guó)政府?dāng)?shù)字語(yǔ)音處理協(xié)會(huì)(DDVPC)選擇了2.4kbps混合激勵(lì)線性預(yù)測(cè)(MELP)語(yǔ)音編碼器作為窄帶保密語(yǔ)音編碼的產(chǎn)品以及各種應(yīng)用的新標(biāo)準(zhǔn)由于MELP具有良好的音質(zhì)

2017-11-02 10:51:16 4

4 MQ編碼是一種無(wú)損數(shù)據(jù)壓縮技術(shù),已被JPEG2000標(biāo)準(zhǔn)采用,其高復(fù)雜度成為JPEG2000系統(tǒng)實(shí)現(xiàn)的速度瓶頸。本文在分析MQ編碼算法軟件流程的基礎(chǔ)上提出了一種優(yōu)化的基于流水線處理的MQ編碼算法;并利用Xilinx FPGA的可編程特性詳細(xì)地將此算法模塊化,最后實(shí)現(xiàn)仿真驗(yàn)證。

2017-11-17 17:09:01 2964

2964 (SC-FDMA)技術(shù),下行采用正交頻分多址接入(OFDMA)技術(shù),其中物理層的技術(shù)相對(duì)于3G發(fā)生了革命性的變化。本文針對(duì)物理層下行鏈路的Turbo編碼器進(jìn)行研究,實(shí)現(xiàn)了基于FPGA的Turbo編碼器。

2017-12-19 10:50:01 0

0 針對(duì)日益復(fù)雜的地面測(cè)控需求,參照空間數(shù)據(jù)系統(tǒng)咨詢委員會(huì)( CCSDS)分包遙測(cè)標(biāo)準(zhǔn),在現(xiàn)場(chǎng)可編程門陣列( Field-Programmable G ate Array,FPGA)平臺(tái)上實(shí)現(xiàn)了一套高效

2018-01-09 15:36:39 1

1 提出一種集成超分辨率重建的圖像壓縮編碼新型框架。在編碼端對(duì)輸入圖像以因子2進(jìn)行下采樣,對(duì)下采樣圖像用JPEG標(biāo)準(zhǔn)編解碼,而后采用事先通過外部訓(xùn)練庫(kù)訓(xùn)練得到的字典,對(duì)解碼后的圖像進(jìn)行基于學(xué)習(xí)的超分辨率

2018-03-19 11:16:33 1

1 直在努力通過降低語(yǔ)音編碼速率來擴(kuò)大通信系統(tǒng)的容量。在我國(guó),對(duì)低速率語(yǔ)音編碼技術(shù)也有迫切的需要,如保密通信、短波信道、水聲信道等對(duì)碼率要求嚴(yán)格的應(yīng)用場(chǎng)合。但現(xiàn)有語(yǔ)音編碼的國(guó)際標(biāo)準(zhǔn)傳輸速率都較高(一般

2018-06-01 13:37:00 1197

1197

關(guān)鍵詞:AMBE-2000 , 語(yǔ)音系統(tǒng) 語(yǔ)音通信是數(shù)字通信系統(tǒng)中最常用的通信方式之一,優(yōu)良的語(yǔ)音編解碼算法能夠更加有效地節(jié)省帶寬資源,提高頻率利用率。現(xiàn)在語(yǔ)音編碼技術(shù)可以廣泛的應(yīng)用在話音多路傳輸

2018-10-17 14:19:02 276

276 近年來,語(yǔ)音識(shí)別研究大部分集中在算法設(shè)計(jì)和改進(jìn)等方面,而隨著半導(dǎo)體技術(shù)的高速發(fā)展,集成電路規(guī)模的不斷增大與各種研發(fā)技術(shù)水平的不斷提高,新的硬件平臺(tái)的推出,語(yǔ)音識(shí)別實(shí)現(xiàn)平臺(tái)有了更多的選擇。語(yǔ)音識(shí)別技術(shù)在與DSP、FPGA、ASIC等器件為平臺(tái)的嵌入式系統(tǒng)結(jié)合后,逐漸向?qū)嵱没⑿⌒突较虬l(fā)展。

2019-06-10 08:00:00 6

6 基于CPU軟核模塊算法IP的方法對(duì)一個(gè)1.6Kb/s類MELP語(yǔ)音壓縮編碼算法進(jìn)行了實(shí)現(xiàn),并將整個(gè)語(yǔ)音壓縮編碼器在FPGA上進(jìn)行了整體驗(yàn)證,實(shí)驗(yàn)結(jié)果說明本文給出的語(yǔ)音壓縮編碼器的實(shí)現(xiàn)結(jié)構(gòu)是可行

2021-01-22 15:08:38 17

17 今天是畫師第二次和各位大俠見面,執(zhí)筆繪畫FPGA江湖,本人最近項(xiàng)目經(jīng)驗(yàn),寫了篇基于FPGA的Varint編碼(壓縮算法)實(shí)現(xiàn),這里分享給大家,僅供參考。如有轉(zhuǎn)載,請(qǐng)?jiān)谖恼碌撞苛粞裕?qǐng)勿隨意轉(zhuǎn)載,否則

2021-04-02 16:29:16 1580

1580

現(xiàn)場(chǎng)可編程邏輯陣列(FPGA)資源豐富,結(jié)構(gòu)靈活,近年來發(fā)展迅猛。針對(duì)其特點(diǎn),本文設(shè)計(jì)了基于FPGA的增量式光電編碼器的接口電路,實(shí)現(xiàn)了對(duì)增量式編碼器脈沖信號(hào)的倍頻、鑒相及計(jì)數(shù)等功能。

2021-04-27 13:57:50 3886

3886

基于提升框架的小波變換方法,利用FPGA 可編程特性可實(shí)現(xiàn)多種小波變換。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近幾年提出的一種小波變換方法,用它的框架結(jié)構(gòu)能有

2023-05-11 15:33:30 456

456

國(guó)產(chǎn)FPGA研究框架

2023-01-13 09:06:57 6

6 電子發(fā)燒友網(wǎng)站提供《基于FPGA的直接序列擴(kuò)頻和差錯(cuò)控制碼編碼系統(tǒng)的實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-11-06 15:57:52 0

0 電子發(fā)燒友網(wǎng)站提供《使用基于標(biāo)準(zhǔn)的接口的框架是如何簡(jiǎn)化編碼.pdf》資料免費(fèi)下載

2023-11-14 14:10:40 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論