時序發生器的設計,基于CPLD和VerilogHDL語言的一種線陣CCD驅動時序電路的設計,基于CPLD和Verilog的高精度線陣CCD驅動電路設計,基于CPLD和VHDL的一種線陣CCD驅動時序電路

2019-06-03 16:45:25

它們的基本設計方法是借助于 EDA 設計軟件,用原理圖、狀態機和硬件描述語言等方法,生成相應的目標文件,最后用編程器或下載電纜,由 CPLD/FPGA 目標器件實現。 生產 CPLD/FPGA

2019-03-04 14:10:13

各位好,請問哪里有免費下載的 CPLD系統設計及VHDL語言的視頻教程?是天祥的。淘寶里有好多賣的,可是要淘寶帳戶和錢呀?

2008-07-20 10:29:10

FPGA 加三移位法,有人用vhdl 語言寫過嗎

2019-03-20 15:59:05

7-5606-1132-X/TP·0574本書介紹了FPGA的相關基礎知識, VHDL硬件描述語言,FPGA開發軟件的使用;器件配置與調試;FPGA設計中的基本問題和電路設計實例等。 《CPLD

2012-02-27 11:31:10

CPLD的電路規模、功能、性能等方面強化之后的產物。(特權同學版權所有)一般而言, FPGA與CPLD之間的區別如表1.1所示。(特權同學版權所有)表1.1 FPGA和CPLD的比較總而言之,FPGA

2019-02-21 06:19:27

希望在今后的學習中大家多多幫助,先來幾個基礎的verilog 教材吧 現在我用到了FPGA關鍵分配的知識。 不過還是想系統的學習一下。那就先從軟件的使用和語法開始學習吧。 完整的pdf格式文檔電子發燒友下載地址(共31頁): FPGA中文VHDL語言教程.pdf

2018-07-04 01:11:32

FPGA入門:Verilog/VHDL語法學習的經驗之談 本文節選自特權同學的圖書《FPGA/CPLD邊練邊學——快速入門Verilog/VHDL》書中代碼請訪問網盤:http

2015-01-29 09:20:41

CPLD的電路規模、功能、性能等方面強化之后的產物。(特權同學版權所有)一般而言, FPGA與CPLD之間的區別如表1.1所示。(特權同學版權所有)表1.1 FPGA和CPLD的比較總而言之,FPGA

2015-03-12 13:54:42

基于VHDL語言的數字鐘系統設計 基于FPGA的交通燈控制 采用可編程器件(FPGA/CPLD)設計數字鐘 數字鎖相環法位同步信號 基于FPGA的碼速調整電路的建模與設計 誤碼檢測儀

2012-02-10 10:40:31

VHDL 主要用于描述數字系統的結構、行為、功能和接口。除了含有許多具有硬件特征的語句外,VHDL 在語言形式、描述風格和句法上與一般的計算機高級語言十分相似。VHDL 的程序結構特點是將一項

2018-09-07 09:04:45

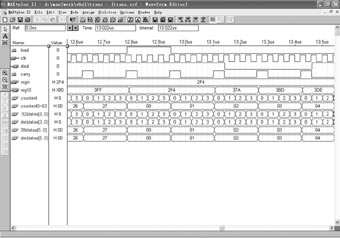

描述語言方式(如Verilog或VHDL)進行設計。2.綜合輸入的設計被綜合進入由邏輯元素(LEs,FPGA芯片提供)組成的電路中。3.功能仿真綜合電路被測試以驗證其功能是否正確,次仿真不考慮時序因素

2017-10-24 14:59:23

EDA技術具有什么特征?FPGA是什么原理?FPGA設計應用及優化策略基于VHDL的FPGA系統行為級設計

2021-04-15 06:33:58

用vhdl實現cpld配置fpga,配置成功后在usermode下設置一個重新配置信號,當信號有效時對fpga進行重新配置;fpga配置程序放在flash內;現在遇到的問題是,上電cpld能夠正常配置fpga并且進入usermode ,但是加上重新配置語句過后就不能成功配置fpga,求高人指點~

2013-01-17 22:35:39

超高速集成電路硬件描述語言,主要是應用在數字電路的設計中。它在中國的應用多數是用在FPGA/CPLD/EPLD的設計中。當然在一些實力較為雄厚的單位,它也被用來設計ASIC。VHDL主要用于描述數字系統的結構

2015-09-30 13:48:29

大家熟悉在CPLD/FPGA 開發中一個關鍵的技術——狀態機,并且簡單介紹了一下RTL 視圖的使用。第三講:加/減計數器例程,講解了計數器的VHDL 語言的設計過程,以及硬件下載的方法,并且可以通過

2020-05-14 14:50:30

,讓大家熟悉在CPLD/FPGA開發中一個關鍵的技術——狀態機,并且簡單介紹了一下RTL視圖的使用。 第三講:加/減計數器例程,講解了計數器的VHDL語言的設計過程,以及硬件下載的方法

2009-03-26 16:38:29

大家好,今天第一次發帖,見笑了。因初學FPGA、cpld,不知從哪著手,以前看過EDA,覺得VHDL語言比較復雜

2009-10-15 22:37:06

如題,multisim12能不能進行FPGA/CPLD的VHDL仿真??各位大神,multisim12到底能不能進行VHDL的仿真呢?看上multisim的直觀,可惜好像不能使用里面的FPGA器件。。各種憂傷啊。。。。。求助。。。

2013-09-22 17:09:04

的邊界掃描測試第5章 Xilinx Foundation應用基礎第6章 Foundation高級應用第7章 VHDL語言簡介第8章 CPLD/FPGA在數字系統設計中的應用第9章 CPLD/FPGA在通信

2018-03-29 17:11:59

`CPLD、Spartan可編程器件的基礎知識,VHDL語言基礎,Foundation編輯工具使用,高級應用以及CPLD/FPGA在數字系統設計的應用。`

2021-04-06 11:43:55

請問使用VHDL語言設計FPGA有哪些常見問題?

2021-05-06 09:05:31

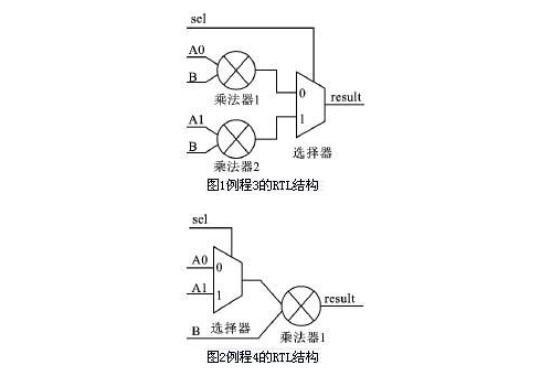

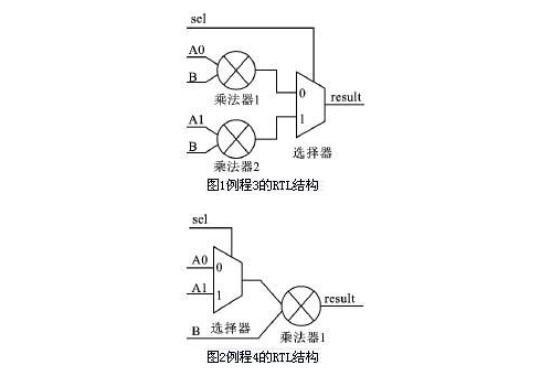

其在設計思路和編程風格等方面也存在差異,這些差異會對系統綜合后的電路整體性能產生重要的影響。在VHDL語言電路優化設計當中,優化問題主要包括面積優化和速度優化。面積優化是指CPLD/FPGA的資源

2019-06-18 07:45:03

基于CPLD的4*4矩陣鍵盤電路設計,用的是VHDL語言

2012-11-24 19:47:18

自從天祥電子推出40小時的“十天學會單片機和C語言編程”視頻教程后,受到了廣大電子愛好者的好評,并希望我們能夠趕緊推出“CPLD器件及VHDL程序設計”的視頻教程,為了能夠滿足大家的要求,提供更多

2009-02-07 11:34:24

,同時包括編寫后如何查找和修改錯誤。教程介紹:第一講:主要講解CPLD 系統開發的基本概念,介紹了CPLD 和FPGA 的各自特點、 生產廠家和相應的軟件以及開發相關的硬件描述語言。以分頻器為例,讓

2012-09-29 21:32:44

利用現場可編程門陣列(FPGA)和VHDL 語言實現了PCM碼的解調,這樣在不改變硬件電路的情況下,能夠適應PCM碼傳輸速率和幀結構變化,從而正確解調數據。

2021-05-07 06:58:37

本文介紹利用VHDL語言實現 FPGA與單片機的串口異步通信電路。

2021-04-29 06:34:57

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起來的。

2019-10-18 08:20:51

本人今年剛接觸EDA,學習VHDL,FPGA/CPLD,最菜得是我對這些名詞的屬性都還不了解。VHDL是硬件語言,FPGA/CPLD是想單片機一樣的芯片嗎?那如果我以后從事VHDL那是算計算機里哪個

2020-06-03 04:08:29

淘汰的今天,作為一個電類專業的畢業生應該熟悉VHDL語言和CPLD、FPGA器件的設計,閻石教授新編寫的教材也加入了VHDL語言方面的內容,可見使用VHDL語言將數字系統集成到一塊集成電路中是現在

2009-10-22 15:44:59

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件

2019-08-28 08:05:46

串行通信發送器是什么工作原理?怎么用VHDL語言在CPLD上實現串行通信?

2021-04-13 06:26:46

在語法和風格上類似于高級編程語言,可讀性好,描述能力強,設計方法靈活,可移植性強,因此它已成為廣大EDA工程師的首選。目前,使用VHDL語言進行CPLD/FPGA設計開發,Altera和Lattice

2019-08-08 07:08:00

本人小菜鳥,開始學FPGA的時候學的Verilog語言,后來因為課題組前期的工作都是VHDL就該學VHDL了。最近聽了幾個師兄的看法,說國內用VHDL的已經很少了,建議我還是堅持用Verilog,小菜現在好糾結,請問到底應該用哪種語言呢?望各位大神指點!

2015-07-08 10:07:56

感覺模擬IC設計就應該是設計模擬電路.設計運放等,通過設計電路、在硅片上搭建TTL.CMOS......從而做成IC芯片;而我經常看到說IC設計就是使用VHDL語言設計IC,寫好VHDL語言后燒錄到FPGA.CPLD.......從而做成芯片。我想問的是這兩者有什么區別?

2018-08-29 09:45:43

),有時我們不需要使用完整的UART的功能和這些輔助功能。或者設計上用到了FPGA/CPLD器件,那么我們就可以將所需要的UART功能集成到FPGA內部。使用VHDL將UART的核心功能集成,從而使整個設計更加緊湊、穩定且可靠。本文應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2012-05-23 19:37:24

只要有數字電路的基礎,還是能較容易和快速地學會利用 CPLD/FPGA 設計數字系統的。 數字系統的基本部件比較簡單,它們是一些與門、或門、非門、觸發器和多路選擇器等,宏器件是一些加法器、乘法器等

2019-02-28 11:47:32

基于CPLD的狀態機該怎樣去設計?如何去描述VHDL語言?

2021-04-28 07:01:10

VHDL硬件描述語言教學:包括fpga講義,VHDL硬件描述語言基礎,VHDL語言的層次化設計的教學幻燈片

2006-03-27 23:46:49 93

93 第1章 緒論 1.1 關于EDA 1.2 關于VHDL 1.3 關于自頂向下的系統設計方法 1.4 關于應用 VHDL的 EDA過程 1.5 關于在系統編程技術 1.6 關于FPGA/CPLD的優勢 1.7

2008-06-04 10:24:06 1679

1679 《Altera FPGA/CPLD設計(高級篇)》結合作者多年工作經驗,深入地討論了Altera FPGA/CPLD的設計、優化技巧。在討論FPGA/CPLD設計指導原則的基礎上,介紹了Altera器件的高級應用;引領讀者

2009-02-12 09:19:12 4799

4799 EDA/VHDL講座主要內容一、EDA、EDA技術及其應用與發展二、硬件描述語言三、FPGA和CPLD四、EDA工具軟件五、電子設計競賽幾個實際問題的討論六、VHDL語言初步七

2009-03-08 10:54:10 39

39 A CPLD VHDL Introduction

This introduction covers the fundamentals of VHDL as applied to Complex

2009-03-28 16:14:37 25

25 FPGA/VHDL技術是近年來計算機與電子技術領域的又一場革命。本書以AAltera公司的FPGA/CPLD為主詳細介紹了FPGA、CPLD為主詳細介紹了FPGA的相關知識,MAX+PLUSⅡ開發環境和VHDL語言基礎,并

2009-07-11 15:06:42 58

58 VHDL語言及其應用的主要內容:第一章 硬件模型概述第二章 基本的VHDL編程語言第三章 VHDL模型的組織第四章 VHDL綜合工具第五章 VHDL應用樣例附錄A VHDL

2009-07-20 12:06:15 0

0

介紹了用VHDL 語言在硬件芯片上實現浮點加/ 減法、浮點乘法運算的方法,并以Altera

公司的FLEX10K系列產品為硬件平臺,以Maxplus II 為軟件工具,實現了6 點實序列浮點加/ 減法

2009-07-28 14:06:13 85

85 本文采用VHDL語言設計了基于CPLD的計數及LED譯碼電路,該設計方法符合電子系統設計的發展方向。關鍵詞:計數器;LED譯碼;CPLD;VHDL在各種檢測與控制系統及儀表中,對發生的事

2009-08-24 08:32:39 28

28 VHDL語言描述數字系統:本章介紹用 VHDL 描述硬件電路的一些基本手段和基本方法。 VHDL 語言是美國國防部在 20 世紀 80 年代初為實現其高速集成電路計劃(VHSIC)而提出的

2009-09-01 09:02:40 37

37 VHDL 語言程序的元素:本章主要內容:VHDL語言的對象VHDL語言的數據類型VHDL語言的運算符VHDL語言的標識符VHDL語言的詞法單元

2009-09-28 14:32:21 41

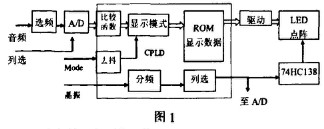

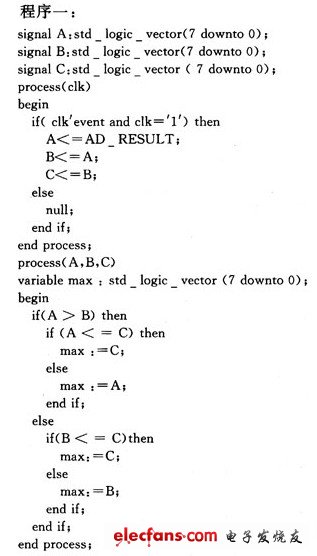

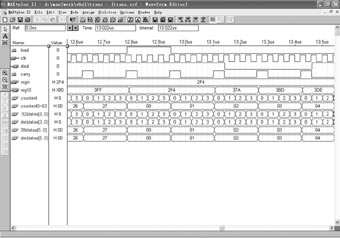

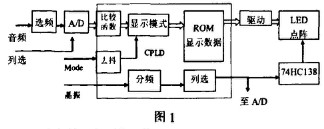

41 本文基于VHDL硬件描述語言,利用CPLD器件EPM570T100C5和LED點陣屏實現了對音頻信號的頻譜顯示,給出了設計過程、VHDL語言源程序和實驗結果,拓展了CPLD在顯示領域的應用。

2010-02-24 14:46:45 28

28 基于FPGA/CPLD芯片的數字頻率計設計摘要:詳細論述了利用VHDL硬件描述語言設計,并在EDA(電子設計自動化)工具的幫助下,用大規模可編程邏輯器件(FPGA/CPLD)實現

2010-04-30 14:45:13 132

132 簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和1.5的分頻器的設計為例,介紹了在MaxPlusII開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過

2010-07-17 17:55:57 36

36 本文基于VHDL硬件描述語言,利用CPLD器件EPM570T100C5和LED點陣屏實現了對音頻信號的頻譜顯示,給出了設計過程、VHDL語言源程序和實驗結果,拓展了CPLD在顯示領域的應用。

2010-07-17 18:07:40 25

25 探討電梯控制技術的發展歷史和技術現狀,仔細研究CPLD器件的工作原理,開發流程以及VHDL語言的編程方法;采用單片CPLD器件,在MAX+plusⅡ軟件環境下,運用VHDL語言設計一個16樓層單

2010-12-27 15:27:35 56

56 摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸

2006-03-13 19:36:44 869

869

用VHDL語言實現3分頻電路

標簽/分類:

眾所周知,分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相

2007-08-21 15:28:16 5527

5527 實驗八、VHDL語言的組合電路設計一? 實驗目的1掌握VHDL語言的基本結構及設計的輸入方法。2掌握VHDL語言的組合電路設計方法。二? 實驗設備與儀器

2009-03-13 19:26:58 2368

2368 【摘 要】 通過設計實例詳細介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優越性。

2009-05-10 19:47:30 1111

1111

摘 要:通過設計實例詳細介紹了用Verilog HDL語言開發FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優越性。

2009-06-20 11:51:28 1857

1857

摘 要: 串行通信是實現遠程測控的重要手段。采用VHDL語言在CPLD上實現了串行通信,完全可以脫離單片機使用。

關鍵詞:

2009-06-20 12:43:50 570

570

摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸

2009-06-20 12:45:00 627

627

用VHDL語言實現3分頻電路(占空比為2比1)

分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖

2009-06-22 07:46:33 7831

7831 采用CPLD/FPGA的VHDL語言電路優化原理設計

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起

2010-03-19 11:38:02 2318

2318

在我國使用Verilog HDL的公司比使用VHDL的公司多。從EDA技術的發展上看,已出現用于CPLD/FPGA設計的硬件C語言編譯軟件,雖然還不成熟,應用極少,但它有可能會成為繼VHDL和Verilog之后,設計大規模CPLD/FPGA的又一種手段。

2011-03-12 11:21:20 1686

1686 簡要介紹了 VHDL 語言進行工程設計的優點,并詳細說明了利用VHDL語言設計狀態機電電路的過程,最后進行了仿真,仿真結果證明該設計能夠實現狀態機電路的功能。

2011-07-18 10:31:20 83

83 利用一塊芯片完成除時鐘源、按鍵、揚聲器和顯示器(數碼管)之外的所有數字電路功能。所有數字邏輯功能都在CPLD器件上用VHDL語言實現。這樣設計具有體積小、設計周期短(設計過

2011-09-27 15:08:56 366

366 VHDL翻譯成中文就是超高速集成電路硬件描述語言,主要是應用在數字電路的設計中。目前,它在中國的應用多數是用在FPGA/CPLD/EPLD的設計中。當然在一些實力較為雄厚的單位,它也被用

2011-12-13 10:36:21 2487

2487 本資料是關于基于Quartus II FPGA/CPLD數字系統設計實例(VHDL源代碼文件),需要的可以自己下載。

2012-11-13 14:03:36 907

907 altera FPGA/CPLD高級篇(VHDL源代碼)

2012-11-13 14:40:38 134

134 基于CPLD的VHDL語言數字鐘(含秒表)設計

2015-11-04 15:14:36 9

9 SVPWM算法優化及其FPGA_CPLD實現

2016-04-13 15:42:35 18

18 ,或是硬件描述語言自由的設計一個數字系統。通過軟件仿真,我們可以事先驗證設計的正確性。在PCB完成以后,還可以利用FPGA/CPLD的在線修改能力,隨時修改設計而不必改動硬件電路。 使用FPGA/CPLD來開發數字電路,可以大大縮短設計時間,減少PCB面積,提高系統的可靠性。 FPGA/CPLD還

2017-10-09 09:52:20 14

14 在小規模數字集成電路就要淘汰的今天,作為一個電類專業的畢業生應該熟悉VHDL語言和CPLD、FPGA器件的設計,閻石教授新編寫的教材也加入了VHDL語言方面的內容,可見使用VHDL語言將數字系統集成

2017-12-05 09:00:31 20

20 LED點陣顯示屏具有醒目、動態效應好、省電節能、亮度較高、用途廣等優點,是現代 化城市的主要標志之一。利用VHDL硬件描述語言設計了以CPLD器件為核心的控制電路, 在LED點陣屏上實現了音頻信號的頻譜型電平動態顯示, 而且具有顯示模式多樣化、易編程 修改,顏色可變、動態效果好等優點。

2019-04-26 08:08:00 1933

1933

用VHDL語言設計交通燈控制系統,并在MAX+PLUS II系統對FPGA/CPLD芯片進行下載,由于生成的是集成化的數字電路,沒有傳統設計中的接線問題,所以故障率低、可靠性高,而且體積小。體現了EDA技術在數字電路設計中的優越性。

2018-11-05 17:36:05 23

23 本文檔的主要內容詳細介紹的是FPGA視頻教程之FPGA和CPLD與VHDL基礎知識的詳細資料說明。主要的目的是:1.VHDL入門,2.設計單元,3.體系結構建模基礎,4.VHDL邏輯綜合,5.層次

2019-03-20 14:35:19 9

9 本文檔的主要內容詳細介紹的是使用FPGA和VHDL語言進行的搶答器設計資料合集免費下載。

2019-06-03 08:00:00 19

19 什么是vhdl語言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述語言)。VHSIC是Very High Speed

2020-04-23 15:58:49 10242

10242 VHDL電路設計的優化與VHDL描述語句、EDA工具以及可編程器件(PLD)的選用都有著直接的關系。

2020-07-16 08:46:03 2333

2333

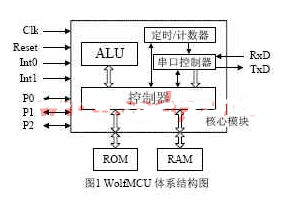

基于以上討論,可以看出ASIP+FPGA設計模式可以從很大程度上解決引言中提到的兩個難題。為了進行更深入的研究,我們對該設計模式進行了嘗試,用VHDL硬件描述語言在FPGA上實現了一個8位微處理器

2020-07-28 17:44:49 562

562

經常看到不少人在論壇里發問,FPGA是不是用C語言開發的?國外有些公司專注于開發解決編譯器這方面問題,目的讓其能夠達到用C語言替代VHDL語言的目的,也開發出了一些支持用c語言對FPGA進行編程的開發工具。但在使用多的FPGA編程語言還是verilog和VHDL語言,一般不使用C語言進行編程。

2020-07-29 16:37:37 23118

23118 本文檔的主要內容詳細介紹的是FPGA VHDL語言基礎的學習課件免費下載。

2021-01-21 16:30:00 26

26 簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和1.5的分頻器的設計為例,介紹了在MaxPlusII開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過程和方法。該設計具有結構簡單、實現方便、便于系統升級的特點。

2021-03-16 09:45:53 10

10 FPGA CPLD數字電路設計經驗分享.(電源技術發展怎么樣)-FPGA CPLD數字電路設計經驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 FPGA CPLD中的Verilog設計小技巧(肇慶理士電源技術有限)-FPGA CPLD中的Verilog設計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35 在這個項目中,我們用 VHDL 語言創建一個 8 位算術邏輯單元 (ALU),并在連接到帶有輸入開關和 LED 顯示屏的定制 PCB 的 Altera CPLD 開發板上運行。

2023-10-24 17:05:57 675

675

和VHDL都是用于邏輯設計的硬件描述語言,并且都已成為IEEE標準。它們能形式化地抽象表示電路的結構和行為,支持邏輯設計中層次與領域的描述,具有電路仿真與驗證機制以保證設計的正確性,并便于文檔管理和設計重用。 fpga用什么語言開發 FPGA(現場可編程邏輯門陣列)的開發主要使用硬件描述語言(HD

2024-03-14 17:09:32 223

223 功能,從而實現對數字電路的高效定制。FPGA語言主要包括VHDL(VHSIC Hardware Description Language)和Verilog等,這些語言具有強大的描述能力,能夠精確地定義硬件的每一個細節,從而實現復雜的數字系統設計。

2024-03-15 14:50:26 166

166

電子發燒友App

電子發燒友App

評論