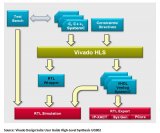

本在生產力方面進行了兩大改進。Vivado設計套件2013.1版本新增了一款以IP為中心的設計環境,用以加速系統集成;而其提供的一套完整數據庫,則可加速C/C++系統級設計和高層次綜合(HLS)。

2013-04-08 15:08:54 902

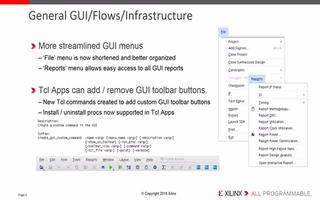

902 作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 3153

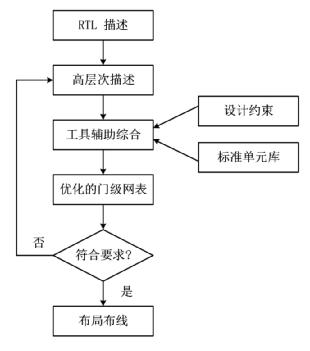

3153 綜合(Synthesis)是指將RTL設計轉換為門級描述。Vivado開發套件中的綜合工具是一款時序驅動型、專為內存使用率和性能優化的綜合工具,支持System Verilog 2012

2020-12-29 14:07:42 5432

5432 的Zynq 7000, 找了一個HLS的教程,就開始了如下入門實驗,體驗高級語言綜合設計IP。Vivado HLS是Xilinx 推出的高層次綜合工具,采用C/C++語言進行FPGA設計。HLS提供了一些

2020-10-14 15:17:19 2881

2881

51單片機是較早使用的了,現在單片機已發展到更高層次的STM32的單片機了。這個51類型的單片機還有發展前景嗎?

2021-08-18 09:50:57

SoC器件上快速地加速和集成您的計算機視覺應用。本次研討會將通過對一個具體案例的流程進行“逐層拆解(Step-by-Step)一個設計案列”的方式,向您介紹如何利用Vivado HLS(高層次綜合

2013-12-30 16:09:34

Vivado下的工程能用Synplify綜合嗎?怎么找不到在綜合工具添加的位置呢?

2019-06-04 09:45:16

菜鳥求指教,最近在用vivado 2015.3 做個小項目,遇到問題:代碼綜合后會報錯:'get_property' expects at least one object.錯誤地址在IP的 clocks.xdc文件中。

2016-08-31 10:42:56

HLS高階綜合(highlevelsynthesis)在被廣泛使用之前,作為商業技術其實已經存在了20多年。設計團隊對于這項技術可以說呈現出兩極化的態度:要么堅信它是先進技術之翹楚,要么對其持謹慎

2021-07-06 08:00:00

Vivado帶來一些負面影響,以便在綜合或布局布線期間進行性能優化?提前致謝。以上來自于谷歌翻譯以下為原文I always see the training documents mentioned "

2019-03-21 12:42:34

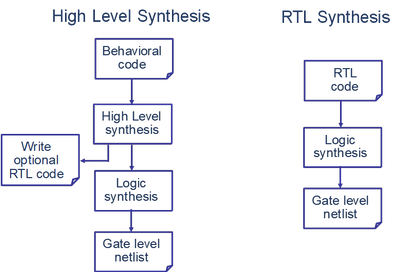

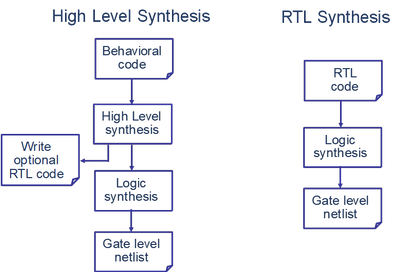

下圖揭示了高層次綜合工作的基本流程,以及它于傳統的RTL綜合流程的對比。接下來將對行為描述,行為綜合,分析與優化三個主要子流程詳細描述。 1、行為描述 當我們把HLS技術的起點立為一種

2021-01-06 17:52:14

高層次綜合技術原理淺析

2021-02-01 06:04:00

描述語言(HDL)完成系統行為級設計,最后通過綜合器和適配器生成最終的目標器件,這樣的設計方法被稱為高層次的電子設計方法。下面介紹與EDA基本特征有關的幾個概念。

2019-10-08 14:25:32

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

1、HLS最全知識庫介紹高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。對于AMD Xilinx而言

2022-09-07 15:21:54

fpga高手經驗談doc文檔在數字電路的設計中,時序設計是一個系統性能的主要標志,在高層次設計方法中,對時序控制的抽象度也相應提高,因此在設計中較難把握,但在理解RTL電路時序模型的基礎上,采用合理

2012-08-11 11:30:39

和實物控制實驗,同時也為了高層次的設計開發實驗提供良好的條件。為了結合教學要求,設計過程中參考了國內多種教材,從中...

2021-09-08 07:31:55

目錄第1章:高層次生產力設計方法指南第2章:系統設計第3章:shell開發第4章:基于C語言的IP開發第5章:系統集成

2017-12-13 09:50:31

、仿真教學軟件、模擬控制實訓掛箱、實物與于一體,綜合性強、功能齊全。 PLC部分可直觀地進行基本指令訓練,多個應用廣泛的 PLC 實際應用模擬和實物控制訓練,同時也為了高層次的設計開發實驗實訓提供良好

2021-09-03 08:53:06

、應用、后端支持.pdf直播簡介:為了解決FPGA的可編程性問題,實現從算法到RTL設計的快速編譯,我們引入了基于MLIR(多級別中間表示)的高層次綜合框架ScaleHLS,對算法的高層次描述進行多級

2022-11-27 12:43:17

何使用硬件描述語言來完成設計,最終實現PL端LED閃爍的效果。在本章我們同樣會通過LED閃爍實驗,來講解如何使用Vivado HLS工具對C語言進行高層次綜合,并最終生成RTL級的實現結果,以及在

2020-10-10 16:48:25

1、使用Vitis HLS創建屬于自己的IP高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。對于AMD

2022-09-09 16:45:27

嗨, 我們正在嘗試將自定義IP連接到vivado的IP集成商中的可用IP。但我們在綜合設計時發現了一些問題。請查看附帶的截圖以獲取詳細視圖。謝謝。

2020-04-09 06:28:36

、sysfs等。中層次指被高層次封裝調用的驅動,比如I2C、sdio等等。他們也有可能直接被應用層調用,這樣就直接上升為高層驅動了。低層次驅動指被中層次調用封裝的驅動,它們可能是platform驅動、GPIO驅動等等。驅動一般還存在混用,比如SDIO+網絡驅動等等。那種單純的簡單的字符設備驅動,一

2021-12-24 06:10:40

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉化成硬件描述語言,同時支持基于OpenCL等框架

2021-11-11 09:38:32

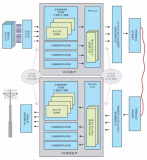

本文運用目前基于FPGA(Field Programmable Gate Array)的SoPC (System on Programmable Chip)技術構建軟件無線電平臺。大大提高了數字信號處理的能力和速度,并且降低了系統功耗,縮小了系統體積,為更高層次的3G無線通信要求提供了解決方案。

2021-05-06 06:21:24

您好我有一個關于vivado hls的問題。RTL是否來自xivix FPGA的vivado hls onyl?我們可以在Design Compiler上使用它進行綜合嗎?謝謝

2020-04-13 09:12:32

親愛的大家,我現在正在使用Vivado 2013.3。我試圖將PL結構時鐘從1 MHZ更改為500KHZ。 (1 MHZ下沒問題)但是,Vivado在運行綜合時崩潰了。對我來說減少PL結構時鐘非常重要,因為我打算在一個時鐘周期內收集更多的XADC數據。我該怎么辦?謝謝!

2020-03-25 08:40:07

利用Mentor高層次綜合技術快速實現復雜DSP算法摘要:為了滿足產品上市時間和功能豐富性的要求,越來越多的先進設計公司開始提高設計的抽象層次進行復雜的D

2010-04-29 14:01:59 34

34 摘要:Mentor公司提供的Catapult SL開發工具,不僅是快速算法驗證,也是模塊級結構設計和分析的有力工具,能有效地縮短產品的上市時間。本文首先回顧Catapult綜合工具開發的基本流程

2010-06-08 08:07:11 11

11 隨著半導體制造工藝的持續縮小,在90 納米及以下的工藝中,時序、面積、功耗以及可制造性的問題都日趨復雜。設計者希望在電子系統級 (ESL) 設計階段,就能知道他們的設

2010-07-04 11:44:09 13

13 在高層次對系統進行功耗佑算和功耗優化是soc設計的關健技術本文首先給出soc設計的特點和流程,然后綜述目前高層次功耗估算和功耗優化的常用方法和技術,重點論述寄存器傳輸級和

2011-12-27 16:42:38 46

46 為了解決實現的瓶頸,Vivado 工具采用層次化器件編輯器和布局規劃器、速度提升 了3 至 15 倍且為 SystemVerilog 提供業界領先支持的邏輯綜合工具、速度提升 了4 倍且確定性更高的布局布

2012-04-25 10:54:16 59

59 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 高層次綜合設計最常見的的使用就是為CPU創建一個加速器,將在CPU中執行的代碼移動到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設計中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

最新? UltraFast?? 設計方法指南 和 UltraFast? 高層次生產力設計方法指南 查看最新? Vivado QuickTake? 視

2017-11-10 14:49:02 887

887 度更高的C語言層面上,加速算法開發;對軟件工程師而言,它可以使軟件工程師將計算密集型算法采用有別于傳統CPU處理器的FPGA上實現。高層次綜合可以使工程師在C語言層面上同時進行算法開發和算法驗證。 Xilinx提供了另一工具Vivado HLS(Vivado High Level S

2017-02-08 12:39:34 265

265

HLx 版本均包括帶有 C/C++ 庫的 Vivado 高層次綜合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE? IP 子系統以及完整的 Vivado 實現工具套件,使主流用戶能夠方便地采用生產力最高、最

2017-02-08 19:35:06 386

386 高層次綜合 (HLS)的增強功能,可實現更大型 IP 構建模塊及相關模塊的復用,從而有助于加快集成和驗證速度,進

2017-02-09 01:15:42 225

225 Luke Miller并非一開始就是HLS(高層次綜合)的倡導者。在使用早期的工具版本的時候,他似乎有過一些糟糕的經歷。

2017-02-10 18:48:59 3334

3334

本文從程序員的角度對CNTK和TensorFlow做高層次的對比。本文也不屬于性能分析,而是編程模型分析。文中會夾雜著大量的代碼。 原標題:當TensorFlow遇見CNTK CNTK是微軟用于搭建

2017-10-12 14:17:04 0

0 在使用高層次綜合,創造高質量的RTL設計時,一個重要部分就是對C代碼進行優化。Vivado Hls總是試圖最小化loop和function的latency,為了實現這一點,它在loop

2017-11-16 14:44:58 3362

3362 ,有助于應對這種挑戰。 我們使用 Vivado? Design Suite 的高層次綜合 (HLS) 工具來評估針對 E-UTRA I/Q 數據的開放無線電設備接口 (ORI) 標準壓縮方案,以估計其對信號

2017-11-16 20:05:41 1918

1918

使用Xilinx Vivado HLS(Vivado 高層次綜合)工具實現浮點復數QRD矩陣分解并提升開發效率。使用VivadoHLS可以快速、高效地基于FPGA實現各種矩陣分解算法,降低開發者

2017-11-17 17:47:43 3293

3293

如果您正在努力開發計算內核,而且采用常規內存訪問模式,并且循環迭代間的并行性比較容易提取,這時,Vivado? 設計套件高層次綜合(HLS) 工具是創建高性能加速器的極好資源。通過向C 語言高級算法描述中添加一些編譯指示,就可以在賽靈思FPGA 上快速實現高吞吐量的處理引擎。

2017-11-17 18:12:01 1647

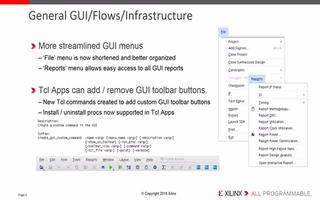

1647 在ISE下,對綜合后的網表進行編輯幾乎是不可能的事情,但在Vivado下成為可能。Vivado對Tcl的支持,使得Tcl腳本在FPGA設計中有了用武之地。本文通過一個實例演示如何在Vivado下利用Tcl腳本對綜合后的網表進行編輯。

2017-11-18 03:16:01 6899

6899

眾多應用中的一個,而且創建定制硬件需要花費時間和成本。是不是這樣? 最近聽說了賽靈思的高層次綜合工具Vivado?HLS后,我開始重新思考這一問題。高層次綜合工具與Zynq?-7000 All Programmable SoC的結合為設計開辟了新的可能性。

2017-11-18 09:12:24 1192

1192

Vivado的高層次綜合功能將幫助您為嵌入式視頻應用設計更好的排序網絡。從汽車到安全系統再到手持設備,如今采用嵌入式視頻功能的應用越來越多。每一代新產品都需要更多的功能和更好的圖像質量。但是,對于

2017-11-18 11:02:02 1681

1681 理由一:突破器件密度極限:在單個器件中更快速集成更多功能;理由二:Vivado以可預測的結果提供穩健可靠的性能和低功耗;理由三:Vivado設計套件提供了無與倫比的運行時間和存儲器利用率;理由四:使用Vivado高層次綜合生成基于C語言的IP。

2017-11-22 08:15:19 1421

1421 使用高層次綜合方法設計超大規模集成電路是一項前瞻性的工作。其設計理念旨在保證電路性能的前提下,縮短電路開發周期,讓產品更早投入到市場。然而針對高層次綜合工具面對算法轉換時編譯能力存在局限的問題,本文

2017-11-22 10:11:55 1

1 Vivado HLS配合C語言等高級語言能幫助您在FPGA上快速實現算法。 高層次綜合(HLS)是指自動綜合最初用C、C++或SystemC語言描述的數字設計。工程師之所以對高層次綜合如此感興趣,不僅是因為它能讓工程師在較高的抽象層面上工作,而且還因為它能方便地生成多種設計解決方案。

2019-10-06 10:44:00 1178

1178

我們使用 Vivado ?Design Suite 的高層次綜合 (HLS) 工具來評估針對 E-UTRA I/Q 數據的開放無線電設備接口 (ORI) 標準壓縮方案,以估計其對信號保真度的影響、造成的時延及其實現成本。我們發現賽靈思的 Vivado HLS 平臺能夠高效評估和實現所選壓縮算法。

2018-07-24 09:30:00 1901

1901

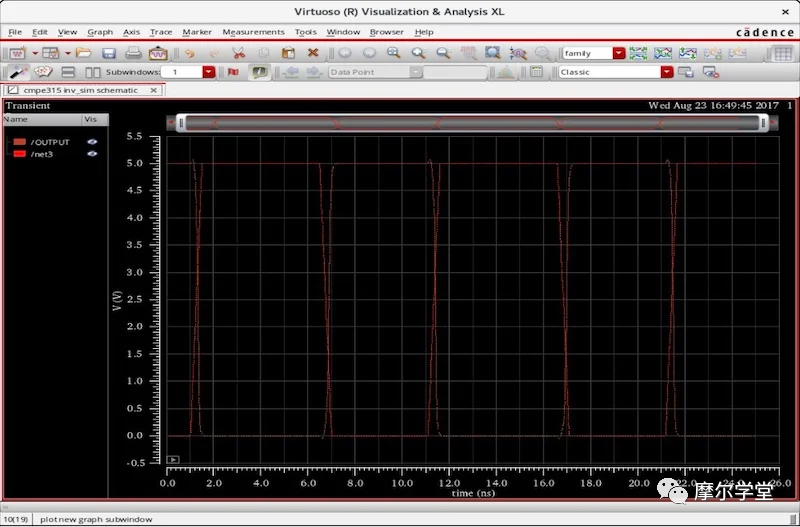

Verilog的主要應用包括:

– ASIC和FPGA工程師編寫可綜合的RTL代碼

– 高抽象級系統仿真進行系統結構開發

– 測試工程師用于編寫各種層次的測試程序

– 用于ASIC和FPGA單元或更高層次的模塊的模型開發

2018-08-09 08:00:00 36

36 、HL 設計版本和 HL WebPACK 版本。所有 HLx 版本均包括帶有 C/C++ 庫的 Vivado 高層次綜合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE IP

2018-08-17 11:43:00 2677

2677 All Programmable SoC 的生產力帶來重大突破。伴隨此款最新版Vivado 設計套件推出的還包括其內含的 Vivado 高層次綜合(HLS)和IP集成器的增強功能,以及最新性能監控

2018-09-06 16:07:00 1466

1466 達25%,性能提升5%。此外,2014.1版本還在Vivado HLS(高層次綜合)中新增了OpenCL內核硬件加速功能。

2018-09-13 16:59:00 1199

1199 新增了一款以IP為中心的設計環境,用以加速系統集成;而其提供的一套完整數據庫,則可加速C/C++系統級設計和高層次綜合(HLS)。 加速IP創建與集成 為了加速在All Programmable

2018-09-25 09:18:01 275

275 關鍵詞:汽車 中國.玉環首屆國際高層次人才創業創新大賽 沈陽分賽區 報名時間:2018年10月11日-10月21日 o立即報名 一、目的和意義 “為深入貫徹省委省政府和市委市政府關于推進“大眾創業

2018-10-27 16:24:01 170

170 觀看視頻,學習如何將 Vivado IP 和第三方綜合工具配合使用。 此視頻將通過一個設計實例引導您完成創建自定義 IP 的步驟;用第三方綜合工具IP黑盒子來審查所需 IP 輸出;整合 Vivado IP 網表和第三方綜合工具網表的兩個方法,即 “網表項目模式” 和 “非項目 Tcl 腳本模式”。

2018-11-21 06:34:00 4811

4811 本視頻重點介紹了Vivado設計套件2018.1版本中的新增功能,包括對操作系統以及器件的支持情況,還有高層次增強功能,以及各種功能改進以加速設計集成,實現和驗證的過程。

2018-11-20 06:28:00 2254

2254

的需求。客戶可在 Zynq? MPSoC 和 UltraScale? FPGA 芯片平臺上使用 Vivado? 高層次綜合 (HLS)、 SDSoC?、和 SDAccel? 軟件定義環境。Xilinx

2019-12-26 07:01:00 1409

1409

Xilinx 戰略應用高級工程師。專注于 C/C++ 高層次綜合,擁有多年利用 Xilinx FPGA 實現數字信號處理算法的經驗,對 Xilinx FPGA 的架構、開發工具和設計理念有深入的理解

2019-08-01 15:43:09 3508

3508 從 Vivado 2019.1 版本開始,Vivado 綜合引擎就已經可以支持增量流程了。這使用戶能夠在設計變化較小時減少總的綜合運行時間。

2019-07-21 11:02:08 1367

1367 高層次綜合(High-level Synthesis)簡稱 HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。所謂的高層次語言,包括 C、C++、SystemC

2019-11-21 16:28:56 8888

8888 意見明確,將人工智能納入“國家關鍵領域急需高層次人才培養專項招生計劃”支持范圍,綜合考慮有關高校高水平師資、國家級科研平臺、重大科研項目和攻關任務,以及產教融合、協同育人成效等情況,安排研究生尤其是博士生招生計劃專項增量。

2020-03-05 11:29:17 1635

1635 意見明確,將人工智能納入“國家關鍵領域急需高層次人才培養專項招生計劃”支持范圍,綜合考慮有關高校高水平師資、國家級科研平臺、重大科研項目和攻關任務,以及產教融合、協同育人成效等情況,安排研究生尤其是博士生招生計劃專項增量。

2020-03-07 15:47:47 1819

1819 -flatten_hierarchy full: 綜合時將原始設計打平,只保留頂層層次,執行邊界優化 none: 綜合時完全保留原始設計層次,不執行邊界優化 rebuilt: 綜合時將原始設計打平

2020-11-25 10:28:49 8164

8164 12月23日,據杭州市人力資源和社會保障局消息,阿里巴巴蔣凡被認定為蔣凡被認定為高層次人才,消息曝光后引發網友熱議。

2020-12-30 11:12:34 1969

1969 說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述

2021-01-14 09:27:28 1848

1848 說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述是:由更高抽象度的行為描述生產電路的技術。

2022-02-08 17:26:42 7041

7041

作為碧桂園集團旗下的初創型企業,博智林機器人副總裁劉震分享了打造高層次人才隊伍布局先進制造業的經驗。 ? 建筑行業和農業一樣,是信息化、自動化、智能化水平比較低的行業。博智林要做的研發很多。 劉震

2021-01-26 15:22:48 2814

2814 說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述是:由更高抽象度的行為描述生產電路的技術。

2021-01-28 09:11:08 3

3 在FPGA設計里,設計仿真完成RTL代碼設計后便是交給設計套件進行綜合及布局布線。在綜合過程里,Vivado里提供的參數選項有點兒多,今天閑暇抽空梳理下。 -flatten_hierarchy

2021-06-01 11:20:35 6511

6511 1.實驗目的通過例程探索Vivado HLS設計流用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目用各種HLS指令綜合接口優化Vivado HLS設計來滿足各種約束用不用的指令來探索

2021-11-06 09:20:58 6

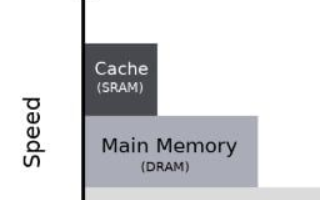

6 本文將從高層次探討什么是虛擬內存、它存在的原因以及它是如何工作的。

2022-04-28 17:06:56 1363

1363

Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數硬連線到器件邏輯互連結構和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應用加速開發流程中實現硬件

2022-05-25 09:43:36 1930

1930 VitisHLS是一種高層次綜合工具,支持將C、C++和OpenCL函數硬連線到器件邏輯互連結構和RAM/DSP塊上。

2022-06-14 09:20:51 1946

1946 Vitis 環境開發方法論反應了 Versal ACAP 系統的異構性質,此類系統通常是由 PS、PL 和 AI 引擎功能組成的。您可使用 Vitis 工具來獨立開發并驗證這些組件,并逐漸將其加以集成以構成最終系統。

2022-06-16 10:23:38 971

971 基于硬件描述語言HDL,抽象出HLS(High-Level Synthesis)(翻譯為高層次綜合?怎么聽起來都沉得別扭)技術,通過高層設計去隱藏很多底層邏輯和細節,讓FPGA的開發更加簡單。

2022-09-05 09:12:48 704

704 這是一個關于系統構成和芯片架構的高層次描達文件,涉及芯片的高層次操作、引腳分配與定義、軟件編程模型、可測性、寄存器定義以及應用模型等。

2022-11-10 20:48:51 10610

10610 這是一個關于系統構成和芯片架構的高層次描達文件,涉及芯片的高層次操作、引腳分配與定義、軟件編程模型、可測性、寄存器定義以及應用模型等。

2022-11-10 16:25:15 1256

1256 01 演講題目 ? 開源硬件系列02期: 從PyTorch到RTL - 基于MLIR的高層次綜合技術 02 演講時間 ? 2022年11月27日 上午?10:00 03 內容簡介 ? 為了解

2022-11-24 08:15:03 1379

1379 英特爾? NUC 8 支持更高層次的設計

2022-12-29 10:02:52 619

619

)和連線(wire)息息相關。Verilog便具有將ASM圖表和電路框圖用計算機語言表達的能力,本文將講述Vivado綜合支持的Verilog硬件描述語言; Verilog提供了行為化和結構化兩方面的語言結構,描述設計對象時可以選擇高層次或低層次的抽象等級。使用V

2022-12-29 10:30:09 3387

3387 模擬IC設計與數字 IC 設計有很大不同。其中數字IC設計在與確定的柵- /晶體管級放置和路由的具體系統和過程的抽象水平大多進行,模擬IC設計通常涉及更個性化的焦點到每個電路,甚至大小和每個具體晶體管。

2023-03-16 10:36:09 333

333

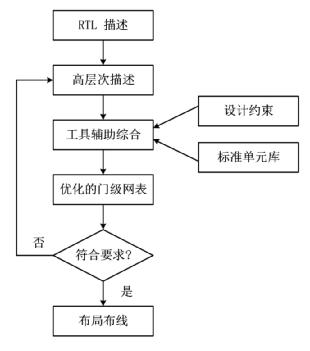

綜合,就是在標準單元庫和特定的設計約束基礎上,把數字設計的高層次描述轉換為優化的門級網表的過程。標準單元庫對應工藝庫,可以包含簡單的與門、非門等基本邏輯門單元,也可以包含特殊的宏單元,例如乘法器、特殊的時鐘觸發器等。設計約束一般包括時序、負載、面積、功耗等方面的約束。

2023-03-30 11:45:49 556

556

“工業控制系統層次模型”是為了解決工業控制系統設計中的復雜性而提出的一種模型。該模型將整個控制系統分為4個層次,即系統層次、任務層次、結構層次和實現層次。

1、系統層次:即控制系統的高層次

2023-04-19 16:41:43 542

542 如果你正在使用Vivado開發套件進行設計,你會發現綜合設置中提供了許多綜合選項。這些選項對綜合結果有著潛在的影響,而且能夠提升設計效率。為了更好地利用這些資源,需要仔細研究每一個選項的功能。本文將要介紹一下Vivado的綜合參數設置。

2023-05-16 16:45:50 1857

1857

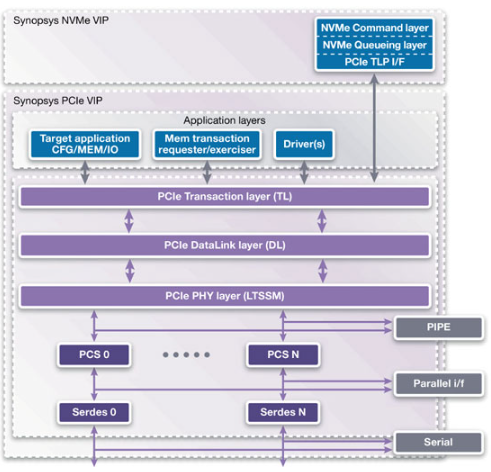

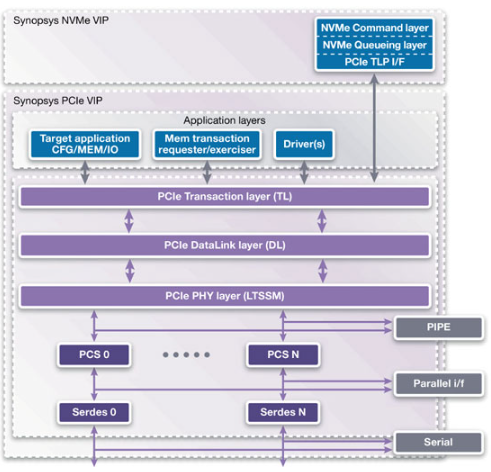

的 Synopsys NVMe 驗證 IP (VIP) 是一個綜合測試工具,由兩個主要子系統組成——第一個是 SVC(系統驗證組件),第二個是 SVT(系統驗證技術)。

2023-05-26 17:41:20 1080

1080

Vivado綜合默認是timing driven模式,除了IO管腳等物理約束,建議添加必要的時序約束,有利于綜合邏輯的優化,同時綜合后的design里面可以評估時序。

2023-07-03 09:03:19 414

414 這通常需要由工程師團隊編寫代碼(如Verilog、Chisel或C/C++等),然后在電子設計自動化(EDA)工具(如邏輯綜合或高層次綜合工具)的輔助下生成電路邏輯。

2023-07-03 11:16:48 784

784

電子發燒友網站提供《Vivado Design Suite用戶指南:綜合.pdf》資料免費下載

2023-09-13 15:47:40 0

0 電子發燒友網站提供《UltraFast高層次生產力設計方法指南.pdf》資料免費下載

2023-09-15 10:41:47 0

0 電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

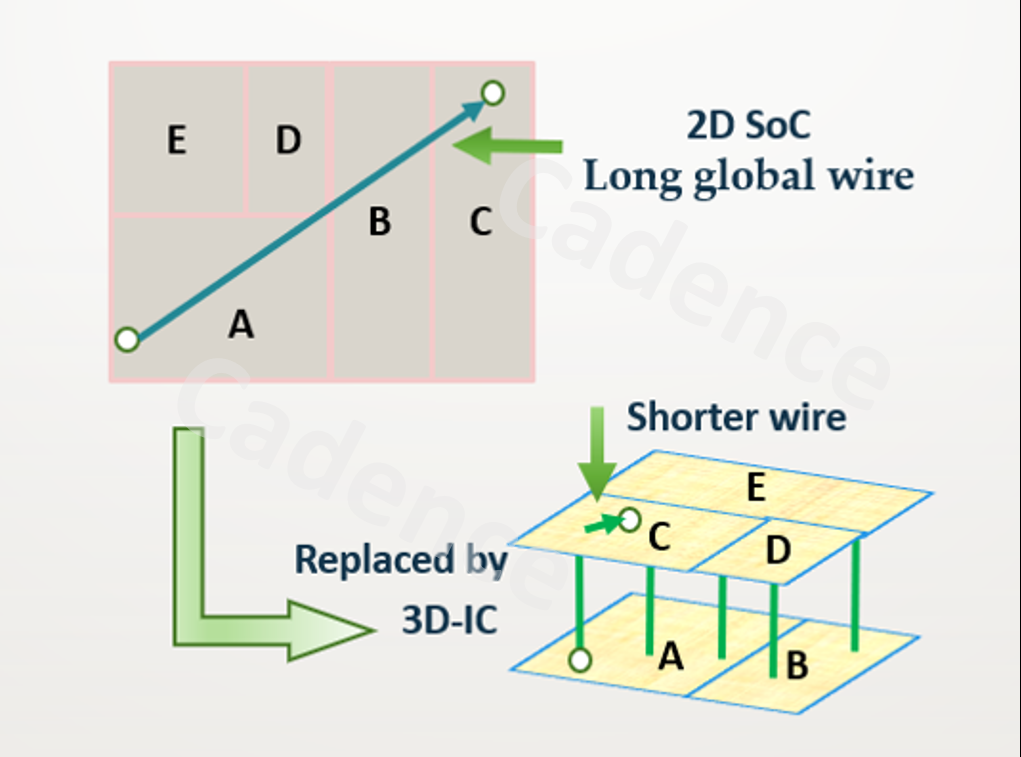

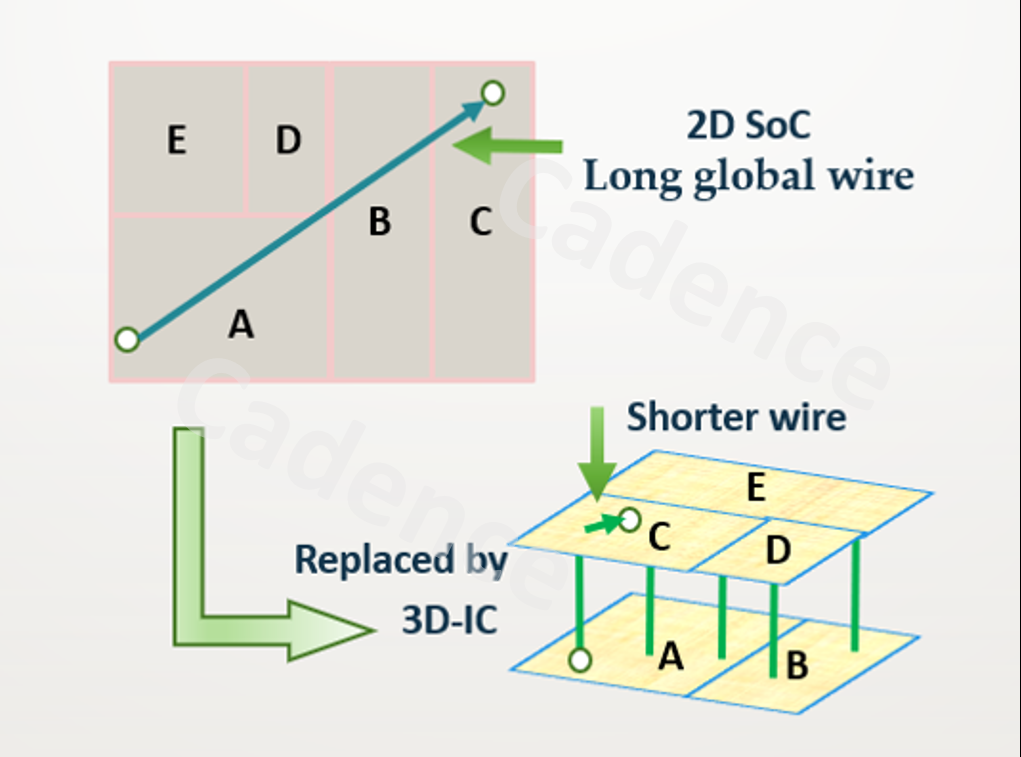

0 3D-IC 設計之早期三維布圖綜合以及層次化設計方法

2023-12-04 16:53:58 200

200

近日,中共南京市委人才工作領導小組發布了南京市“紫金山英才計劃高層次創新創業人才項目”評審結果,宙訊科技董事長周沖成為該項目入選人才。

2024-02-26 09:23:47 376

376

電子發燒友App

電子發燒友App

評論