在FPGA 上設計一個高性能、靈活的、面積小的通信體系結(jié)構(gòu)是一項巨大的挑戰(zhàn)。大多數(shù)基于FPGA 的片上網(wǎng)絡都是運行在一個單一時鐘下。隨著FPGA 技術的發(fā)展,Xilinx 公司推出了Virtex-4 平臺

2011-10-21 16:13:51 1270

1270

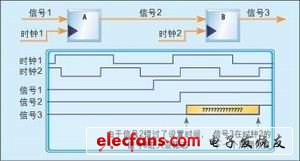

在多時鐘設計中可能需要進行時鐘的切換。由于時鐘之間可能存在相位、頻率等差異,直接切換時鐘可能導致產(chǎn)生glitch。

2020-09-24 11:20:38 5317

5317

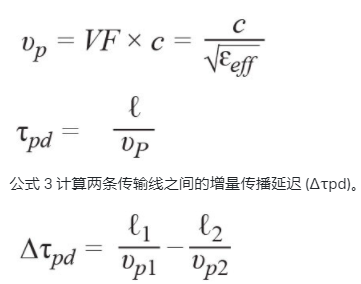

01、如何決定FPGA中需要什么樣的時鐘速率 設計中最快的時鐘將確定 FPGA 必須能處理的時鐘速率。最快時鐘速率由設計中兩個觸發(fā)器之間一個信號的傳輸時間 P 來決定,如果 P 大于時鐘周期

2020-11-23 13:08:24 3565

3565

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設計策略的基礎。 賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說

2021-02-13 17:02:00 2014

2014

。Xilinx FPGA7系列分為全局時鐘(Global clock)和局部時鐘(Regional clock)資源。目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發(fā)沿設計,對時鐘的周期

2023-07-24 11:07:04 655

655

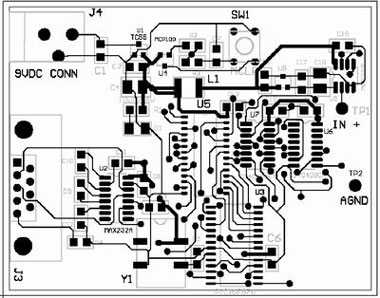

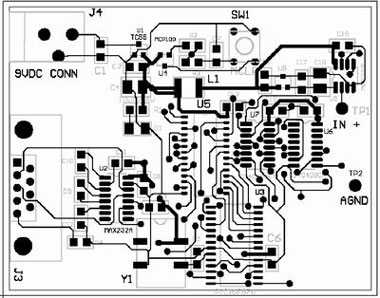

。在本文中,我們將討論自動布線功能的正確使用和錯誤使用,有無地平面時電流回路的設計策略,以及對雙面板元件布局的建議。

2023-09-26 09:41:54 389

389

有一個有趣的現(xiàn)象,眾多數(shù)字設計特別是與FPGA設計相關的教科書都特別強調(diào)整個設計最好采用唯一的時鐘域。

2023-12-22 09:04:46 875

875

本帖最后由 lee_st 于 2017-10-31 08:58 編輯

FPGA多時鐘設計

2017-10-21 20:28:45

大型設計中FPGA 的多時鐘設計策略Tim Behne 軟件與信號處理部經(jīng)理 Microwave Networks 公司Email: timothyb@microwavenetworks.com利用

2012-10-26 17:26:43

利用FPGA實現(xiàn)大型設計時,可能需要FPGA具有以多個時鐘運行的多重數(shù)據(jù)通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設計和時鐘/數(shù)據(jù)關系。設計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進行布線?

2019-08-30 08:31:41

摘要:FPGA異步時鐘設計中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個必須考慮的問題。本文介紹了FPGA異步時鐘設計中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時根據(jù)實踐經(jīng)驗給出了解決這些問題的幾種同步策略。關鍵詞

2009-04-21 16:52:37

FPGA的多時鐘系統(tǒng)設計 Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

EDA技術具有什么特征?FPGA是什么原理?FPGA設計應用及優(yōu)化策略基于VHDL的FPGA系統(tǒng)行為級設計

2021-04-15 06:33:58

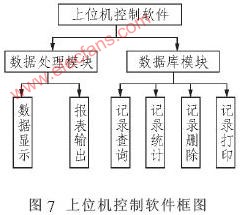

采用FPGA來設計一款廣泛應用于計算機、Modem、數(shù)據(jù)終端以及許多其他數(shù)字設備之間的數(shù)據(jù)傳輸?shù)膶S卯惒讲⑿型ㄐ沤涌谛酒瑢崿F(xiàn)了某一時鐘域(如66 MHz)的8位并行數(shù)據(jù)到另一低時鐘域(如40 MHz)16

2011-09-07 09:16:40

本帖最后由 mingzhezhang 于 2012-5-23 20:05 編輯

大型設計中FPGA的多時鐘設計策略 利用FPGA實現(xiàn)大型設計時,可能需要FPGA具有以多個時鐘運行的多重

2012-05-23 19:59:34

利用FPGA實現(xiàn)大型設計時,可能需要FPGA具有以多個時鐘運行的多重數(shù)據(jù)通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設計和時鐘/數(shù)據(jù)關系。設計過程中

2015-05-22 17:19:26

人工智能大熱之前,Cloud或Data Center已經(jīng)開始使用FPGA做各種加速了。而隨著Deep Learning的爆發(fā),這種需求越來越強勁。本文主要討論Cloud巨頭Amazon和Microsoft的FPGA策略。

2019-08-13 08:37:24

1、IC設計中的多時鐘域處理方法簡析我們在ASIC或FPGA系統(tǒng)設計中,常常會遇到需要在多個時鐘域下交互傳輸?shù)膯栴},時序問題也隨著系統(tǒng)越復雜而變得更為嚴重。跨時鐘域處理技術是IC設計中非常重要的一個

2022-06-24 16:54:26

利用 FPGA 實現(xiàn)大型設計時,可能需要FPGA 具有以多個時鐘運行的多重數(shù)據(jù)通路,這種多時鐘 FPGA 設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設計和時鐘/數(shù)據(jù)關系

2012-03-05 14:42:09

跨越時鐘域FPGA設計中可以使用多個時鐘。每個時鐘形成一個FPGA內(nèi)部時鐘域“,如果需要在另一個時鐘域的時鐘域產(chǎn)生一個信號,需要特別小心。隧道四部分第1部分:過路處。第2部分:道口標志第3部分:穿越

2012-03-19 15:16:20

目前高速PCB的設計在通信、計算機、圖形圖像處理等領域應用廣泛。而在這些領域工程師們用的高速PCB設計策略也不一樣。 在電信領域,設計非常復雜,在數(shù)據(jù)、語音和圖像的傳輸應用中傳輸速度已經(jīng)遠遠

2016-10-16 12:57:06

` 本帖最后由 gk320830 于 2015-3-4 14:11 編輯

世界十大設計團隊的經(jīng)典設計策略`

2013-09-13 19:44:35

本文就以太網(wǎng)保護設計方面提出設計策略以及幾種應對的設計思路,正如不同的標準中都有多個級別的防護等級,用戶需要根據(jù)實際的項目應用場景來選擇合適的方案,這包括PCB 設計、器件選擇、成本、信號一致性等

2020-12-28 06:35:21

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說

2020-04-25 07:00:00

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結(jié)構(gòu)是一項巨大的挑戰(zhàn)。大多數(shù)基于FPGA 的片上網(wǎng)絡都是運行在一個單一時鐘下。隨著FPGA 技術的發(fā)展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。

2019-09-18 08:26:21

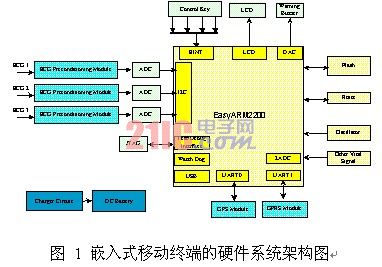

供電的便攜嵌入式系統(tǒng)電源設計都是有幫助的。根據(jù)本文描述的構(gòu)造模塊,讀者可以為特定設計選擇合適的器件以及設計策略。

2019-07-26 07:23:19

對多時鐘系統(tǒng)的同步問題進行了討論?提出了亞穩(wěn)態(tài)的概念及其產(chǎn)生機理和危害;敘述了控制信號和數(shù)據(jù)通路在多時鐘域之間的傳遞?討論了控制信號的輸出次序?qū)ν郊夹g的不同要求,重點論述了常用的數(shù)據(jù)通路同步技術----用FIFO實現(xiàn)同步的原理及其實現(xiàn)思路

2012-05-23 19:54:32

大型設計中FPGA的多時鐘設計策略利用FPGA實現(xiàn)大型設計時,可能需要FPGA具有以多個時鐘運行的多重數(shù)據(jù)通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘

2020-04-26 07:00:00

筆記本電腦的EMI設計策略

2009-08-16 13:39:19

。雖然這樣可以簡化時序分析以及減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時鐘常常又不現(xiàn)實。FPGA時常需要在兩個不同時鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收

2022-10-14 15:43:00

目前高速PCB的設計在通信、計算機、圖形圖像處理等領域應用廣泛。而在這些領域工程師們用的高速PCB設計策略也不一樣。 在電信領域,設計非常復雜,在數(shù)據(jù)、語音和圖像的傳輸應用中傳輸速度已經(jīng)遠遠

2018-11-27 10:15:02

Multiple Clock System Design PLD設計技巧—多時鐘系統(tǒng)設計

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 通過介紹BOVA 公司的產(chǎn)品設計實踐來認識客車產(chǎn)品的形象識別設計策略。關鍵詞: 客車; 產(chǎn)品形象識別; 設計策略Abstract: The article touches upon the bus p roduct identity design strategy th rough

2009-07-27 14:45:37 10

10 單片機系統(tǒng)的低功耗設計策略:摘要嵌入式系統(tǒng)的低功耗設計需要全面分析各方面因素,統(tǒng)籌規(guī)劃。在設計之初,各個因素往往是相互制約、相互影響的,一個降低系統(tǒng)功耗的措施有

2009-10-27 17:44:03 26

26 DLL在FPGA時鐘設計中的應用:在ISE集成開發(fā)環(huán)境中,用硬件描述語言對FPGA 的內(nèi)部資源DLL等直接例化,實現(xiàn)其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發(fā)板設計中的

2009-11-01 15:10:30 33

33 PLC控制系統(tǒng)抗干擾技術設計策略

自動化系統(tǒng)所使用的各種類型PLC中,有的是集中安裝在控制室,有的是安裝在生產(chǎn)現(xiàn)場和各電機設備上

2009-06-19 14:33:09 297

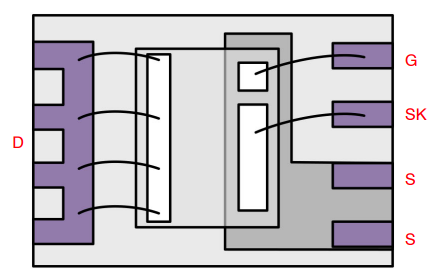

297 RFID芯片的攻擊技術分析及安全設計策略

本文以采用磁耦合和CMOS工藝的RFID產(chǎn)品為例,簡要介紹了此類芯片的構(gòu)成,在列舉各種破壞性/非破壞性攻擊手段的基礎上,從軟

2009-12-26 14:41:47 1205

1205 高可靠性嵌入式系統(tǒng)固件設計策略

本文針對如何編寫易理解、易維護的優(yōu)秀代碼進行了討論,為程序員提供了一些非常實用的編程指導。文中指出

2009-12-26 14:42:39 546

546 大型設計中FPGA的多時鐘設計策略

利用FPGA實現(xiàn)大型設計時,可能需要FPGA具有以多個時鐘運行的多重數(shù)據(jù)通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率

2009-12-27 13:28:04 645

645

便攜電子設備的高效電源系統(tǒng)設計策略

對于電池供電的便攜設備而言,除了需要突破處理能力的限制外,便攜式系統(tǒng)電源的性能也需要不斷改進。本文探討便攜嵌入式

2010-03-30 17:28:10 304

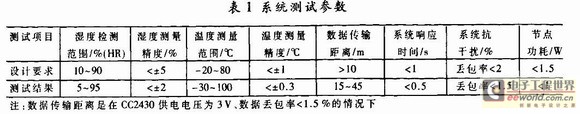

304 基于集成溫度傳感器的有源電子標簽設計策略

射頻識別RFID(Radio Frequency Identification)技術是近年來開始興起并逐漸走向成熟的一種自動識

2010-04-20 15:37:31 1045

1045

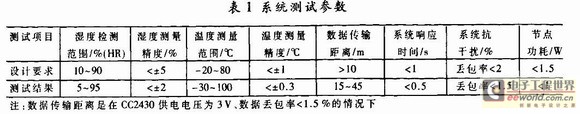

MSP430F149的無線環(huán)境監(jiān)測傳感器系統(tǒng)設計策略

微處理器模塊

C

2010-04-20 15:50:18 772

772

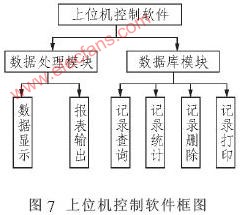

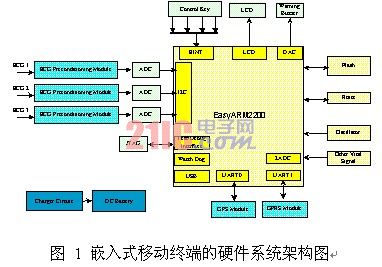

根據(jù)高危心臟病人遠程實時監(jiān)護系統(tǒng)設計策略

1 引言 心血管疾病發(fā)病往往十分危急,且病情嚴重、變化迅速,一旦發(fā)作就可能給病人帶來巨大痛苦、甚至導致暈

2010-04-21 09:46:13 853

853

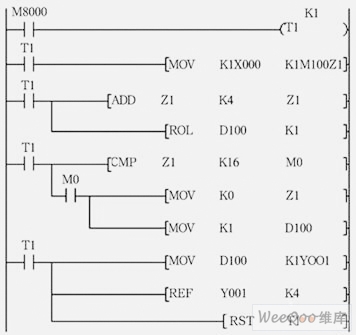

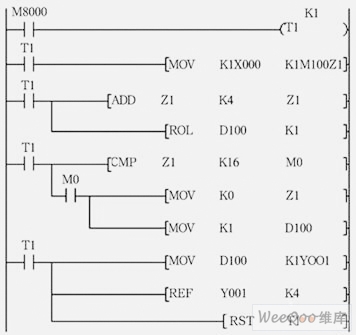

基于組掃描的PLC開關量采集方法設計策略

概 述:針對大量開關量信號輸入的問題,以日本三菱公司的fx系列plc為例,本文設計了一種基于組掃描輸入的plc開關量

2010-04-21 10:59:25 937

937

根據(jù)ZigBee的汽車空調(diào)控制系統(tǒng)設計策略

摘 要: 針對汽車空調(diào)系統(tǒng)的實時性要求,提出了一種基于ZigBee技術的汽車空

2010-04-21 16:50:21 864

864

根據(jù)TCP/IP的浮標網(wǎng)絡通信系統(tǒng)設計策略

水聲信道匹配基礎研究是建立在水聲學、海洋物理聲學以及現(xiàn)代信號處理技術基礎上的新興研究領域。為滿足研究需要而構(gòu)建的

2010-04-22 12:38:28 1752

1752

根據(jù)ARM的LCD觸摸屏系統(tǒng)設計策略

隨著嵌入式系統(tǒng)技術的飛速發(fā)展,工業(yè)設備產(chǎn)品也越來越現(xiàn)代化,普遍要求可視化操作。LCD觸摸屏低耗能.散熱小,成

2010-04-22 13:55:26 995

995

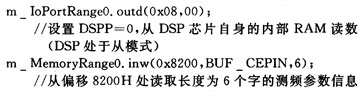

根據(jù)PCI總線的實時測頻卡WDM驅(qū)動程序設計策略

PCI總線是一種與CPU無關的32/64位地址數(shù)據(jù)復用總線,工作頻率為33 MHz/66 MHz,它支持突發(fā)傳輸,具有即插即用、電源管理等

2010-04-23 10:33:38 1269

1269

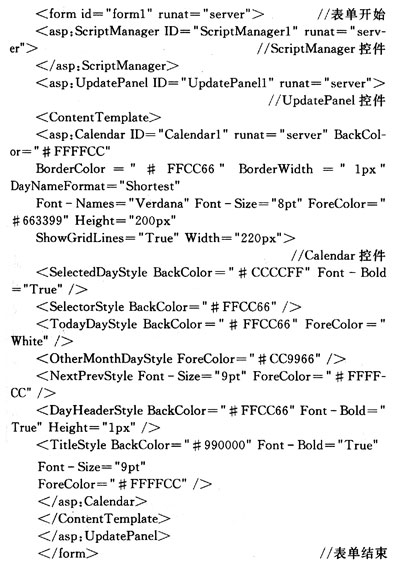

基于ASP.NET AJAX的OA系統(tǒng)設計策略0 引言辦公自動化(Office Automation,OA)系統(tǒng),是指利用計算機技術和網(wǎng)絡技術,使辦公室部分工作逐步物化于各種現(xiàn)代化設備中,由

2010-04-23 10:38:10 613

613

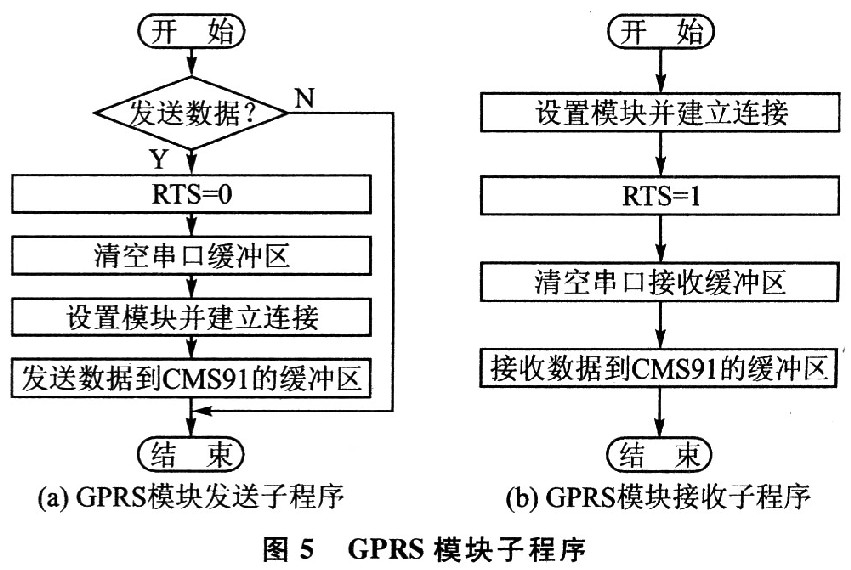

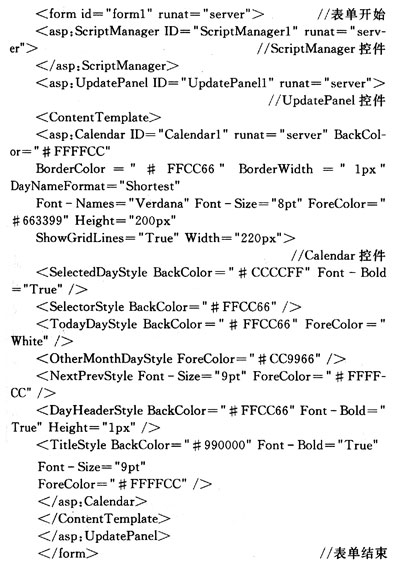

基于GPRS和PLC的遠程路燈監(jiān)控系統(tǒng)設計策略

1 GPRS技術簡介 GPRS(General Packet Radio Service,通用分組無線業(yè)務)是一種基于第二代移動通信系統(tǒng)GSM的無線分組

2010-04-23 11:29:55 952

952

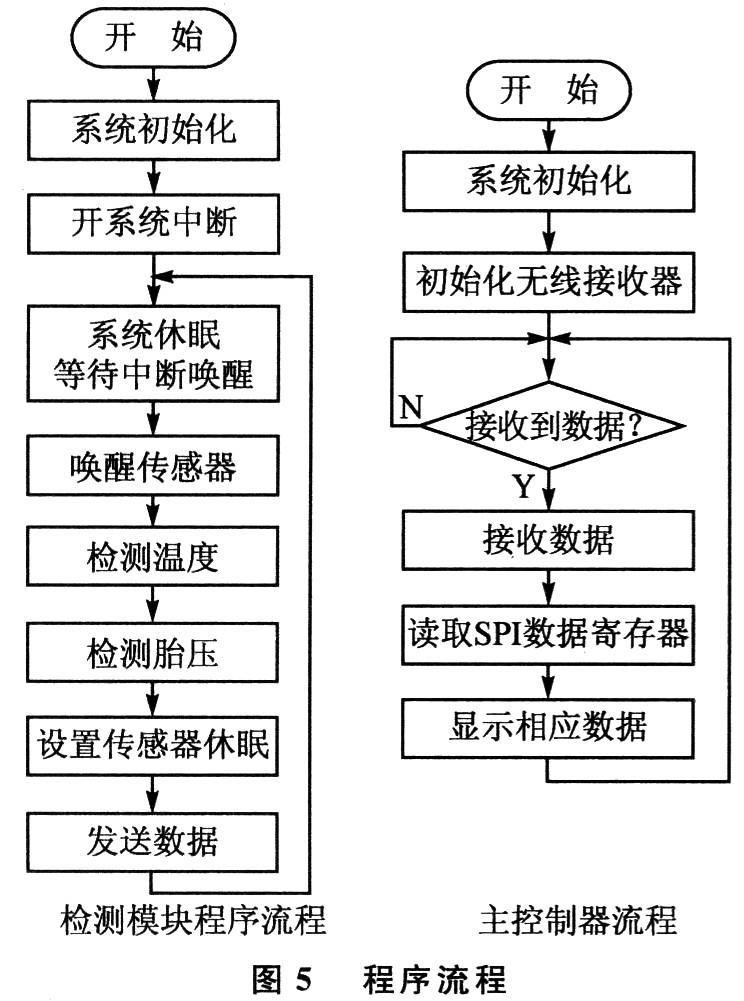

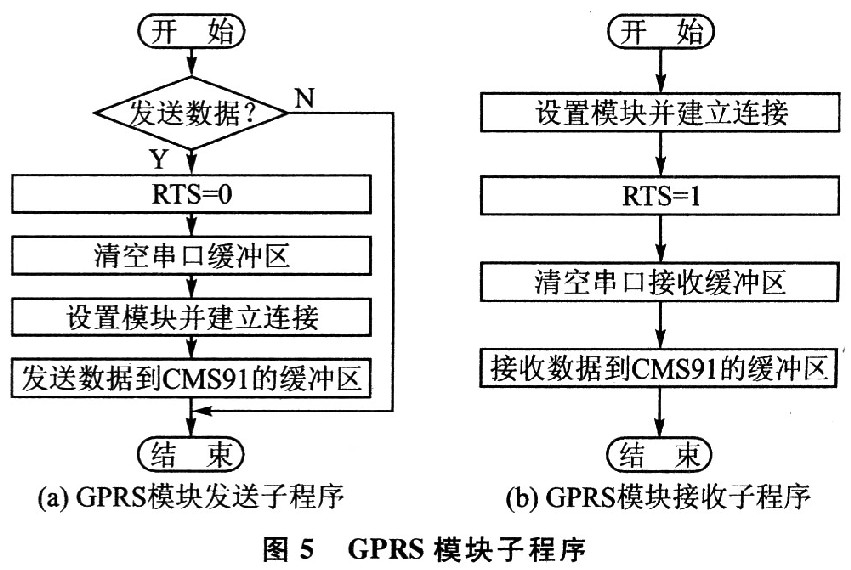

基于智能傳感器MPXY8320A的TPMS系統(tǒng)設計策略

1 TPMS系統(tǒng)的發(fā)展歷史和趨勢1.1 TPMS系統(tǒng)的發(fā)展歷史??? 國際市場,1997年,通用汽車公司開始使用間接式汽

2010-04-23 11:48:27 1097

1097

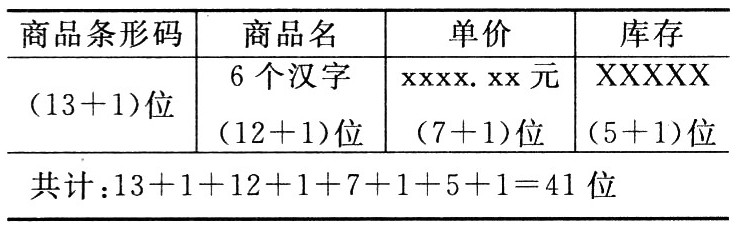

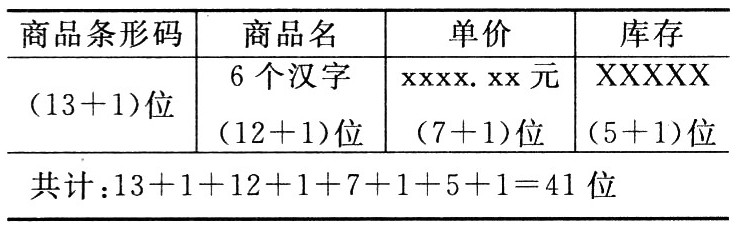

基于LPC2138的超市收銀機系統(tǒng)設計策略

ARM7 LPC2138介紹 Philips公司的32位的ARM7 LPC2138微控制器具有強大的存儲空間,內(nèi)嵌32 KB片內(nèi)靜態(tài)RAM和512KB的Flash

2010-04-23 11:50:36 3506

3506

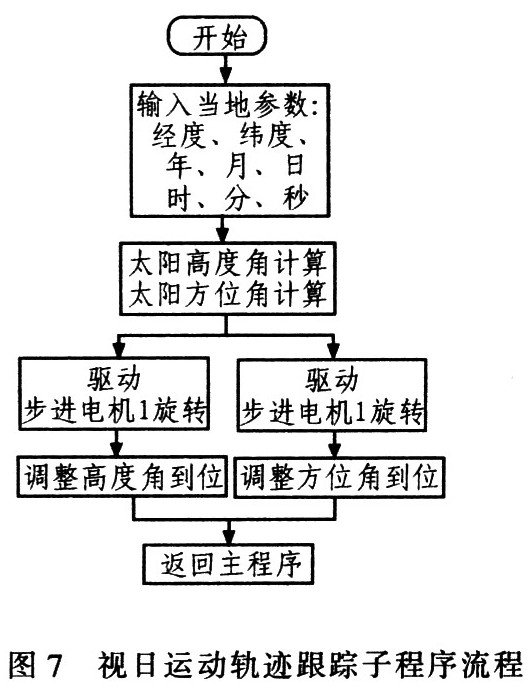

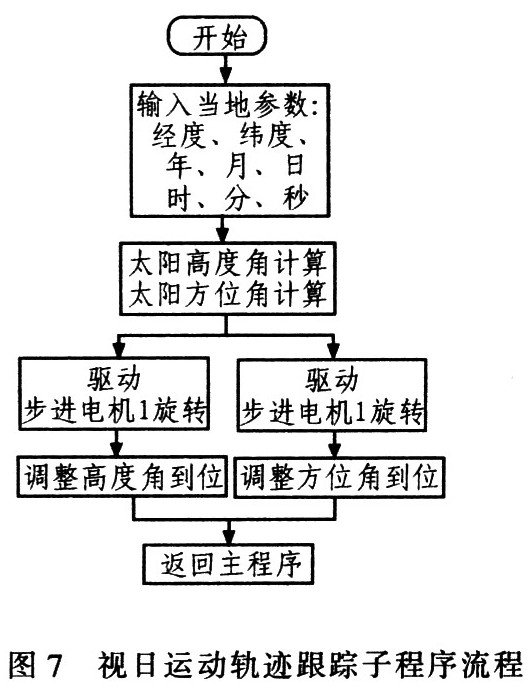

基于ATmega8的雙軸太陽跟蹤器設計策略

太陽能作為一種清潔能源,倍受人們重視,因此提高太陽能的利用率已成為研究熱點。理論分析表明:精確跟蹤與非跟蹤太

2010-04-23 14:07:01 2606

2606

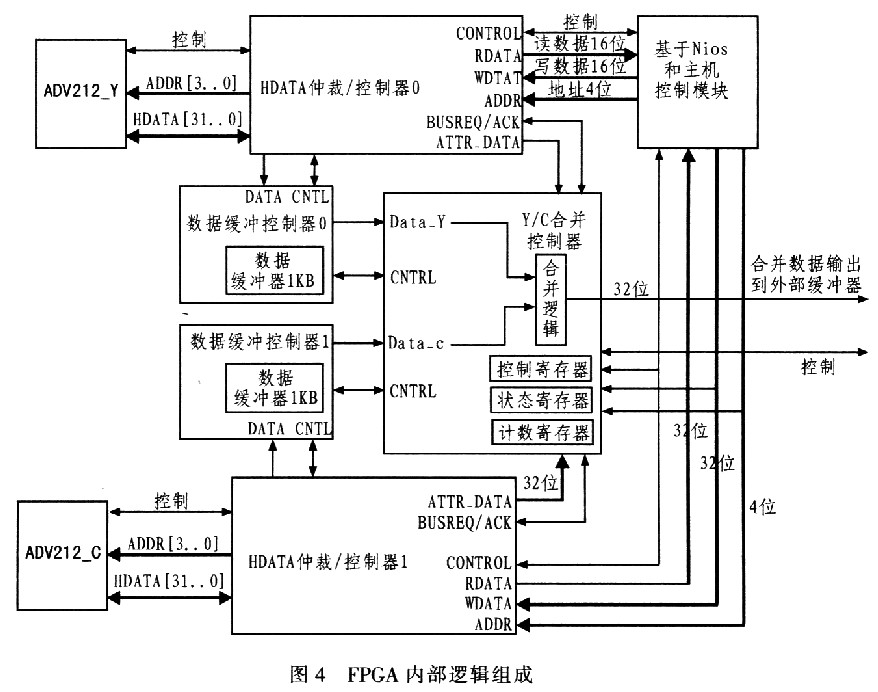

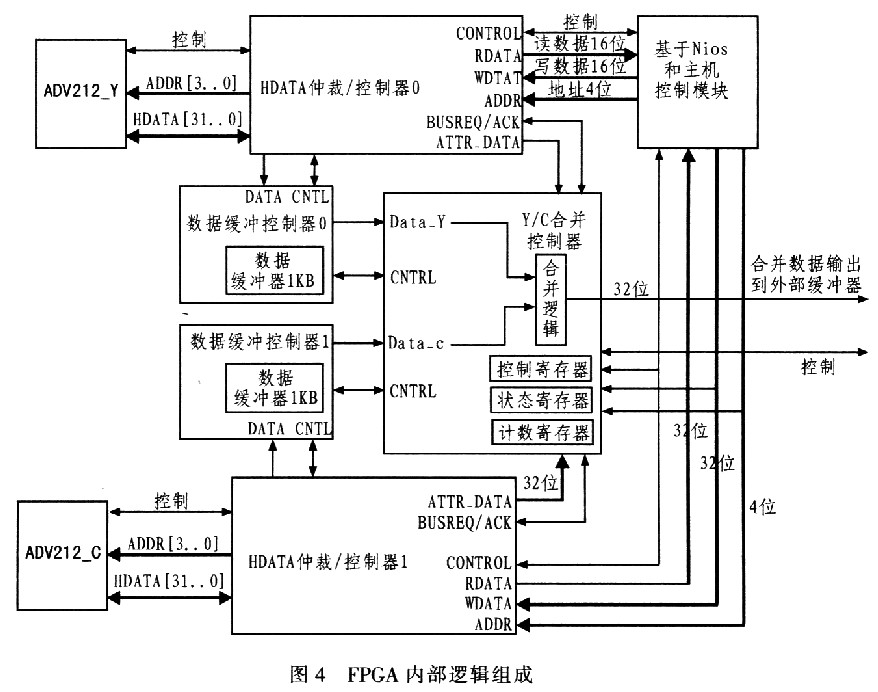

基于ADV212的高清視頻壓縮系統(tǒng)設計策略

隨著社會信息量的增大,人們對多媒體視頻壓縮的要求越來越高,“高壓縮、低比特速率”的高清視頻壓縮已廣泛應用于家用電

2010-04-23 14:15:36 2169

2169

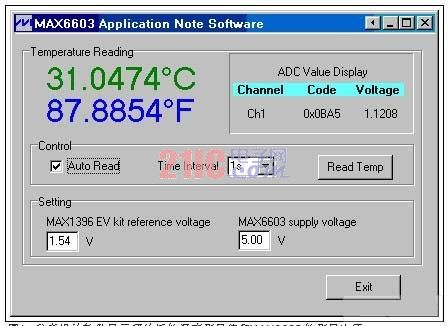

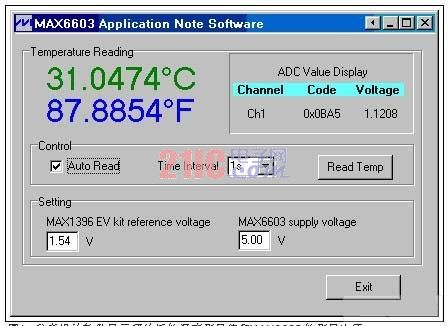

基于PC的溫度測量系統(tǒng)參考設計策略

引言

該參考設計提供了一個創(chuàng)建基于PC的溫度測量系統(tǒng)的方案,用于*估信號調(diào)理器MAX6603。該設計采用兩塊*估(EV)板:

2010-04-23 14:35:33 791

791

基于嵌入式系統(tǒng)的虛擬儀器的研究與設計策略

以工控計算機和PC為平臺的虛擬儀器系統(tǒng)長期以來充當著智能測試系統(tǒng)的平臺。隨著后PC時代的來臨,業(yè)界對儀

2010-04-23 14:40:44 1311

1311 安富利“ARM系統(tǒng)設計策略”研討會亞洲之旅6月28日北京啟動,安富利電子元件與ARM通力協(xié)作,在亞洲15個城市舉辦技術培訓。

2011-05-12 11:08:10 800

800 安富利全球“ARM系統(tǒng)設計策略”研討會亞洲之旅日前正式在北京國際會議中心拉開帷幕,共有1000名業(yè)內(nèi)人士參加了此次研討會,場面盛大,與會者反響熱烈,彰顯了業(yè)界對針對ARM系統(tǒng)的

2011-06-30 08:59:55 612

612 分析了變頻調(diào)速異步電動機的工作狀態(tài)和在電機設計中需要考慮的特殊點,提出了變頻調(diào)速異步電動機的設計策略

2011-08-26 14:24:28 49

49 在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 3472

3472

基于AD9540產(chǎn)生多時鐘輸出

2011-11-25 00:02:00 31

31 FPGA 異步時鐘設計中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個必須考慮的問題。本文介紹了FPGA 異步時鐘設計中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時根據(jù)實踐經(jīng)驗給出了解決這些問題的

2011-12-20 17:08:35 63

63 2014-06-20 10:30:15 21

21 DLL在_FPGA時鐘設計中的應用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現(xiàn)的。

2015-10-28 14:25:42 1

1 FPGA學習資料,有興趣的同學可以下載看看。

2016-04-07 16:33:47 0

0 基于改進模糊卡爾曼濾波的感應電機轉(zhuǎn)速估計策略研究_王鑫博

2017-01-08 11:20:20 1

1 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發(fā)沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅(qū)動設計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-02-11 11:34:11 4223

4223 在一個SOC設計中,存在多個、獨立的時鐘,這已經(jīng)是一件很平常的事情了。大多數(shù)的SOC器件都具有很多個接口,各個接口標準都可能會使用完全不同的時鐘頻率。

2017-02-11 15:07:11 1047

1047 很大。 在設計PLD/FPGA時通常采用幾種時鐘類型。時鐘可分為如下四種類型:全局時鐘、門控時鐘、多級邏輯時鐘和波動式時鐘。多時鐘系統(tǒng)能夠包括上述四種時鐘類型的任意組合。

2017-11-25 09:16:01 3907

3907

基于FPGA的數(shù)字系統(tǒng)設計中大都推薦采用同步時序的設計,也就是單時鐘系統(tǒng)。但是實際的工程中,純粹單時鐘系統(tǒng)設計的情況很少,特別是設計模塊與外圍芯片的通信中,跨時鐘域的情況經(jīng)常不可避免。如果對跨時鐘

2018-09-01 08:29:21 5302

5302

跨時鐘域問題(CDC,Clock Domain Crossing )是多時鐘設計中的常見現(xiàn)象。在FPGA領域,互動的異步時鐘域的數(shù)量急劇增加。通常不止數(shù)百個,而是超過一千個時鐘域。

2019-08-19 14:52:58 2854

2854 時鐘是FPGA設計中最重要的信號,FPGA系統(tǒng)內(nèi)大部分器件的動作都是在時鐘的上升沿或者下降沿進行。

2019-09-20 15:10:18 5065

5065

有一個有趣的現(xiàn)象,眾多數(shù)字設計特別是與FPGA設計相關的教科書都特別強調(diào)整個設計最好采用唯一的時鐘域。

2020-09-24 10:20:00 2487

2487

利用 FPGA 實現(xiàn)大型設計時,可能需要FPGA 具有以多個時鐘運行的多重數(shù)據(jù)通路,這種多時鐘FPGA 設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設計和時鐘/數(shù)據(jù)關系。設計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進行布線,本文將對這些設計策略深入闡述。

2021-01-13 17:00:00 11

11 利用 FPGA 實現(xiàn)大型設計時,可能需要FPGA 具有以多個時鐘運行的多重數(shù)據(jù)通路,這種多時鐘FPGA 設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設計和時鐘/數(shù)據(jù)關系。設計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進行布線,本文將對這些設計策略深入闡述。

2021-01-15 15:57:00 14

14 AN-769: 基于AD9540產(chǎn)生多時鐘輸出

2021-03-18 23:03:12 2

2 引言:從本文開始,我們陸續(xù)介紹Xilinx 7系列FPGA的時鐘資源架構(gòu),熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 4326

4326 減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時鐘常常又不現(xiàn)實。 FPGA時常需要在兩個不同時鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時鐘的低功耗

2021-05-10 16:51:39 3719

3719

減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時鐘常常又不現(xiàn)實。FPGA時常需要在兩個不同時鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時鐘的低功耗

2021-09-23 16:39:54 2763

2763 (29)FPGA原語設計(差分時鐘轉(zhuǎn)單端時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(差分時鐘轉(zhuǎn)單端時鐘)5)結(jié)語1.2 FPGA簡介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原語設計(單端時鐘轉(zhuǎn)差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(單端時鐘轉(zhuǎn)差分時鐘)5)結(jié)語1.2 FPGA簡介FPGA

2021-12-29 19:41:48 10

10 ?xilinx 的 FPGA 時鐘結(jié)構(gòu),7 系列 FPGA 的時鐘結(jié)構(gòu)和前面幾個系列的時鐘結(jié)構(gòu)有了很大的區(qū)別,7系列的時鐘結(jié)構(gòu)如下圖所示。

2022-07-03 17:13:48 2592

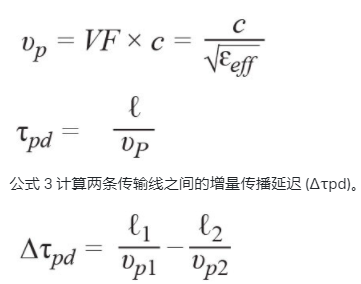

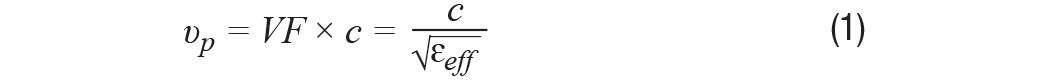

2592 本文確定了設計過程、制造過程和應用環(huán)境中可能導致 1 ps 或更多時鐘偏移的幾個關注領域。關于這些關注領域,將提供一些建議、示例和經(jīng)驗法則,以幫助讀者直觀地了解時鐘偏差錯誤的根本原因和幅度。

2022-07-05 10:17:51 901

901

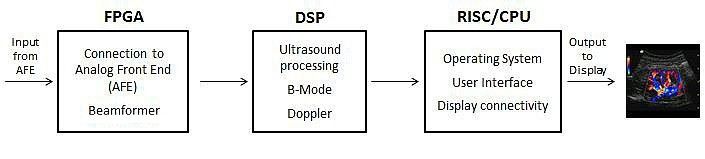

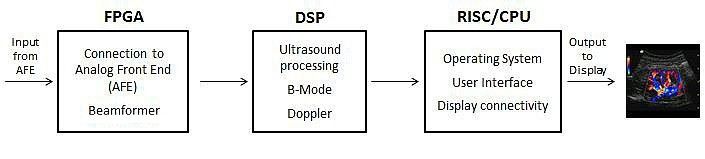

與關注處理器以說明產(chǎn)品其余部分的設計實踐類似,終端設備的重點將是便攜式醫(yī)療成像設備,例如手持式超聲設備。與大多數(shù)便攜式醫(yī)療系統(tǒng)相比,這需要更多的處理,但許多設計策略仍然具有相關性。

2022-10-26 15:08:55 801

801

電子發(fā)燒友網(wǎng)站提供《大型自調(diào)時鐘開源分享.zip》資料免費下載

2022-11-01 11:03:32 0

0 大型時鐘樹通過多個時鐘設備、使用多種傳輸線類型以及跨多個板和同軸電纜路由時鐘信號的情況并不少見。即使遵循最佳實踐,這些介質(zhì)中的任何一種都可能引入大于 10 ps 的時鐘偏差。但是,在某些應用中,希望

2022-12-22 15:19:31 628

628

減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時鐘常常又不現(xiàn)實。FPGA時常需要在兩個不同時鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時鐘的低功耗

2023-08-23 16:10:01 336

336 干貨 | 氮化鎵GaN驅(qū)動器的PCB設計策略概要

2023-09-27 16:13:56 484

484

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設計人員在他們的FPGA設計中或多或少都會用到。

2023-10-30 11:47:55 523

523

電子發(fā)燒友網(wǎng)站提供《大型多GHz時鐘樹中的相位偏差設計.pdf》資料免費下載

2023-11-22 16:56:01 0

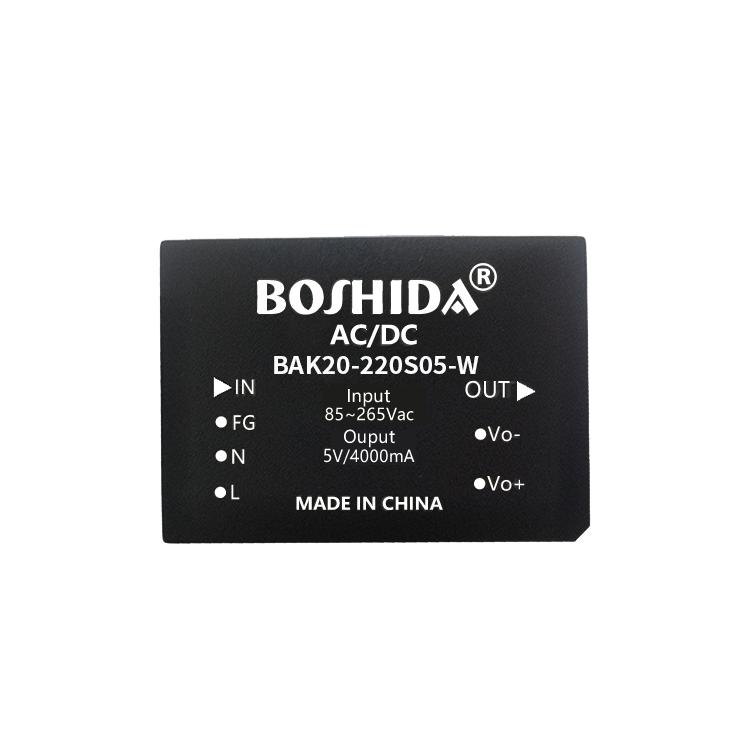

0 BOSHIDA DC電源模塊的節(jié)能與環(huán)保設計策略 DC電源模塊的節(jié)能與環(huán)保設計策略可以從以下幾個方面考慮: DC電源模塊的節(jié)能與環(huán)保設計策略 1. 高效率設計:設計高效率的電源轉(zhuǎn)換器可以減少能量損耗

2024-02-18 14:23:17 77

77

電子發(fā)燒友App

電子發(fā)燒友App

評論