隨著工藝技術(shù)的發(fā)展與市場需求,超大規(guī)模、高速、低功耗的新型現(xiàn)場可編程邏輯器件(FPGA)不斷推出,給電路設(shè)計帶來極大的方便。在采用大規(guī)模FPGA的開發(fā)系統(tǒng)中,供電模塊的設(shè)計將直接影響到系統(tǒng)的穩(wěn)定性,因此設(shè)計出高效、穩(wěn)定的供電模塊顯得尤為重要。本文以可擴展網(wǎng)絡(luò)交換調(diào)度系統(tǒng)的FPGA驗證平臺為例,介紹FPGA供電模塊的設(shè)計方法。

目前,F(xiàn)PGA、DSP等芯片的電源供電方案主要有三種:低壓差線性穩(wěn)壓器(LDO)、電源模塊和開關(guān)穩(wěn)壓電源。其中采用集成FET的稱為DC/DC調(diào)整器,采用非集成FET的稱為DC/DC控制器。

LDO的基本原理是根據(jù)負載電阻的變化情況調(diào)節(jié)自身的內(nèi)阻,從而保證穩(wěn)壓器輸出端的電壓不變,因此LDO只適用于降壓變換。其具體效果與輸入/輸出電壓比有關(guān),變換效率可以簡單地看作輸出與輸入電壓之比。由于采用線性調(diào)節(jié)原理,瞬態(tài)特性好。LDO本質(zhì)上沒有輸出紋波,但隨著LDO的輸入/輸出電壓差別增大或者輸出電流增加,LDO的發(fā)熱比會成比例增大,所以在散熱控制方面要求很高。LDO穩(wěn)壓器為電流輸出要求較低的應(yīng)用提供了體積小且廉價的解決方案。

DC/DC調(diào)整器利用了磁場儲能,無論升壓、降壓或是兩者同時進行,都可以實現(xiàn)相當高的變換效率。由于變換效率高,因此發(fā)熱很小,散熱處理得以簡化,所以DC/DC調(diào)整器一般不再需要附加一個成本較高、面積較大的散熱器。考慮到DC/DC調(diào)整器集成有FET,使用時只需外接一個電感和必不可少的輸入電容和輸出電容,故可以使整個解決方案的空間利用率大大提高,尤其對于需要大電流的FPGA來說十分理想。由于是開關(guān)穩(wěn)壓器電源,與LDO相比,DC/DC調(diào)整器輸出紋波電壓較大、瞬時恢復(fù)時間較慢、容易產(chǎn)生電磁干擾(EMI)。要取得低紋波、低EMI、低噪聲的電源,關(guān)鍵在于電路設(shè)計,尤其是輸入/輸出電容、輸出電感的選擇和布局。DC/DC調(diào)整器占用面積較大。

DC/DC控制器和DC/DC調(diào)整器的差別主要是沒有內(nèi)置的FET。因此,設(shè)計者可以選用有特定導通電阻的外接FET晶體管,并根據(jù)應(yīng)用的需要調(diào)整電流,使設(shè)計具有很大的靈活性,這在需要十幾甚至幾十安培電流的特大規(guī)模FPGA開發(fā)系統(tǒng)中非常有用。與DC/DC調(diào)整器相比,采用這種方案設(shè)計,既要選擇適當?shù)妮斎腚娙?輸出電容、輸出電感,又要選擇符合要求的FET,增加了設(shè)計難度和總成本。此外,由于FET外置,占用空間也相對較大。

電源模塊從原理上來說是個開關(guān)穩(wěn)壓器,所以它的效率非常高。相對于普通開關(guān)穩(wěn)壓器,它的集成度更高,因此外圍只需要一個輸入電容和一個輸出電容即可工作,設(shè)計簡便,適合要求開發(fā)周期非常短的應(yīng)用。它一般以可插拔的形式給出。由于電源模塊上集成了幾乎所有可以集成的東西,靈活性相對較差,價格也相對較高。

1 器件選型與功能介紹

本文中的交換調(diào)度系統(tǒng)的FPGA驗證平臺采用4片Xilinx VirtexII FPGA作為網(wǎng)絡(luò)包調(diào)度器實現(xiàn)可擴展的交換調(diào)度功能,其中VirtexII的核心電壓VCCINT為1.5V,輔助電壓VCCAUX和輸出驅(qū)動電壓VCCO均為3.3V。由于需要對4片F(xiàn)PGA供電,電源板面積較大。為了調(diào)試方便,對整個供電電路采用單獨設(shè)計制板,根據(jù)器件和系統(tǒng)的要求,本設(shè)計采用DC/DC調(diào)整器方案。

采用DC/DC調(diào)整器的供電方案雖然有多種,但考慮到每個供電模塊需要對兩片F(xiàn)PGA供電,而且通過仿真估算出的每片F(xiàn)PGA的最大電流為2A左右,加上一定的裕量,因此需要單個供電模塊最大能夠提供6A左右的電流。

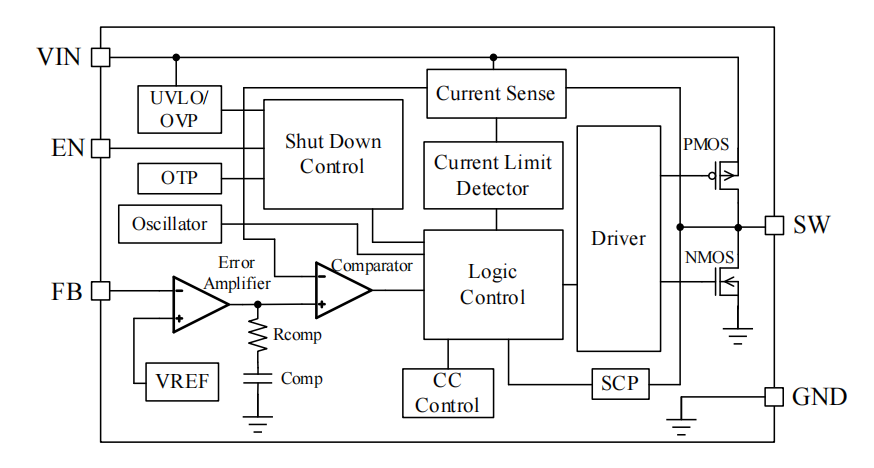

TPS54610是TI公司專門為DSP、ASIC和FPGA等多芯片系統(tǒng)供電而設(shè)計的一款低電壓輸入、大電流輸出的同步降壓DC/DC調(diào)整器,內(nèi)含30MΩ、12A峰值電流的MOSFET開關(guān)管,最大可輸出6A電流。輸出電壓從0.9V到3.3V可調(diào),誤差率為1%。開關(guān)頻率可固定在350kHz或550kHz,也可以在280kHz到700kHz之間調(diào)整。另外,它還具有限流電路、低壓閉鎖電路和過熱關(guān)斷電路。而且TPS54610的集成化設(shè)計又減少了元件數(shù)量和體積,因此,可廣泛用于低電壓輸入、大電流輸出的分散電源系統(tǒng)中。經(jīng)過分析,采用兩片TPS54610為兩片F(xiàn)PGA供電的方案。

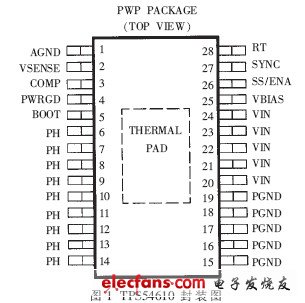

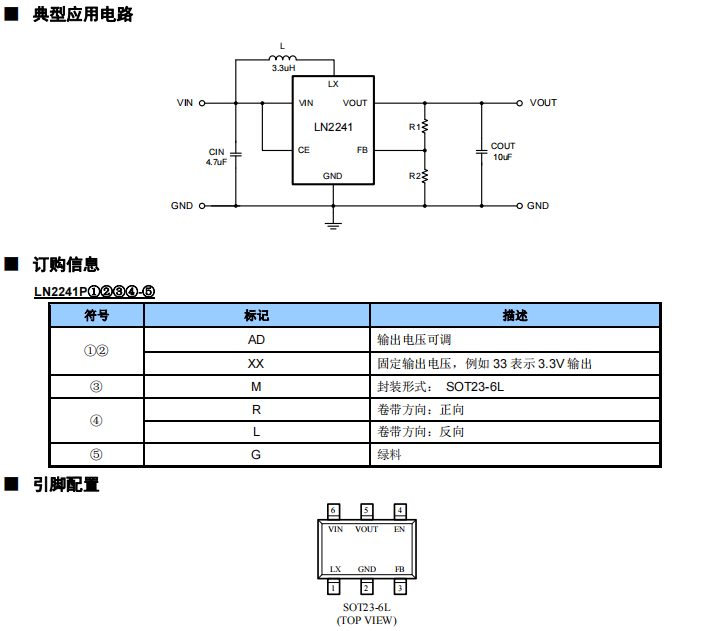

TPS54610采用28腳TSSOP封裝,其引腳排列如圖1所示。各引腳功能如下:

·AGND(1腳):模擬地。

·VSENSE(2腳):誤差放大反饋輸入,通過補償網(wǎng)絡(luò)/輸出分壓器連接輸出電壓。

·COMP(3腳):誤差放大器輸出,COMP腳與VSENSE腳間應(yīng)接頻率補償電路。

·PWRGD(4腳):當VSENSE端的電壓高于Vref的90%時,輸出為高,否則為低。

·BOOT(5腳):自舉電路輸出,在BOOT腳和PH腳之間應(yīng)連接0.022μF~0.1μF的電容。

·PH(6~14腳):相輸出,功率MOSFET高低端與輸出電感的連接點。

·PGND(15~19腳):電源地,使用時應(yīng)與AGND單點連接。

·VIN(20~24腳):電源輸入,與PGND間應(yīng)連接10μF的電容。

·VBIAS(25腳):內(nèi)部偏壓調(diào)節(jié),與AGND引腳間應(yīng)接一個0.1μF~1μF的陶瓷電容。

·SS/ENA(26腳):軟啟動/輸入輸出使能端,可提供控制器允許工作邏輯信號。 該腳的另一個功能是通過外接電容設(shè)置軟啟動時間。

·SYNC(27腳):同步輸入,可提供外部振蕩器同步邏輯信號,此時要求RT引腳必須連接一個電阻,在內(nèi)部振蕩時用于開關(guān)頻率的切換。

·RT(28腳):頻率設(shè)置電阻輸入,在RT和AGND間連接一個電阻可以設(shè)置開關(guān)頻率, 當使用SYNC端時, 通過RT設(shè)置的頻率應(yīng)稍低于外部振蕩器的頻率。

2 電路設(shè)計

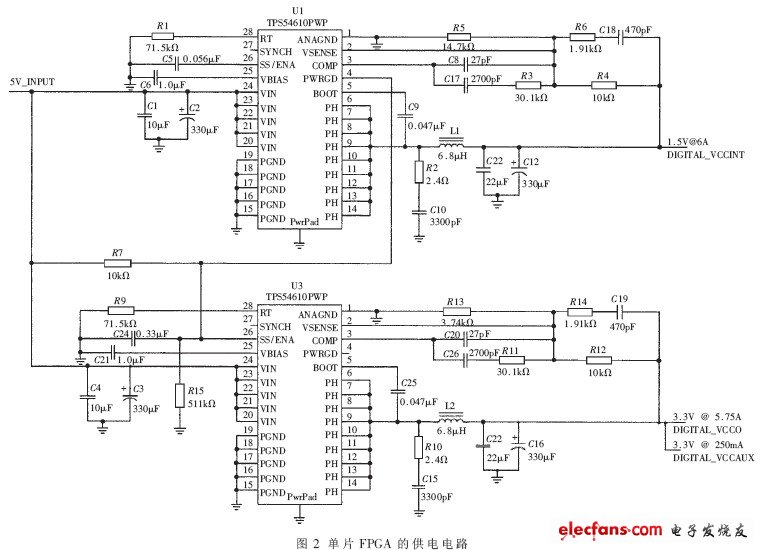

圖2所示為兩片F(xiàn)PGA的供電電路,其中的一片TPS54610提供兩片F(xiàn)PGA的VCCINT電壓,另一片TPS54610給兩片F(xiàn)PGA的VCCAUX和VCCO供電。設(shè)計該電路時主要應(yīng)考慮輸入輸出濾波、反饋電路以及開關(guān)頻率的選擇等方面。

2.1 輸入輸出濾波

電路的輸入為5V直源電源,輸入濾波電容C2(C3)為330μF,可減少輸入波紋電壓。輸入旁路電容C1(C4)為10μF,可有效地去除輸入電壓中的高頻分量,這幾個電容制版時都要盡可能靠近芯片。輸出濾波網(wǎng)絡(luò)由6.8μH的電感L1(L2)與22μF的電容C11(C22)和330μF的電容C12(C16)組成。

2.2 補償網(wǎng)絡(luò)

圖2中的R4、R5組成的分壓網(wǎng)絡(luò)使輸出的VCCINT電壓為1.5V,R12、R13組成的分壓網(wǎng)絡(luò)使輸出的VCCO電壓為3.3V。R4(R12)、R3(R11)、R6(R14)、C8(C20)、C17(C26)與C18(C19)形成了電路的環(huán)路補償網(wǎng)絡(luò)。這些元器件的選取方法很多,本設(shè)計中主要考慮其穩(wěn)定性和較寬的帶寬。補償電路的設(shè)計首先應(yīng)考慮補償誤差放大器的增益不被限制。其次,補償誤差放大器應(yīng)將COMP引腳的波紋電壓降到100mV左右。另外,電路總的回路串擾頻率應(yīng)小于開關(guān)頻率的1/8,同時相角裕量至少應(yīng)為45°。通過圖中補償元件的參數(shù)設(shè)計可將總的回路響應(yīng)串擾頻率范圍限制在10kHz~70kHz之間,相位裕量范圍設(shè)定在60°~90°之間,同時圖中各電阻的偏差應(yīng)小于1%,電容偏差應(yīng)小于10%。

2.3 開關(guān)頻率的選擇

TPS54610的開關(guān)頻率在280kHz~700kHz之間是可調(diào)節(jié)的。當SYNC引腳接地時,開關(guān)頻率為350kHz,當SYNC接輸入電源電壓時,開關(guān)頻率為550kHz。當RT和AGND之間接180kΩ~68kΩ的電阻時,可以在280kHz~700kHz之間調(diào)節(jié)開關(guān)頻率,其中電阻R的計算公式為 ,這時,SYNCH腳應(yīng)斷開。開關(guān)頻率的選擇要考慮轉(zhuǎn)換效率和元件尺寸,較高的工作頻率允許使用較低數(shù)值的電感和電容,反之,則因減少了內(nèi)部開關(guān)損失而提高效率,但需較大的電感和電容以降低輸出紋波。本設(shè)計將開關(guān)頻率選定為最高的700kHz,此時,通過計算可得R1為71.5kΩ。

偏置電容C6和C21采用1.0μF的陶瓷電容,連接到VBIAS腳和AGND腳之間,自舉電容C9和C25采用0.047μF的陶瓷電容,連接到BOOT腳和PH腳之間。2.4 軟啟動及系統(tǒng)使能

SS/ENA腳有兩個功能:一是作為使能信號控制芯片的關(guān)閉或啟動,啟動閾值電壓大約為1.2V。缺省時,芯片處于關(guān)閉狀態(tài),直到SS/ENA的電壓超過閾值電壓時,芯片開始啟動。TPS54610內(nèi)部慢啟動時間為3.35ms,反饋到誤差放大器的基準電壓在3.35ms內(nèi)從0V線性上升到0.891V,同樣地,芯片的輸出電壓在3.35ms內(nèi)上升到穩(wěn)定值。

另一個功能是通過與AGND腳之間連接的一個小電容Css設(shè)置啟動時延td及軟啟動時間tss。其中,啟動時延td的大小與Css的大小是成比例的,即td=Css×1.2V/5μA,軟啟動時間即輸出電壓的上升時間tss的調(diào)整是通過公式 tss=Css×0.7V/5μA進行的。

因此,在為VCCINT供電的TPS54610芯片的SS/ENA腳外接一個0.056μF的電容C5,為VCCAUX和VCCO供電的TPS54610芯片的SS/ENA腳接0.33μF的C24后,外加5V電壓時,0.013ms后為VCCINT供電的TPS54610芯片開始啟動,經(jīng)過0.0078ms后,輸出VCCINT穩(wěn)定為1.5V。此時,PWRGD引腳輸出為高電平,為VCCAUX和VCCO供電的TPS54610芯片SS/ENA腳為高電平,0.079ms后該芯片開始啟動,經(jīng)過0.046ms后,VCCAUX和VCCO的輸出達到穩(wěn)定的3.3V。當VCCINT輸出的電壓低于1.35V(即正常值的90%)時,PWRGD腳輸出為低電平,使得為VCCAUX和VCCO供電的TPS54610芯片的SS/ENA腳為低電平,此時芯片關(guān)閉,VCCAUX和VCCO輸出為0。

該電路的PCB設(shè)計采用雙層板設(shè)計。首先進行整體布局,布局時要考慮PCB的形狀和尺寸。通常,電路板的最佳形狀為矩形,PCB尺寸過大時,印制線條長,阻抗增加,抗噪聲能力下降,成本也增加;而PCB尺寸過小時,散熱不好,且鄰近線條易受干擾。由于設(shè)計的PCB板上有由4片TPS54610 和2片TPS79425組成的兩個供電單元,根據(jù)芯片尺寸,本次設(shè)計的尺寸為149.8mm×70.47mm。

確定了PCB的尺寸后,先要確定特殊元件的位置,再根據(jù)電路的功能單元,對電路中的全部元器件進行布局。其中,需注意以下幾點:①易受干擾的元器件不能相互挨得太近,輸入和輸出元件應(yīng)盡量遠離,熱敏元件應(yīng)遠離發(fā)熱元件;②對于電位器、可調(diào)電感線圈、可變電容器、微動開關(guān)等可調(diào)元件應(yīng)放在印制板上方便于調(diào)節(jié)的地方;③應(yīng)留出印制板定位孔及固定支架所占用的位置。在本設(shè)計中,輸入的+5V電壓源插座位于板子的上方,輸出插座位于板子的左右兩側(cè),兩個供電單元呈中心對稱分布,距離適當。布局時需要對所選用元件器及各種插座的規(guī)格、尺寸、面積等有完全的了解,對各部件的位置安排作合理、仔細考慮,主要應(yīng)從電磁場兼容性、抗干擾、走線短、交叉少、電源和地的路徑及去耦等方面考慮。位于電路板邊緣的元器件與電路板邊緣距離一般不小于2mm。

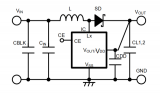

圖3所示為TPS54610的PCB線路連接模型。可以看到,輸入電壓腳VIN都連在一起,通過輸入旁路電容C1與PGND(電源地)相連,C1為低等效串聯(lián)電阻陶瓷電容。為了減少噪聲的影響,PCB設(shè)計時C1、C2應(yīng)盡可能靠近VIN和PGND腳。

TPS54610有兩個地,即電源地PGND和模擬地AGND。電源地連接嘈雜的功率信號,模擬地連接所有噪聲敏感信號。兩個地之間一旦注入噪聲就會降低TPS54610的性能,還會引起控制信號和偏置出現(xiàn)問題,尤其在高速電路中表現(xiàn)得尤為明顯。因此,通常將電源地與模擬地分開布線,并在一點上相連。用一個單獨的比較寬的導線作為模擬地,它連接頻率設(shè)置電阻R1,慢啟動電容C3和偏置電容C4的接地端,并與TPS54610的AGND腳相連。

為了解決TPS54610芯片的散熱問題,在其底面有一塊暴露的PowerPAD區(qū)(見圖3中的PowerPAD),制作PCB板時應(yīng)將它與頂層地相接并用過孔將頂層地與PCB的地相連。過孔還可以用在輸入和輸出濾波電容的接地端。直接連接到電源地上的器件只有輸入濾波電容和旁路電容、輸出濾波電容和PGND腳。

PH腳與輸出電感L1相連,由于連接電路是開關(guān)節(jié)點,所以L1要盡可能地靠近PH腳。另外,PH腳連接在一起的區(qū)域要盡可能小以防止過多的電容耦合。從圖中可以看到,PH腳通過C8連接到BOOT腳,布線時C8要盡可能靠近IC,使連線盡可能短。輸出濾波電容C9連接在VOUT和PGND間,其輸出端、L1的輸出端、PH腳和PGND腳之間組成的環(huán)路越小越好。

最后要進行布線和敷銅。敷銅時,輸入輸出信號線應(yīng)盡量避免相鄰平行,最好加線間地線,以免發(fā)生反饋耦合;電源和地的導線應(yīng)盡可能用寬線,印制導線的拐彎處一般取圓弧形;盡量避免使用大面積銅箔,必須用大面積銅箔時,最好用柵格狀。

根據(jù)上述原則設(shè)計出的電路經(jīng)實際測試,電源各項指標均符合系統(tǒng)要求。其中,輸出的核心電壓VCCINT為1.5V,電流為6A;輔助電壓VCCAUX為3.3V,電流為250mA;輸出驅(qū)動電壓VCCO為3.3V,電流為5.75A。

FPGA供電模塊的設(shè)計,在選擇方案時,要綜合考慮系統(tǒng)要求、成本、效率、設(shè)計靈活性及封裝等眾多因素,做出全面的折衷考慮,既滿足設(shè)計要求,又降低設(shè)計復(fù)雜度和成本。

電子發(fā)燒友App

電子發(fā)燒友App

評論