FPGA開發基本流程包括:設計輸入、設計仿真、設計綜合、布局布線,它們的連接關系如圖1 所示。

2010-06-10 08:24:15 1687

1687 賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

2013-07-23 09:25:53 19707

19707

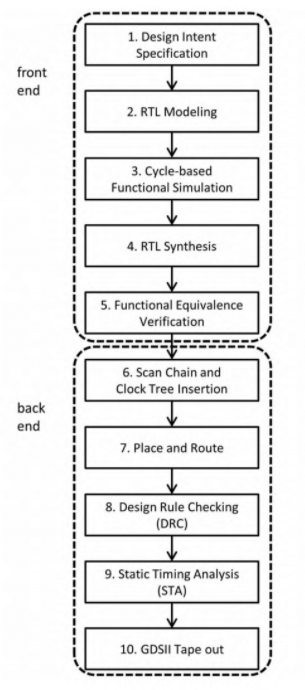

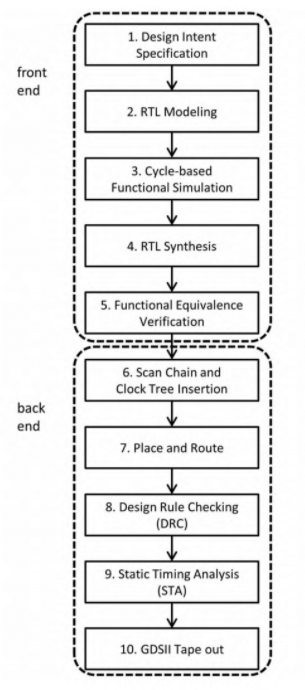

FPGA的前端設計流程類似于ASIC,但后端不同。FPGA的后端部分與ASIC的主要區別在于FPGA的布局和布線。對于ASIC,place and route軟件決定IC的制造方式。

2022-06-20 16:24:12 4730

4730

7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 1276

1276 FPGA設計流程是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的設計流程如上圖所示:包括設計定義、代碼實現、功能仿真、邏輯綜合、前仿真、布局布線、后仿真和板級調試等步驟!

2023-04-04 10:29:51 1281

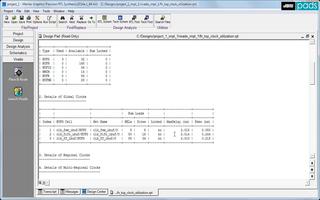

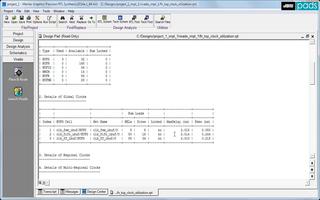

1281 FPGA 如何估算程序所需的資源?是不是要把輸出接到FPGA的PIN上后build,才算是程序所需的資源?因為我有個比較復雜的程序,沒有output到FPGA上,LUT使用為8000+一旦output到FPGA上,LUT使用為8W+.是不是此時的LUT使用量才是程序真正所需的?

2017-01-19 09:09:19

FPGA CPLD同步設計若干問題淺析摘要:針對FPGA/CPLD同步設計過程中一些容易被忽視的問題進行了研究,分析了問題產生的原因、對可靠性的影響,并給出了解決方案。關鍵詞:FPGA/CPLD

2009-04-21 16:42:01

FPGA布線開關的電路設計1 研究方法及其條件假定2 導通晶體管布線開關設計 2.1導通晶體管布線開關尺寸優化2.2 導通晶體管存在的問題及其改進3 三態緩沖布線開關的設計3.1三態緩沖器尺寸優化3.2 三態緩沖布線開關的缺點及其改進4 各種布線開關性能比較及其建議

2011-03-02 09:50:16

)是兩種不同的硬件實現方式。

FPGA是一種可編程邏輯器件,其內部資源可以根據需要進行配置和重新配置。這些資源包括但不限于:

邏輯單元(Logic Cells):這些是FPGA的核心計算資源,可以實現各種

2024-02-22 09:52:22

FPGA入門:基本開發流程概述 本文節選自特權同學的圖書《FPGA/CPLD邊練邊學——快速入門Verilog/VHDL》書中代碼請訪問網盤:http://pan.baidu.com/s

2015-02-09 20:14:21

FPGA入門:基本開發流程概述 在第一章中,已經給出了FPGA/CPLD的基本開發流程圖。這里不妨回顧一下,如圖5.15所示。這個流程圖是一個相對比較高等級的FPGA/CPLD器件開發流程,從項目

2019-01-28 02:29:05

FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般包括功能定義、設計輸入、功能仿真、綜合優化、綜合后仿真、實現與布局布線、時序仿真與驗證、板級仿真

2023-12-31 21:15:31

FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如圖1-10所示,包括電路功能設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真

2021-07-23 09:12:07

對FPGA學習好的資源有哪些?從入門到精通,大家可以分享一起學習呀

2024-01-28 17:00:27

FPGA開發流程(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-31 09:27:38

如圖1.6所示。這個流程圖是一個相對比較高等級的FPGA開發流程,從項目的提上議程開始,設計者需要進行FPGA功能的需求分析,然后進行模塊的劃分,比較復雜和龐大的設計,則會通過模塊劃分把工作交給一個

2019-01-28 04:24:37

的器件無關,也就是說,生成的門電路網表也是一種平臺移植的媒質。FPGA開發—映射我們通過編譯得到一張門級網表之后,與早先ASIC開發流程中在這個門級網表布線后去做掩膜不同,接下來就得考慮如何與我們選擇

2017-11-22 09:34:02

請問FPGA的資源使用如何評估?

2024-02-22 09:55:53

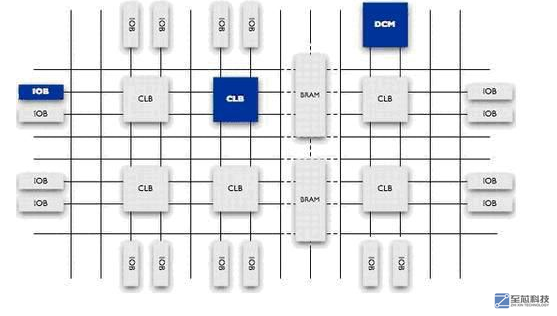

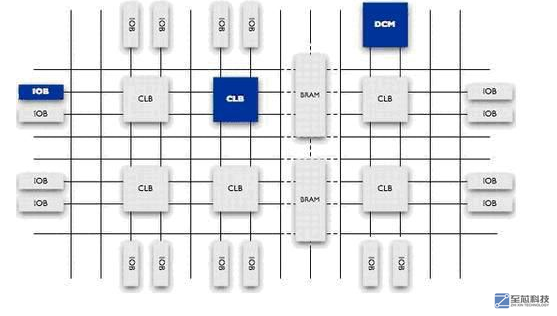

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2019-09-24 11:54:53

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-07-16 15:32:39

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-08-23 10:33:54

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-09-18 11:15:11

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-10-08 14:43:50

FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如圖1-10所示,包括電路功能設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后

2020-11-30 16:22:59

:將邏輯網表配置到具體的FPGA芯片上,需要在速度和面積之間進行選擇 7、時序仿真:后仿真,是將布局布線延時反標注到設計網表中 8、板級仿真與驗證:應用于高速電路,對高速系統信號完整性,電磁干擾等特征進行分析 9、芯片編程與調試:產生位數據流文件,將編程數據下載到FPGA芯片中

2020-12-04 15:28:09

第二章 FPGA 開發流程FPGA 的設計流程就是利用 EDA 開發軟件和編程工具對 FPGA 芯片進行開發的過程。原理圖和HDL(Hardware description language,硬件

2022-02-23 06:23:33

開發流程FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如圖2所示,包括電路設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真、板級

2017-01-10 15:50:15

ASIC的設計流程是怎樣的?FPGA的開發流程又是怎樣的?

2021-11-01 07:08:47

輸入、功能仿真、邏輯綜合、形式驗證、時序/功耗/噪聲分析,布局布線(物理綜合)、版圖驗證。 至于FPGA設計,開發起來更加簡單,結合第三方軟件(像Modelsim和Synplify Pro),兩大

2018-08-16 09:14:32

PROTEL99SE布線的基本流程

2012-08-20 20:38:58

`Xilinx Artix-7 FPGA快速入門、技巧與實例連載6——FPGA開發流程更多資料共享鏈接:https://share.weiyun.com/53UnQas如圖1.32所示,這是一個

2019-04-01 17:50:52

,并把它們分配到FPGA內部的物理位置,通常基于某種先進的算法,如最小分割、模擬退火和一般的受力方向張弛等來完成;布線是指利用自動布線軟件使用布線資源選擇路徑試著完成所有的邏輯連接。因最新的設計實現

2010-01-30 11:22:22

protel布線基本流程PCB打樣找華強 http://www.hqpcb.com 樣板2天出貨

2013-04-05 10:09:12

protel布線基本流程PCB打樣找華強 http://www.hqpcb.com 樣板2天出貨

2013-04-05 10:11:23

前言FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元(IOB)基本可編程邏輯單元(configurable logic block,CLB) 完整的時鐘管理嵌入塊式RAM豐富的布線資源內嵌

2021-07-26 06:54:01

,此時只受限于芯片內塊RAM 的數量,而不再受上面兩條原則約束。5. 豐富的布線資源布線資源連通 FPGA 內部的所有單元,而連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。FPGA 芯片內部

2012-03-08 11:03:49

1.XILINX ISE傳統FPGA設計流程利用XilinxISE軟件開發FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實現、布線后仿真與驗證和下班調試等步驟。如下圖所示。1)電路設計

2021-05-27 09:28:40

,其實這個階段也應該包括第二個階段的布局布線和時序驗證,因為這兩個步驟都是和FPGA器件緊密相關的。我們這么粗略的三個階段劃分并沒有把FPGA整個設計流程完全的孤立開來,恰恰相反,從我們的階段劃分中,我們也看到FPGA設計的各個環節是緊密銜接、相互影響的。 圖1.10 簡化的FPGA開發流程

2016-07-13 17:25:34

NoC 去替代傳統的邏輯去做高速數據傳輸和數據總線管理。· 增加了 FPGA 的布線資源,對于資源占用很高的設計有效地降低布局布線擁塞的風險。· 實現真正的模塊化設計,減小 FPGA 設計人員調試

2020-09-07 15:25:33

器件燒錄和板級調試外,其實這個階段也應該包括第二個階段的布局布線和時序驗證,因為這兩個步驟都是和FPGA器件緊密相關的。我們這么粗略的三個階段劃分并沒有把FPGA整個設計流程完全的孤立開來,恰恰相反

2017-10-12 21:02:44

前言 本部門所承擔的FPGA設計任務主要是兩方面的作用:系統的原型實現和ASIC的原型驗證。編寫本流程的目的是:l在于規范整個設計流程,實現開發的合理性、一致性、高效性。l形成風格良好和完整的文檔

2017-12-08 14:47:15

華為FPGA設計流程指南本部門所承擔的FPGA設計任務主要是兩方面的作用:系統的原型實現和ASIC的原型驗證。編寫本流程的目的是:l在于規范整個設計流程,實現開發的合理性、一致性、高效性。l形成

2017-12-18 10:45:03

,FIR消耗內存較大,這樣會消耗大部分的FPGA邏輯資源,會導致較大系統的資源不夠,因此需要設計更好的數據流結構和算法來處理這個問題。這將是筆者以后需要繼續研究學習的。

2019-06-06 05:00:39

的布線資源,對于資源占用很高的設計有效地降低布局布線擁塞的風險。實現真正的模塊化設計,減小FPGA設計人員調試的工作量。本文用了一個具體的FPGA設計案例,來體現上面提到的NoC在FPGA設計中的幾項

2020-10-20 09:54:00

很完善的protel99se布線流程

2012-12-21 13:32:34

請問各位學友,站內有沒有FPGA視頻學習資源,,以及下載quartus具體指南,,,謝謝

2015-08-03 16:11:02

用PROTEL99SE布線的基本流程

2012-08-20 19:42:05

用PROTEL99SE布線的基本流程

2013-03-17 22:41:13

1.XILINX ISE傳統FPGA設計流程利用XilinxISE軟件開發FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實現、布線后仿真與驗證和下班調試等步驟。如下圖所示。1)電路設計

2019-05-03 08:00:00

1.XILINX ISE傳統FPGA設計流程利用XilinxISE軟件開發FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實現、布線后仿真與驗證和下班調試等步驟。如下圖所示。1)電路設計

2021-06-24 08:00:01

用PROTEL99SE布線的基本流程

2006-03-12 01:13:33 0

0 Protel 布線流程

2006-05-28 01:18:49 0

0 無線資源管理流程

6.4.1 RRC連接建立流程UE處于空閑模式下,當UE的非接入層請求建立信令連接時,UE將發起R

2009-10-12 19:43:42 2964

2964 Mentor Graphics的FPGA Advantage是享譽業界,具有FPGA設計黃金組合的全流程設計工具。本次課程將使用戶體驗FPGA Advantage如何最大化地加速設計的實現以及復用。同時掌握如何利用FPGA Advantage快速實現設計從創建、理解、仿真驗證、綜合以及布局布線的全過

2011-03-15 13:39:56 97

97 Alter FPGA的設計流程以及DSP設計.

2012-03-16 15:52:07 127

127 本文簡要的分析FPGA芯片中豐富的布線資源 。FPGA芯片內部有著豐富的布線資源,根據工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。

2012-12-17 17:28:41 3491

3491 用PROTEL99SE布線的基本流程。

2015-12-25 10:43:29 0

0 FPGA開發流程,好東西,喜歡的朋友可以下載來學習。

2016-01-18 15:17:27 32

32 FPGA的學習流程,有需要的朋友下來看看

2016-05-10 10:46:40 22

22 FPGA設計的流程,步驟,選型,仿真,軟硬件設計,調試流程。

2016-05-11 14:33:02 29

29 電子專業單片機相關知識學習教材資料——FPGA片內資源設計指導

2016-08-23 15:55:35 0

0 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 布線資源連通FPGA內部的所有單元,而連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。FPGA芯片內部有著豐富的布線資源,根據工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。第一類

2017-12-05 11:48:44 8

8 1. FPGA 開發流程: 電路設計與設計輸入 ;仿真驗證:利用Xilinx集成的仿真工具足矣 ;邏輯綜合:利用XST(Xilinx Synthesis Tool)工具 ;布局布線:利用Xilinx

2018-01-12 03:59:48 10000

10000 不斷 從賽靈思FPGA設計流程看懂FPGA設計 1.XILINX ISE傳統FPGA設計流程 利用XilinxISE軟件開發FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合

2018-02-20 20:32:00 15820

15820

(ASIC型)模塊。如圖所示,FPGA芯片主要由7部分組成,分別為:可編程輸入輸出單元(IOB)、基本可編程邏輯單元(CLB)、完整的時鐘管理(DCM)、嵌入式塊RAM、豐富的布線資源、內嵌的底層功能單元和內嵌專用硬件模塊。 1.可編程輸入輸出單元(IOB) 可編程

2018-05-25 14:11:47 8558

8558

本文首先介紹了FPGA發展由來,其次介紹了FPGA的硬件設計技巧及FPGA設計者的5項基本功,最后介紹了FPGA設計流程及工程師FPGA設計心得體會。

2018-05-31 09:35:06 11241

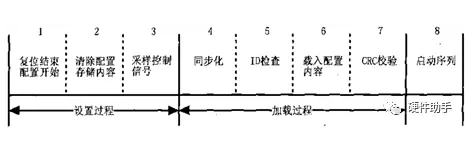

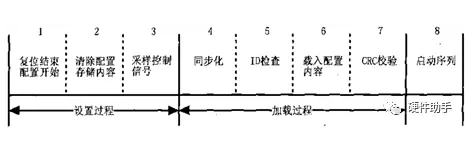

11241 盡管FPGA的配置模式各不相同,但整個配置過程中FPGA的工作流程是一致的,分為三個部分:設置、加載、啟動。

2018-08-01 15:32:54 4736

4736

本文檔的主要內容詳細介紹的是FPGA的設計流程是怎么樣的?FPGA設計流程指南詳細資料免費下載內容包括了:1.基于HDL 的FPGA 設計流程概述2.Verilog HDL 設計3. 邏輯仿真4. 邏輯綜合

2018-10-17 17:50:41 29

29 現在的FPGA里面有很多存儲資源,DSP(數字信號處理)資源,布線通道,I/O資源,當然最根本的還是CLB(Configurable Logic Block)。Xilinx的資源分布采用ASMBL架構。

2018-10-22 11:00:43 5270

5270 在使用FPGA過程中,通常需要對資源做出評估,下面簡單談談如何評估FPGA的資源。

2019-02-15 15:09:05 3580

3580 在FPGA高速AD采集設計中,PCB布線差會產生干擾。今天小編為大家介紹一些布線解決方案。

2019-03-07 14:52:24 6086

6086 在一個環境中實施從合成到塑封式布局和布線以及比特流生成的全套 FPGA 設計。界面中內置了用于運行布局和布線的常用選項,并在與合成結果相同的位置提供所有報告。

2019-05-17 06:06:00 2586

2586

FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現、編程調試等主要步驟。

2019-11-06 15:17:28 2224

2224 FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現、編程調試等主要步驟。

2019-11-20 15:06:28 1545

1545 一般PCB基本設計流程如下:前期準備-》PCB結構設計-》PCB布局-》布線-》布線優化和絲印-》網絡和DRC檢查和結構檢查-》制版。

2019-12-06 15:16:31 2233

2233 布局布線 PlaceRoute 1 布局 我們前面做的那些設計流程得到的LUT門級網表就好比一個購物清單,即LUT門級網表。網表里提供的僅僅是從邏輯關系上一些LUT結構的連接。我們需要將這些LUT

2020-10-25 10:25:31 7659

7659

01 FPGA的設計流程 FPGA是可編程芯片,因此FPGA的設計內容包括硬件設計和軟件設計兩部分。硬件包括FPGA芯片電路、 存儲器、輸入輸出接口電路以及其他設備,軟件即是相應的HDL程序以及

2020-11-12 18:22:28 5791

5791 在使用 FPGA 過程中,通常需要對資源做出評估,下面簡單談談如何評估 FPGA 的資源。 FF 和 LUT 的數目:這個在寫出具體代碼之前,初學者通常沒法估算,但資深 FPGA 工程師會估算

2020-12-28 07:59:00 8

8 區域(Region):每個FPGA器件被分為多個區域,不同的型號的器件區域數量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA

2020-12-09 14:49:03 20

20 FPGA時鐘資源主要有三大類 時鐘管理模、時鐘 IO 、時鐘布線資源。

2020-12-09 18:14:00 13

13 本文檔的主要內容詳細介紹的是FPGA硬件基礎之FPGA時鐘資源的工程文件免費下載。

2020-12-10 15:00:29 15

15 FPGA設計流程指南

2021-11-02 16:29:21 9

9 第二章 FPGA 開發流程FPGA 的設計流程就是利用 EDA 開發軟件和編程工具對 FPGA 芯片進行開發的過程。原理圖和HDL(Hardware description language,硬件

2021-12-29 19:40:15 9

9 (06)FPGA資源評估1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA資源評估5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 關于 FPGA 的 IO資源分析共分為三個系列進行具體闡述,分別為: IO資源:分析FPGA IO資源的電氣特性; IO邏輯資源:分析FPGA的輸入輸出數據寄存器、DDR工作方式、可編程輸入延時

2022-12-13 13:20:06 1099

1099 硬件電路描述方法。其中,運用 HDL 設計方法具有更好的移植性、通用性以及利于模塊劃分的特點,在工作學習中被廣泛使用。典型 FPGA 的開發流程一般如下圖所示, 其包括功能定義/器件選型、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真、板級仿真以及芯片編程與調試等主要步驟。

2023-03-21 10:26:50 2624

2624 FPGA設計的五個主要任務:邏輯綜合、門級映射、整體功能邏輯布局、邏輯資源互連布線,最后生成FPGA的bit流

2023-04-06 09:39:45 691

691 如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量

2023-05-23 15:46:24 481

481

FPGA的設計流程主要包括HDL代碼編寫、RTL綜合、布局布線、靜態時序分析、生成下載文件。下面將逐一介紹各部分。下面是FPGA設計的流程圖。

2023-07-04 12:06:08 795

795

??FPGA 的詳細開發流程就是利用 EDA 開發工具對 FPGA 芯片進行開發的過程,所以 FPGA 芯片開發流程講的并不是芯片的制造流程,區分于 IC 設計制造流程喲(芯片制造流程多麻煩,要好

2023-07-04 14:37:17 2387

2387

FPGA的BRAM和LUT等資源都是有限的,在FPGA開發過程中,可能經常遇到BRAM或者LUT資源不夠用的情況。

2023-08-30 16:12:04 949

949

現代電子設備中,針對復雜的數字電路,FPGA(Field-Programmable Gate Array)是一種非常優秀的可編程邏輯器件。在FPGA的設計過程中,布局布線算法是關鍵步驟之一,其主要

2023-12-20 09:55:13 200

200 電子發燒友網站提供《FPGA的PL端固化流程.pdf》資料免費下載

2024-03-07 14:48:58 0

0 FPGA原型驗證流程是確保FPGA(現場可編程門陣列)設計正確性和功能性的關鍵步驟。它涵蓋了從設計實現到功能驗證的整個過程,是FPGA開發流程中不可或缺的一環。

2024-03-15 15:05:33 97

97

電子發燒友App

電子發燒友App

評論