在汽車電子中廣為采用的微控制器(MCU)正快速面臨時間和成本的壓力。使用MCU的主要優勢一直以來都是‘創造具有高性價比的高階系統整合’。然而,在此一優勢之下,有一些與元件本身相關的潛在成本是超乎于其單價水平的。例如,若選用的元件無法創造所需特性,則必須增加外部邏輯、軟件或其它整合元件。

再者,目前汽車終端市場對于需求的變化屢見不鮮,以至MCU很快就變得不適用;許多具有專門特性以及固定專用界面數量的MCU,經過短暫的評估后即無法滿足市場需求。因此,系統供應商不得不重新設計硬件及編寫相關軟件,在某些情況下,甚至必須更換處理器核心。

MCU的困境

MCU制造商正被迫面對會為整個市場帶來巨大影響的挑戰。MCU是針對應用而設計的元件;因此必須針對個別應用,設計具有不同性能組合的新元件。要以一個單一核心架構來滿足這個廣大市場,制造商必須提供多款MCU系列,提供不同的界面與功能。而市場上大部分的實例顯示,目前的特性組合無法具體滿足客戶的需求,為了能夠量產,必須在一個特定核心架構上改變新界面與功能。

過去的MCU是以舊有技術搭配相對低的制造成本來實現,在過去這是個成功的方法。但現在,為實現更高階的系統整合,廠商不斷采用先進制程技術,開發新的變種MCU所需費用變得相當可觀。由于只有少數客戶會下訂單,因此,為滿足單一客戶需求而生產如此特殊的元件便不再具有商業意義。

因此,新的變種MCU被設計成具備越來越豐富的特性,以吸引整體市場,它正向標準產品發展,不再是針對特殊應用的元件。然而雖然這些標準產品的功能非常強大,但其成本也相對大幅增加,最后變得更難滿足諸如汽車電子等對成本非常敏感的市場。

除了改變引起問題的根源——芯片上的固定功能,我們別無他法。很明顯的,我們需要一種新的設計方法。

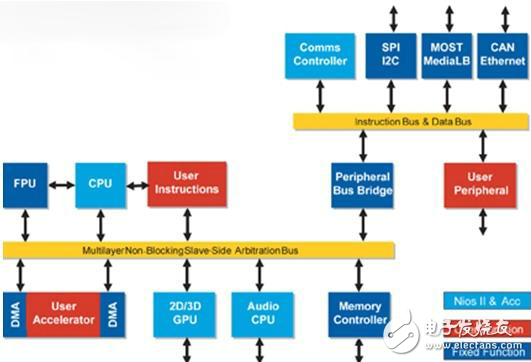

圖1:此汽車資訊娛樂平臺具有多個子系統、可擴展界面以及功能。

靈活的MCU概念

打破這個僵局的方法,是使用FPGA在芯片上實現靈活的功能。FPGA能顯著縮短工程開發時間以及降低多次芯片返工成本,為MCU提供一個強而有力的可行替代方案。例如,采用基于FPGA的方法為汽車音響和導航設備開發一個靈活的繪圖系統,可將開發時間縮短6個月。

與不具備所需特性的MCU不同的是,在設計過程中,可根據需要對FPGA進行編程和改編,以加快原型產生速度及產品上市時間。若需求改變,還可在現場對FPGA進行升級——即使元件已被安裝在產品內。

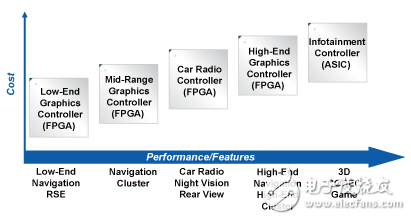

相較于傳統控制器,FPGA已成為汽車繪圖控制器所采用的主要設計方法。雖然為了諸如繪圖等獨立功能所設計的低價FPGA能廣泛地為汽車市場所接受,但為實現可編程能力,仍需在芯片上做出巨額投資,因此擴增的復雜功能也將使得可編程元件價格趨于昂貴。

但隨著目前已能從FPGA無縫轉換為結構化ASIC,一個靈活的微控制器已兼具了價格競爭力,它從一個預定義的大型元件庫與可擴展建構模組中所選取的性能也可以具體滿足客戶需求。

它與傳統MCU的主要區別在于,從原型FPGA到最終MCU的無縫轉換過程。CPU和匯流排架構對靈活的MCU概念來說都是特殊的,且對于特定客戶應用,它們可將所需特定功能及特性映射到設計中。

圖2:FPGA到ASIC整合提升了控制器的性能和特性。

RISC CPU

在Altera設計概念中使用的CPU是軟RISC處理器。然而,與一般情況不同,該處理器并不是建構在一個預先設定好、無法改變的芯片內。相反地,它采用的作法是依據系統架構師/設計工程師,借助可用工具定義的規格自動產生,并與整個電路所需的其余邏輯同時載入FPGA。因此對于特定應用需求,可使用相關開發工具對處理器核心進行參數化。更重要的是,它可根據所需功能以及實現這些所需功能所需的邏輯資源,無縫地實現設計。

在基于Altera的靈活MCU應用中,Nios II嵌入式處理器采用一款帶32位元獨立位址和資料匯流排的標準RISC架構。兩個匯流排都透過獨立快取記憶體執行,且可獨立地連續饋送到匯流排系統。最后,系統架構師決定對程式碼和資料采用個別記憶體或是兩者共用記憶體。任何處理器包含的功能單元都呈現在Nios II嵌入式處理器中,根據不同設定決定它們的特性。例如可選擇硬件乘法器、桶式移位器以及硬件除法器作為選項,同樣地,對指令和資料緩沖記憶體進行精確的處理,其尺寸可不同或是徹底被排除在外。

匯流排架構

傳統上在MCU內一直是采用單匯流排,一個仲裁器用于監控匯流排,以便使匯流排成為一種分散式資源。隨著作為系統中心資源的匯流排迅速成為一項瓶頸,這種安排導致了嚴重的損害。因此,在較新的系統,特別是在許多匯流排平行工作的系統級芯片(SoC)上,已開始采用多層匯流排架構。目前FPGA的匯流排組織結構也以相似的原則進行,不同的是,在其他多層匯流排中所呈現的層數是固定的,但FPGA匯流排建構能讓使用者依需求自由選擇層數。

當考慮到電磁相容性(EMC)和功耗問題時,附加一個有別于整體系統執行功率的周邊模組有時是合理的。舉例而言,以較高速度執行一個記憶體界面,將可縮短存取時間,而系統內其余元件便得以較低的時脈速率運作。另一種方案是可在相對較低時脈便已足夠的地方整合多個模組。

為滿足EMC或功耗要求,采用諸如SOPC Builder等高階系統設計工具可輕易地將這些部分與系統內以很高頻率工作的部分分離。這些工具可自動產生同步這些不同時脈域所需的邏輯,而設計師只需指定在一個特定時脈域中執行哪些模組。

在FPGA內實現MCU

由于汽車MCU系統的復雜性比純繪圖控制器要高得多,所以FPGA大多用于原型邏輯產生。以FPGA產生原型能大幅降低開發風險,因為它能提供全面驗證、韌體開發以及現場測試的功能。除此之外,藉由使用FPGA產生原型,設計師能以‘在系統內’的方式執行元件,并以真實情境的方式運作,以識別出一些模擬時沒被偵測出的潛在設計缺失。

軟件發展在整個開發周期中占了絕大部份。隨著軟件發展要花更長時間及更多資源,原型系統可縮短整個開發周期、發現設計缺失、解決相容性問題、緩解對新硬件功能的需求,以支援無法用軟件有效處理或實現的功能。

用真實系統進行現場測試有助于察覺無法在實驗室發現的系統或元件缺陷。在許多情況,銷售人員為了說服客戶提前下單,擁有一個展示系統是不可或缺的。

而一些在最初規格中沒有的特性和功能也許也將成為必須。無論是因為之前沒發現的缺陷還是必須需增加新功能,FPGA產生的原型都可以快速地被修改,無須一再花費巨額工程成本或忍受漫長制造周期。

靈活MCU概念中的最后步驟是ASIC開發。一旦建構并測試完原型系統,則可著手將設計轉換為結構化ASIC。例如,若采用Altera元件,設計立即被轉換為HardCopy結構化ASIC元件。與其它結構化ASIC不同,若采用該設計流程,則無須重新進行設計合成或花費額外的驗證周期,因這些元件采用的是與其FPGA互補的構件。

采用該結構化ASIC流程提供的快速轉換速度能讓設計師快速簽核FPGA邏輯,因而實現快速、低成本的轉換。

本文小結

下一代汽車電子系統需要高度專用、成本最佳化的元件以滿足市場需求。考慮到先進制程技術開發成本的急劇成長,對傳統MCU針對特殊應用而設計的作法在商業考量上已不再適用。

針對廣泛應用市場所設計的功能豐富型元件也因為過于昂貴而漸被市場淘汰。取而代之的則是靈活的MCU概念,只要將它安置在FPGA中來產生原型,就能提供為特定應用開發恰到好處MCU的程序。設計完成后,甚至在設計過程中可立即進行驗證、軟件發展和現場測試。

為進行量產,FPGA設計被直接映射為一個結構化ASIC而無須重新合成或額外驗證。不只是軟件發展,該方法實現了將硬件定義掌控在汽車電子系統設計師手中。創造了一種與當今任何固定功能MCU相比,均可花費更少時間以及更低成本的應用最佳化車用MCU。

電子發燒友App

電子發燒友App

評論