多道脈沖幅度分析器不僅能自動獲取能譜數據,而且一次測量就能得到整個能譜,因此可大大減少數據采集時間,與此同時,其測量精度也顯著提高。自從20世紀50年代以來,

2010-09-25 09:26:13 2083

2083

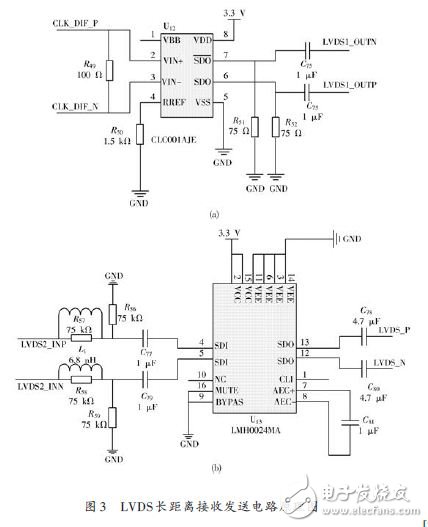

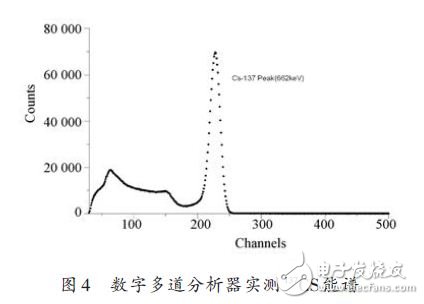

為了研究數字化γ能譜儀,本文提出一種基于FPGA的數字核脈沖分析器硬件設計方案,該方案采用現場可編程邏輯部件(FPGA),完成數字多道脈沖幅度分析儀的硬件設計。用QuartusⅡ軟件在FPGA平臺上完成了數字核脈沖的幅度提取并生成能譜。

2013-11-21 10:57:26 1948

1948

基于FPGA 的數字核脈沖分析器硬件設計方案,該方案采用現場可編程邏輯部件(FPGA),完成數字多道脈沖幅度分析儀的硬件設計。

2015-02-03 09:55:05 1870

1870

1645A數據錯誤分析器操作和維護手冊

2018-12-06 16:19:57

16500C邏輯分析系統的狀態和時序分析器

2019-02-28 13:26:11

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

,整板硬件包括FPGA電路, DDR3電路,外圍接口電路,加上時鐘和控制邏輯等輔助電路,形成一個完整的、一體化的數字系統硬件平臺。能夠快速接入FC-AE網絡,實現光纖總線終端的數據通訊。課程提供項目

2021-11-17 23:12:06

轉成電路連接,從最基本的邏輯門層面上連接成電路(參見數字電路書上那些全加器觸發器什么的)。應該說,雖然看起來像一塊CPU,其實是完全硬件實現的。后來因為寫代碼麻煩,對控制部分比較薄弱,本來跟其他CPU

2020-10-22 11:28:52

如題,小弟最近做一個用FPGA驅動電機的板子,用STM32把FPGA需要發出的脈沖的寬度和個數都計算好,然后用8位的并口,通過一個時鐘上升沿寫進FPGA,在FPGA內部進行運算之后發出脈沖,剛開始

2019-01-28 00:41:02

分析了抖動偏頻激光陀螺信號的解調原理,提出了一種利用數字信號處理技術并采用FPGA實現的抖動解調方法;通過對激光陀螺脈沖計數值高速采樣并采用數字濾波器濾波處理,可以有效消除抖動引起的信號噪聲,得到

2018-08-30 09:21:12

, 節約將近90% 的邏輯資源。 軟核(Soft IP Core) : 軟核在EDA 設計領域指的是綜合之前的寄存器傳輸級(RTL) 模型;具體在FPGA 設計中指的是對電路的硬件語言描述,包括邏輯描述

2018-09-03 11:03:27

數據傳輸效率低,這將嚴重影響產品的性能;而如果采用高速并口,則占用管腳多,硬件成本將會增加。為解決這一痛點,各大芯片公司陸續推出了兼具A核和M核的多核異構處理器,如NXP的i.MX8系列、瑞薩的RZ

2022-11-23 15:09:45

B4620A軟件分析器工具集

2019-03-18 16:53:37

,LED在PIC32芯片上被點亮,這表明它正在運行,但是在MCP2515上沒有LED燈,這是正常的嗎?而且,我發現CAN分析器不接收PIC32發送的測試消息,這表明CAN分析儀和MCP2515

2020-03-26 10:45:52

專家好,

CCS調試程序過程中,需要分析下各函數的執行時間,CCS中提供了性能分析器profile

Q1:性能分析器profile是否只能在Simulator下才能使用,Emulator下沒有這個功能?

Q2:性能分析器profile的使用方法是否有相應的教程參考?

謝謝

NanShan

2018-06-21 19:20:12

我使用的是Microchip CAN總線分析儀,版本2.3軟件。我用最新的固件對這兩個UC進行了編程。我正在運行一個1MIT的CAN網絡,分析器似乎丟失/混淆了消息。請參閱附加屏幕截圖。注意,有時

2018-10-09 11:05:18

OmniBER OTN 2.5 Gb/s通信性能分析器

2019-07-10 16:45:53

OmniBER OTN J7230B 10G通信性能分析器,配置指南

2019-09-03 07:07:28

技術10.4.2 基于FPGA的千兆以太網MAC控制器實現方案10.4.3 Xilinx 千兆以太網MAC IP Core10.5 本章小結第11章時序分析原理以及時序分析器的使用11.1 時序分析的作用

2012-04-24 09:23:33

項目名稱:FPGA上的處理器核原型設計試用計劃:申請理由及項目計劃:本人西安某高校學生,對數字IC感興趣,學習過FPGA與處理器相關知識,用過quartus和vivado,ISE,看過水頭一壽

2017-07-25 18:02:36

國內譜儀技術多年來一直停留在模擬技術水平上,數字化能譜測量技術仍處于方法研究階段。為了滿足不斷增長的高性能能譜儀需求,迫切需要研制一種數字化γ能譜儀。通過核脈沖分析儀顯示在顯示器上的核能譜幫助人們了解核物質的放射性的程度。

2019-07-03 07:35:52

主流四核移動處理器解析

2012-08-20 13:01:36

剛剛接觸antlr詞法分析器只略看了些基本理論知識,關于做實例就完全不懂了,我想知道他需要什么樣的環境和軟件,以及軟件的下載地址.多謝各位了

2014-11-12 16:29:39

分享一個好的工具 單片機C語言流程圖分析器,可以分析整理程序的流程對看懂別人的程序非常管用!

2014-02-08 14:45:59

描述Pico NWT–貧窮無線電愛好者分析儀到了21世紀,你家里還沒有NWT嗎?這個項目的目標是創建一個盡可能簡單的RF分析器。它的設計和調整非常簡單,即使是初學者也可以使用,應用的零件可以在任

2022-08-02 06:11:06

反應堆儀表和控制系統(I&C)的數字化發展方向成為趨勢,反應堆堆外核測量系統的數字化勢在必行。傳統脈沖周期監測裝置通常采用模擬電路設計,但是,周期測量穩定性較差,統計漲落帶來的測量誤差較大

2011-03-04 16:49:54

嗨,我們正在嘗試使用Vivado工具鏈手動路由FPGA,并想知道應該使用什么工具來手動路由Virtex 7 FPGA。還可以在Vivado時序分析器工具中指定溫度和電壓值來估算設計時序嗎?我們將如

2018-10-25 15:20:50

圖形分析器是一個幫助OpenGL ES和Vulkan開發人員通過API級別的分析來充分利用其應用程序的工具。

該工具允許您觀察API調用參數和返回值,并與正在運行的目標應用程序交互,以調查單個API

2023-08-09 06:08:14

描述圖形音頻分析器 16x32

2022-08-24 06:38:03

,減少了硬件資源的占用。該方案在Cyclone II FPGA 芯片EP2C35F484 上實現,占用 20 070 個邏輯單元(少于60% 的資源),系統最高時鐘達到100 MHz 。與傳統的128 位數據路徑設計相比,更方便與處理器進行接口。

2012-08-11 11:53:10

基于FPGA的數字脈沖壓縮技術1.數字脈沖壓縮實現原理2.電路設計2.1APEX2OKE系列FPGA 簡介2.2 基于FPGA 的算法研究及實現 2.3 脈沖壓縮在FPGA 上的實現

2011-03-02 09:41:50

使用。 本文基于快速傅里葉IP核可復用和重配置的特點,實現一種頻域的FPGA數字脈壓處理器,能夠完成正交輸入的可變點LFM信號脈沖壓縮,具有設計靈活,調試方便,可擴展性強的特點。 1 系統功能硬件

2018-11-09 15:53:22

中從電子設計的外圍器件逐漸演變為數字系統的核心。伴隨著半導體工藝技術的進步,FPGA器件的設計技術取得了飛躍發展及突破。分頻器通常用來對某個給定的時鐘頻率進行分頻,以得到所需的時鐘頻率。在設計數字

2019-10-08 10:08:10

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

2019-07-09 07:23:09

Programmable Gate Array,現場可編程門陣列)基于查找表的結構和全硬件并行執行的特性,如何用FPGA 來實現高速FIR 數字濾波器成了近年來數字信號處理領域研究的熱點。目前,全球兩大PLD 器件供應商都提供了加速FPGA 開發的IP(IntelligentProperty,知識產權)核。

2019-09-05 07:21:15

,不同的寄存器在時鐘脈沖的激勵下相互配合完成特定的功能,所以要保證不同的寄存器在同一時刻的時鐘脈沖激勵下協同工作,就需要進行時序分析,通過分析得結果對FPGA進行約束,以保證不同寄存器間的時序要求

2017-02-26 09:42:48

有什么方法可以使用從 cubeIDE 中的 IAR Eclipse 插件生成的 MAP 文件來構建分析器嗎?

2022-12-27 06:26:38

本文利用先進的EDA軟件,用VHDL硬件描述語言采用自頂向下的模塊化設計方法,完成了具有相序自適應功能的雙脈沖數字移相觸發器的IP軟核設計。

2021-04-28 06:39:00

親愛的大家,我使用的是MPLABX3.13的IDE。在分析器中使用PWM模擬器時,我可以在分析器屏幕上獲得PWM波形。但是我不知道如何在分析器窗口進行以下設置:1。如何設置PWM脈沖的NO在X軸上

2019-09-20 08:36:02

多道脈沖幅度分析器結構由那幾部組成基于LPC2134的多道脈沖幅度分析器設計

2021-04-09 06:44:29

現在需要做1nS脈沖發生器,FPGA可以做出來嗎?1,據說FPGA主頻達不到1GHz,那通過PLL或MCMM可以嗎?如果主頻到了,FPGA的普通IO口可以勝任這么高頻嗎?2,可不可以用FPGA內部

2018-03-05 20:03:59

現在需要做1nS脈沖發生器,FPGA可以做出來嗎?1,據說FPGA主頻達不到1GHz,那通過PLL或MCMM可以嗎?如果主頻到了,FPGA的普通IO口可以勝任這么高頻嗎?2,可不可以用FPGA內部

2021-09-10 10:39:13

我無法弄清楚這一點,所以我希望你能提供幫助。在頻譜分析儀上,我可以保存跡線,然后在儀器上調用它,并使用標記進行一些后期分析。我無法破解有關如何使用網絡分析器執行此操作的代碼。任何幫助,將不

2018-09-26 15:09:26

dimond抓取內部信號工具有:插入器,分析器。插入器生產后綴文件為rvl,分析器后綴為rva。FPGA每次斷電后,需要重拔插USB 口才可燒寫(軟件bug)。FPGA每次斷電后,需要找到對應文件夾

2018-12-03 09:00:37

核的分類和特點有哪些?在FPGA設計中的核分為哪幾種?核基FPGA是如何設計的?軟核的設計及使用是什么?

2021-04-14 06:25:39

我可以將EVSPIN32F0251S1與電機分析器一起使用嗎?

2023-01-05 07:14:55

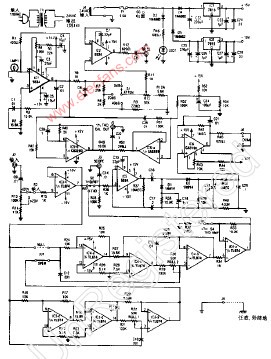

多道脈沖幅度分析器的結構是怎樣設計的?多道脈沖幅度分析器的硬件是如何設計的?怎樣去設計多道脈沖幅度分析器的相關軟件?怎樣對多道脈沖幅度分析器的硬件電路進行仿真測試?

2021-04-14 06:31:11

提出了采用Verilog HDL 設計I2C 總線分析器的方法,該I2C 總線分析器支持三種不同的工作模式:被動、主機和從機模式,并提供了嵌入式系統設計接口。通過硬件總體框架分析,分

2009-08-10 15:32:18 40

40 VPGE(Visual Parser Generation Environment)是一個可視化語法分析器集成開發環境,除了具有良好的界面和強大的調試功能,其LALR(1)分析器的生成速度達到并超過公認的分析器生成速度最快

2009-08-29 10:04:13 16

16 Rosemount分析器基于Raman的激光技術,在對二甲苯純化過程中通過減少給料的變化,幫助工廠達到99.7%的產品純度。本文中的案例講述了如何在生產線中應用Raman分析器

2009-12-08 16:39:33 11

11 HG/T20516-2000自動分析器室設計規定

本規定適用于化工裝置自動分析器室的設計。執行本規定時,尚應符合國家現行的有關標準的規定。

2010-02-24 14:25:51 7

7 轉換到TimeQuest時序分析器教程(電子書)

2010-03-23 16:49:43 0

0 本文介紹一種采用電池供電的ADc和袖珍計算機Pc一1500通過接口電路組成的256道脈沖幅度分析器。其分析范圍為0.1—5V,微分非線性好于±2.5%,耗電約180mw,連續工作24小時道位漂移不

2010-05-19 09:12:18 30

30 摘要:通過對高精度脈沖幅度分析器的電路分析,得出了在使用過程中,采用高精度和低溫系數的電壓基準集成塊,可保證該脈沖幅度分析器比傳統脈沖幅度分析器靈敏度高、穩定

2010-05-25 08:39:59 29

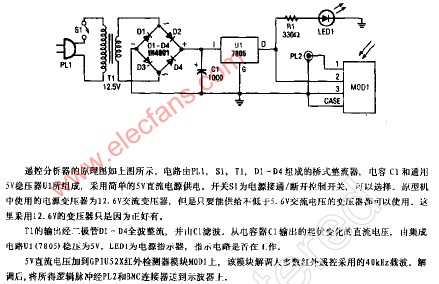

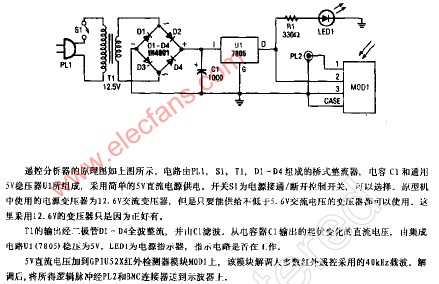

29 遙控分析器

2009-09-18 14:14:38 456

456

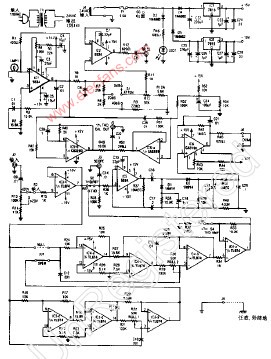

諧波失真分析器

電路包括一個1KHZ的低失真

2009-09-23 14:34:24 757

757

網絡分析器,網絡分析器原理是什么?

網絡分析器

具有發現并解決各種故障特性的硬件或軟件設備

2010-03-22 11:25:21 993

993 協議分析器在WLAN中的應用

協議分析器廣泛應用于有線網絡,成為一類極有用的測試和維護工具。然而,在WLAN領域,這個問題很有可

2010-03-29 17:11:30 483

483 虛擬聲譜分析器軟件詳細介紹 此軟件操作方便快捷

2011-02-11 15:53:54 97

97 摘要:介紹一種以數字信號處理器(DSP)為核心的多道脈沖幅度分析器,它能夠進行核信號的采集\處理以及傳輸,然后經過上位機的處理實現對射線的能量和強度的分析.DSP的采用保證了信號處理的實時性. 關鍵詞:DSP MCA A/D轉換 D/A轉換 探測器 高壓

2011-02-27 13:33:23 34

34 Fortify的靜態代碼分析器(Static Code Analyzer,SCA)是組成Fortify 360的三個分析器之一。SCA工作在開發階段,以用于分析應用程序的源代碼是否存在安全漏洞。這種類型的分析與程序跟蹤分析

2011-04-07 20:32:46 22

22 用大多數FPGA都可以實現一個數字UWB(超寬帶)脈沖發生器。本設計可以創建一個兩倍于FPGA時鐘頻率的脈沖信號(

2011-09-06 11:59:48 5280

5280

多道脈沖幅度分析器不僅能自動獲取能譜數據,而且一次測量就能得到整個能譜,因此可大大減少數據采集時間,與此同時,其測量精度也顯著提高。

2011-10-13 12:01:13 4325

4325

本文將重點介紹“交換端口分析器(SPAN)”的工作原理及配置方法。

2012-02-03 14:09:03 909

909 電子發燒友網: 本文主要分析了多道脈沖幅度分析器忙時間的形成特點,設計出來一套能減小系統忙時間的方案,從而大大地減少由于忙時間造成的脈沖漏計數。同時分析了改進后系統

2012-06-11 08:47:26 37

37 電感儲能型脈沖電源系統的半解析參數分析_丁健民

2017-01-04 16:45:45 0

0 基于LPC1764的多道脈沖幅度分析器的電路設計

2017-09-25 11:45:51 4

4 基于CPLD_ARM的多道脈沖幅度分析器設計

2017-09-25 12:55:06 8

8 核分析能譜測量所用的多道脈沖幅度分析器,在進行模數轉換時需要一定的時間,會使分析器產生漏計數,給測量分析帶來誤差,需要對死時間進行修正。針對這種情況,探討了兩種有效的死時間修正方法。核分析能譜測量

2018-04-09 11:11:45 12

12 本文介紹一種采用電池供電的ADC和袖珍計算機PC-1500通過接口電路組成的256道脈沖幅度分析器。

2018-04-09 11:19:24 9

9 針對當前對多道脈沖幅度分析器的高處理速度、高集成度、友好人機交互的要求,采用三星公司生產的S3C2410芯片設計并實現了一種便攜式的核數據采集系統設計方案。對傳統的多道脈沖幅度分析器進行改進和簡化

2018-04-09 11:51:32 6

6 英特爾?圖形性能分析器的Geometry Viewer快速提示

2018-11-12 06:48:00 2579

2579 Seth為DirectX提供了圖形幀分析器。

了解這款功能強大的分析儀的基本特性和功能。

2018-11-12 06:35:00 1838

1838 Seth為OpenGL提供了圖形幀分析器。

了解這款功能強大的分析儀的基本特性和功能。

2018-11-09 06:25:00 2597

2597 在英特爾?視頻專業分析器中預覽易于使用的GUI:

2018-11-09 06:07:00 1803

1803 Seth提供圖形監視器,系統分析器和HUD。

這些組件構成了英特爾圖形性能分析器中的實時分析工具。

2018-11-07 06:53:00 4770

4770 英特爾?跟蹤分析器中新的性能助理圖表概述。

2018-11-07 06:15:00 2239

2239 開源網絡協議分析器WireShark軟件下載

2021-07-23 09:22:08 14

14 電子發燒友網站提供《圖形音頻分析器開源設計.zip》資料免費下載

2022-08-02 15:18:04 0

0 如您所知,HostMonitor能夠將測試結果記錄到日志文件中。日志分析器是一個可視化日志數據的圖形工具。它解析日志文件的內容并將數據呈現為各種圖表,代表不同的測試統計數據。

2022-08-24 15:19:37 811

811 實時數據分析器用戶手冊 產品規格書.實時數據分析器是,可應用生產現場的數據執行離線分析與實時診斷的邊緣應用程序。

2022-08-26 11:50:34 0

0 LogAnalyzer(日志分析器)是HostMonitor的一個輔助應用程序,它包含在高級主機監視器軟件包中。

2022-09-14 09:56:39 1561

1561 LogAnalyzer(日志分析器)是HostMonitor的一個輔助應用程序,它包含在高級主機監視器軟件包中。

2022-10-13 15:42:31 1232

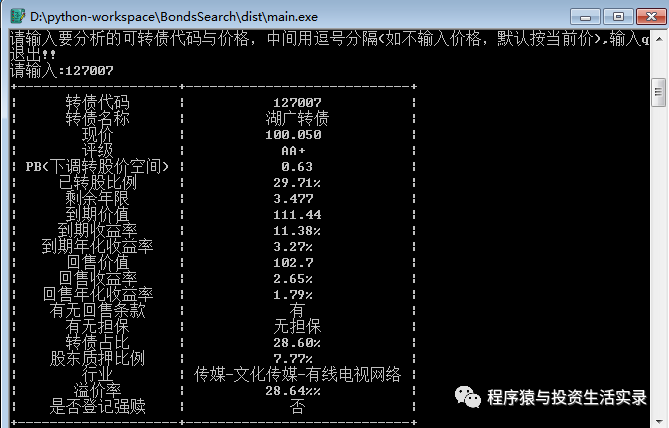

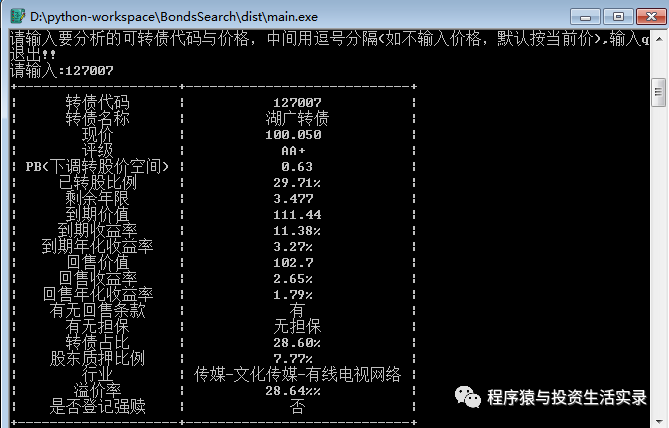

1232 用Python寫個可轉債分析器

2023-02-16 15:13:00 909

909

轉換器分析器用戶指南

2023-04-27 18:48:01 0

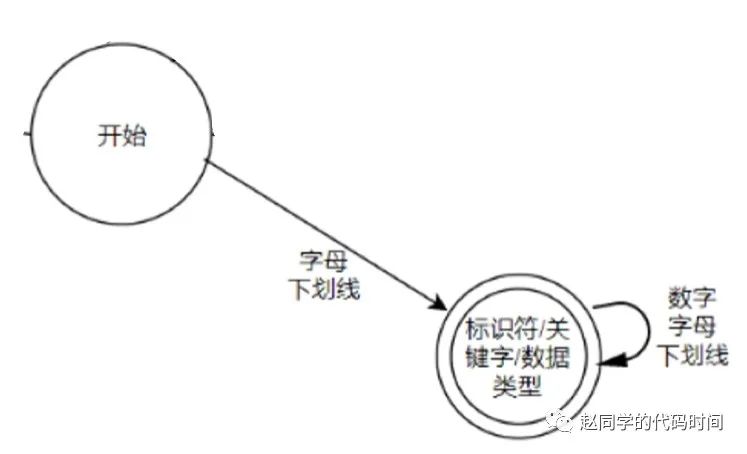

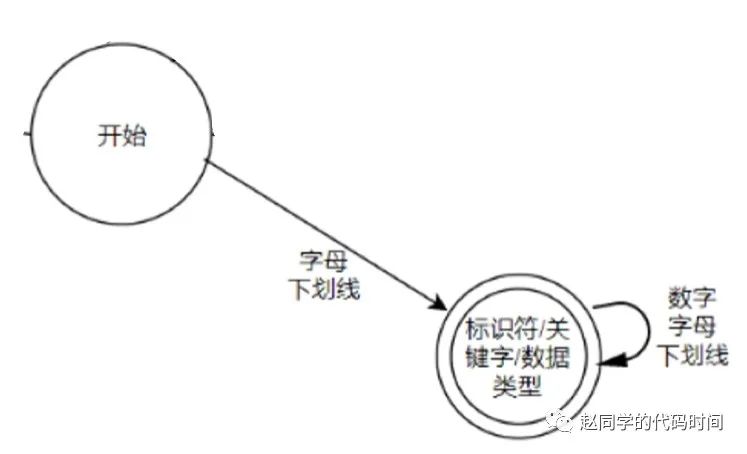

0 在開始手寫詞法分析器之前呢,我們得先準備好一些零件,規劃好將要使用哪些函數,如果函數沒有現成的,那還得自己寫。

2023-05-23 11:20:58 514

514

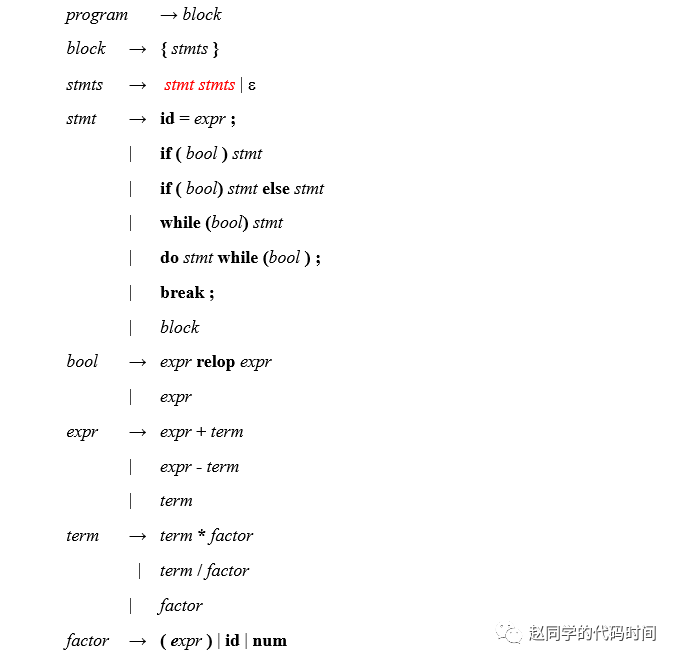

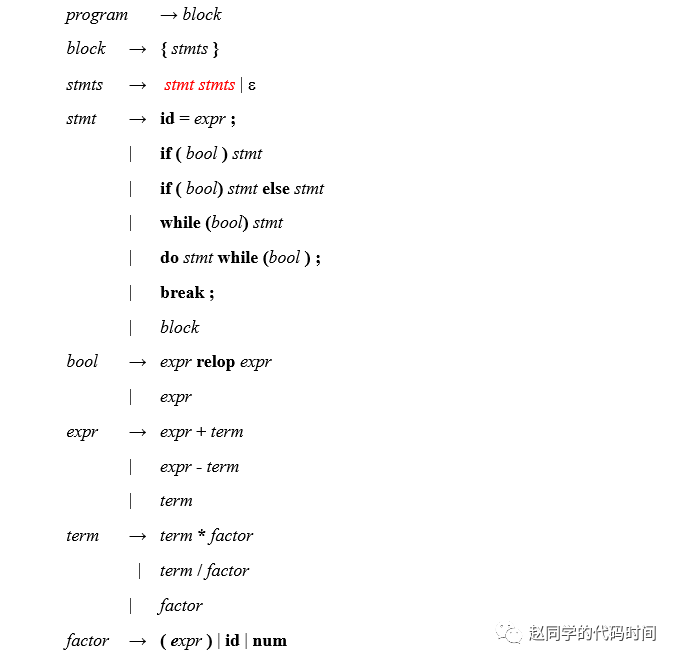

在之前已經通過手寫的方式實現了一個詞法分析器,現在,我將利用之前手寫的詞法分析器,使用遞歸下降的方式,實現一個簡單的語法分析器。

2023-05-23 11:24:02 1451

1451

電子發燒友App

電子發燒友App

評論